- FPGA芯片厂商及关键的开发测试工具

Chip Design

xPUChipDesignfpga开发

以下是结合2025年技术动态整理的。一、FPGA芯片主要厂商及产品系列厂商芯片系列典型特点目标市场AMD/XilinxVersal,Kintex,Artix,Zynq高性能异构计算(AI引擎+FPGA+CPU)数据中心、5G、航空航天Intel(Altera)Stratix,Arria,Agilex,Cyclone高带宽内存集成(HBM),支持CXL协议网络加速、边缘计算LatticeCertus

- (34)FPGA原语设计(BUFGMUX)

宁静致远dream

FPGA就业技能ux开发语言r语言

(34)FPGA原语设计(BUFGMUX)1.1目录1)目录2)FPGA简介3)VerilogHDL简介4)FPGA原语设计(BUFGMUX)5)结语1.2FPGA简介FPGA(FieldProgrammableGateArray)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门

- AUTOSAR汽车电子嵌入式编程精讲300篇-基于 FPGA 的 CAN 控制器设计与验证(续)

格图素书

汽车fpga开发

目录3CAN控制器的设计3.1CAN的模块构成3.2CPI模块3.2.1CPI模块总设计3.2.2位时序设计3.2.3发送模块设计3.2.4接收模块设计3.2.5错误处理模块设计3.2.6过载帧模块设计3.3CAN控制器的操作模式4CAN控制器的验证4.1基于Vivado软件的CAN控制器仿真4.1.1CAN控制器配置及地址打包4.1.2其余端口配置说明4.1.3Testbench编写说明4.1.

- FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)

阿牛的药铺

算法移植部署fpga开发verilog

FPGA小白到项目实战:Verilog+Vivado全流程通关指南(附光学类岗位技能映射)引言:为什么这个FPGA入门路线能帮你快速上岗?本文设计了一条**"Verilog语法→工具链操作→光学项目实战→岗位技能对标"的阶梯式学习路径。不同于泛泛而谈的FPGA教程,我们聚焦光学类产品开发**核心能力(时序接口设计、图像处理算法移植、高速接口应用),通过3个递进式项目(从LED闪烁到图像边缘检测),

- PyTorch & TensorFlow速成复习:从基础语法到模型部署实战(附FPGA移植衔接)

阿牛的药铺

算法移植部署pytorchtensorflowfpga开发

PyTorch&TensorFlow速成复习:从基础语法到模型部署实战(附FPGA移植衔接)引言:为什么算法移植工程师必须掌握框架基础?针对光学类产品算法FPGA移植岗位需求(如可见光/红外图像处理),深度学习框架是算法落地的"桥梁"——既要用PyTorch/TensorFlow验证算法可行性,又要将训练好的模型(如CNN、目标检测)转换为FPGA可部署的格式(ONNX、TFLite)。本文采用"

- FPGA 设计中的 “Create HDL Wrapper“ 和 “Generating Output Products“ 的区别

行者..................

fpga开发

CreateHDLWrapper(创建HDL包装器)目的:为顶层设计模块(通常是BlockDesign/IPIntegrator设计)创建一个HDL包装文件功能:将图形化/框图设计的BlockDesign转换为可综合的HDL代码(Verilog或VHDL)创建一个顶层模块,将所有IP核和连接实例化使用场景:当使用IPIntegrator创建BlockDesign后需要将图形化设计转换为HDL代码以

- STM32与FPGA用FMC进行通讯

weixin_43554366

单片机stm32fpga物联网人工智能

stm32正常按读写SDRAM进行配置,FPGA进行信号采集。FPGA信号采集发现SDWNE是高但H7手册上时序显示是低,造成无法像FPGA模拟的SDRAM无法写入数据FPGA采集信号应该在时钟下降沿,上升沿采集,数据会发生错误。

- Xilinx Vivado开发环境快速导出hdf文件(bat批处理)

XilinxFPGA使用Vivado开发环境创建MicroBlaze软核或ZYNQPS侧SDK逻辑工程时,需要FPGA侧搭建的硬件平台文件,即hdf文件,常规方式是编译完成生成bit流文件后,通过File->Export->ExportHardware菜单来导出,在弹出的菜单再选择要导出的路径和文件名称等,这个过程比较繁琐,通过观察TCL终端窗口:update_compile_order-file

- Xilinx系FPGA学习笔记(三)Vivado的仿真及ILA使用

贾saisai

FPGA学习fpga开发学习笔记

系列文章目录文章目录系列文章目录前言仿真验证(类似modelsim)ILA在线调试工具添加ILAILA的例化ILA的使用前言接着学习vivado的使用方法仿真验证(类似modelsim)首先类似添加.v文件的方法,在File-AddSource中选择Addorcreatesimulationsources或者直接在Sources里面选就行然后就编写testbench,类似之前介绍的modelsim

- 【AXI】读重排序深度

oahrzvq

总线AMBAAXI

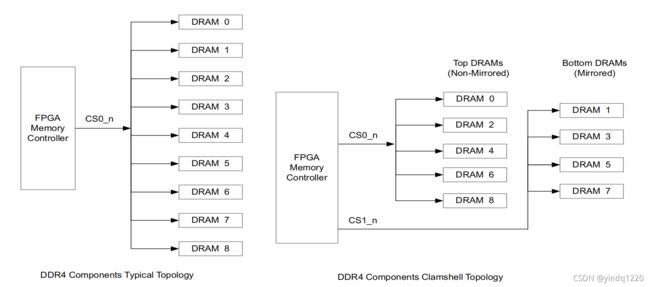

我们以DDR4存储控制器为例,设计一个读重排序深度为3的具体场景,展示从设备如何利用3级队列优化访问效率:基础设定从设备类型:DDR4存储控制器(支持4个存储体Bank0-Bank3)读重排序深度:3(允许同时跟踪3个未完成读请求)访问延迟特征:Bank激活后访问:3周期(低延迟)Bank预充电后访问:7周期(高延迟)主机请求序列(按时间顺序发送):时间点请求标识ARID值目标Bank地址描述T0

- FPGA 47 ,MIG 内存接口生成器深度解析( FPGA 中的 MIG 技术 )

北城笑笑

fpga开发fpga

目录前言一、基础理论1.1MIG介绍1.2结构框架1.2.1主要模块①用户接口层(UserInterfaceLayer)②控制逻辑层(ControLogicLayer)③校准逻辑(CalibrationLogic)④初始化与时序控制(Initialization&TimingControl)⑤物理层接口(PHY–PhysicalLayer)⑥IO引脚驱动(引脚分配与IO配置:Pinout&IOSt

- 基于FPGA的数字密码锁

阿智605

fpga开发notepad++

基于FPGA的数字密码锁顶层文件modulelock(inputclk,//时钟inputrst_n,//复位input[3:0]number_in,//输入inputkey_open1,inputkey_lock1,//inputkey_reset1,outputbeep,//蜂鸣器outputlock_flag,//锁标志位output[3:0]dtube_cs_n,//7段数码管位选信号ou

- 基于FPGA的设计:简易电子密码锁嵌入式实现

程序员杨弋

嵌入式开发fpga开发嵌入式

简介:本文介绍了如何使用FPGA(现场可编程逻辑门阵列)来设计和实现一款简易的电子密码锁。电子密码锁是一种常见的安全访问控制系统,通过输入正确的密码来解锁。嵌入式系统采用FPGA作为核心处理器,结合适当的外设和编程逻辑,能够实现密码输入、验证和控制功能。本文将详细介绍电子密码锁的设计和源代码。设计原理:输入设备:本设计采用数字键盘作为密码输入设备。数字键盘通过FPGA的GPIO(通用输入输出)引脚

- 多通路fpga 通信_FMC与FPGA双口ram通讯

weixin_39796752

多通路fpga通信

硬件环境:ARM+FPGA通过FMC互联,STM32F767和EP4CE15F23I7FMC设置,STM的系统时钟HCLK为216MHz1/*FMCinitializationfunction*/2voidMX_FMC_Init(void)3{4FMC_NORSRAM_TimingTypeDefTiming;56/**PerformtheNOR1memoryinitializationsequen

- [硬件接口]HDMI和DP 区别

DisplayPort和HDMI在FPGA应用场景的实现使用与区别概述DisplayPort(DP)和HDMI是两种主流的数字音视频接口,广泛应用于视频传输场景。在FPGA(现场可编程门阵列)应用中,DP和HDMI常用于视频处理、显示驱动和高带宽数据传输。本文档比较两者在FPGA实现中的使用方式、应用场景及主要区别,并以Markdown格式呈现。1.FPGA实现概述1.1DisplayPort在F

- [FPGA工具]FPGA 文件格式转换工具

S&Z3463

FPGA开发工具fpga开发

SZFPGA文件格式转换工具概述SZFPGA文件格式转换工具(版本V1.0.0)是一款专为FPGA文件格式转换设计的工具,旨在帮助用户将基于Vivado的FPGA文档格式转换为适用于XilinxVivado工具链的格式。本工具支持多种FPGA文档格式的转换,包括BIT转BIN、BIT转MCS、MCS转BIN以及SPIFlash加载等功能。本文档将详细介绍工具的主要功能、使用需求、转换要求、SPI使

- [FPGA AXI IP] AXI Crossbar

AXICrossbarIP详细介绍概述AXICrossbar是属于AXIInterconnectIPSuite的一部分,专为AXI4、AXI3和AXI4-Lite协议设计,提供多个AXI主设备(Master)和从设备(Slave)之间的灵活互联功能。它通过交叉开关(Crossbar)架构实现高效的数据路由,支持多主多从的点对点连接,广泛应用于FPGA和SoC系统设计,特别是在需要复杂AXI总线互联

- [AXI] AXI Interconnect

AXIInterconnectIP详细介绍概述AXIInterconnect专为AXI4、AXI3和AXI4-Lite协议设计,提供多个AXI主设备(Master)和从设备(Slave)之间的灵活互联功能。它通过模块化架构实现高效的数据路由、协议转换、数据宽度转换和时钟域转换,广泛应用于FPGA和SoC系统设计,特别是在需要复杂AXI总线互联的场景,如多核处理器系统、视频处理、网络通信和硬件加速器

- [FPGA Video IP] Video Processing Subsystem

S&Z3463

FPGAVideoIPfpga开发tcp/ip网络协议Video

XilinxVideoProcessingSubsystemIP(PG231)详细介绍概述XilinxLogiCORE™IPVideoProcessingSubsystem(VPSS)(PG231)是一个高度可配置的视频处理模块,设计用于在单一IP核中集成多种视频处理功能,包括缩放(Scaling)、去隔行(Deinterlacing)、颜色空间转换(ColorSpaceConversion,CS

- 基于FPGA的二维FFT实现

廉连曼

基于FPGA的二维FFT实现【下载地址】基于FPGA的二维FFT实现本项目提供了一种基于FPGA的高效二维FFT实现方案,专为数字信号处理和图像处理领域设计。通过并行使用两个一维FFT单元,本方案显著提升了二维FFT变换的计算效率,并基于Xilinx的FFTIP核,确保易于集成到其他FPGA设计中。该方案适用于各类频谱分析场景,尤其适合图像处理系统。经过Verilog编程和Modelsim仿真测试

- FPGA电子系统设计项目实战VHDL语言第2版王振红:深入掌握FPGA设计

姜奇惟Sparkling

FPGA电子系统设计项目实战VHDL语言第2版王振红:深入掌握FPGA设计【下载地址】FPGA电子系统设计项目实战VHDL语言第2版王振红这是一本专注于FPGA电子系统设计的实战指南,适合初学者和进阶开发者。全书共11章,从FPGA设计基础到VHDL语言应用,再到综合电子系统设计实例,内容全面且实用。通过深入浅出的讲解,读者不仅能掌握FPGA设计方法,还能具备实际应用能力。书中详细介绍了Quart

- 基于FPGA的Verilog电子密码锁设计资源文件:为安全而生,智控锁码

基于FPGA的Verilog电子密码锁设计资源文件:为安全而生,智控锁码【下载地址】基于FPGA的Verilog电子密码锁设计资源文件基于FPGA和Verilog语言设计的电子密码锁项目,提供完整的硬件设计原理图、Verilog代码、仿真波形图和硬件描述文档。通过FPGA的可编程特性,实现密码设置、验证及锁定功能,适合学术研究、教学演示或个人兴趣学习。项目文件清晰,包含详细的使用说明,帮助用户快速

- 【FFT】基于FPGA的FFT傅里叶变换和相位计算系统设计

fpga和matlab

★FPGA项目经验板块19:信号发生器fpga开发FFT相位计算

1.软件版本ISE14.7,modeslimSE,10.1c2.系统仿真与分析第1步:信号源的产生主要通过rom将产生的数据保存到rom中,然后,我们再仿真的时候调用即可。这个部分仿真效果如下所示,你给的程序中,这个部分主要有两个数据源,一个是1025,一个是N为1024,我们这里分别将这两个数据量化之后保存到rom中,仿真如下所示:

- 基于FPGA的快速傅里叶变换(FFT)设计在嵌入式系统中的应用

风吹麦很

fpga开发嵌入式

基于FPGA的快速傅里叶变换(FFT)设计在嵌入式系统中的应用快速傅里叶变换(FastFourierTransform,FFT)是一种重要的信号处理算法,在许多领域中都得到广泛的应用,例如通信系统、雷达技术、图像处理等。为了提高FFT的计算性能和实时性,将其设计为硬件加速器常常是一个明智的选择。本文将介绍基于现场可编程门阵列(Field-ProgrammableGateArray,FPGA)的FF

- FPGA电子系统设计项目实战 VHDL语言 第2版 王振红

幸刚磊Thomas

FPGA电子系统设计项目实战VHDL语言第2版王振红【下载地址】FPGA电子系统设计项目实战VHDL语言第2版王振红这是一本专注于FPGA电子系统设计的实战指南,适合初学者和进阶开发者。全书共11章,从FPGA设计基础到VHDL语言应用,再到综合电子系统设计实例,内容全面且实用。通过深入浅出的讲解,读者不仅能掌握FPGA设计方法,还能具备实际应用能力。书中详细介绍了QuartusⅡ工具的使用、VH

- xilinx fpga芯片的结温

hahaha6016

硬件设计fpga开发

xilinxfpga芯片的结温,结温这个含义是啥1.“结温”是半导体器件(比如XilinxFPGA芯片)常用的一个术语,全称是“结温”(JunctionTemperature),指的是芯片内部晶体管结点(PN结)的温度2.结温是芯片内部最关键的温度点,代表晶体管内部结点的实际温度,通常比芯片表面的温度或者散热器的温度要高。3.结温对芯片性能、稳定性和寿命影响很大。如果结温过高,芯片可能会出现性能下

- 存储延时数据,帮你选数据库和缓存架构

呢喃coding

系统架构设计架构

1.理解存储媒介量化延时类别描述延时缓存/内存L1cachereference1ns缓存/内存L2cachereference4ns缓存/内存Mainmemoryreference(DDR4,5-10ns为补充说明)100ns网络传输SendpacketCA->Netherlands->CA150,000,000ns(150ms)磁盘存储HDD(HardDiskDrive)读写1-10ms磁盘存储

- XILINX FPGA如何做时序分析和时序优化?

InnoLink_1024

FPGAVerilogRTL设计fpga开发

时序分析和时序优化是FPGA开发流程中关键步骤,确保设计在目标时钟频率下正确运行,避免时序违例(如建立时间或保持时间不足)。以下以XilinxKintex-7系列FPGA为例,详细介绍时序分析和时序优化的方法、工具、流程及实用技巧,结合Vivado工具链,力求清晰、全面且实用。1.时序分析概述时序分析的目的是验证FPGA设计是否满足时序约束,即信号在规定时间内正确传递,确保逻辑功能和性能。时序分析

- FPGA设计中的数据存储

cycf

FPGA之道fpga开发

文章目录FPGA设计中的数据存储为什么需要数据存储FPGA芯片内部的载体触发器查找表块存储FPGA芯片外部的资源RAM应用场合ROM特征简介实现载体应用场合FIFO特征简介FIFO使用小技巧之冗余法FIFO写接口缓存FIFO读接口缓存“冗余法”总结根据数据流的稳定性与存储操作的容错性,决定采用RAM模式还是FIFO模式STACK特征简介实现载体应用场合SummaryFPGA设计中的数据存储为什么需

- FDMA读写AXI BRAM交互:FPGA高速数据传输的核心技术

芯作者

D1:ZYNQ设计fpga开发

在图像处理系统中,当1080P视频流以每秒60帧的速度传输时,传统DMA每帧会浪费27%的带宽在地址管理上——而FDMA技术能将这些损失降至3%以内现代FPGA系统中,高效数据搬运往往是性能瓶颈的关键所在。当你在手机上流畅播放4K视频、在自动驾驶系统中实时处理激光雷达点云时,背后都依赖于FDMA(FlexibleDirectMemoryAccess)与AXIBRAM的高效交互技术。本文将深入探讨这

- 解线性方程组

qiuwanchi

package gaodai.matrix;

import java.util.ArrayList;

import java.util.List;

import java.util.Scanner;

public class Test {

public static void main(String[] args) {

Scanner scanner = new Sc

- 在mysql内部存储代码

annan211

性能mysql存储过程触发器

在mysql内部存储代码

在mysql内部存储代码,既有优点也有缺点,而且有人倡导有人反对。

先看优点:

1 她在服务器内部执行,离数据最近,另外在服务器上执行还可以节省带宽和网络延迟。

2 这是一种代码重用。可以方便的统一业务规则,保证某些行为的一致性,所以也可以提供一定的安全性。

3 可以简化代码的维护和版本更新。

4 可以帮助提升安全,比如提供更细

- Android使用Asynchronous Http Client完成登录保存cookie的问题

hotsunshine

android

Asynchronous Http Client是android中非常好的异步请求工具

除了异步之外还有很多封装比如json的处理,cookie的处理

引用

Persistent Cookie Storage with PersistentCookieStore

This library also includes a PersistentCookieStore whi

- java面试题

Array_06

java面试

java面试题

第一,谈谈final, finally, finalize的区别。

final-修饰符(关键字)如果一个类被声明为final,意味着它不能再派生出新的子类,不能作为父类被继承。因此一个类不能既被声明为 abstract的,又被声明为final的。将变量或方法声明为final,可以保证它们在使用中不被改变。被声明为final的变量必须在声明时给定初值,而在以后的引用中只能

- 网站加速

oloz

网站加速

前序:本人菜鸟,此文研究总结来源于互联网上的资料,大牛请勿喷!本人虚心学习,多指教.

1、减小网页体积的大小,尽量采用div+css模式,尽量避免复杂的页面结构,能简约就简约。

2、采用Gzip对网页进行压缩;

GZIP最早由Jean-loup Gailly和Mark Adler创建,用于UNⅨ系统的文件压缩。我们在Linux中经常会用到后缀为.gz

- 正确书写单例模式

随意而生

java 设计模式 单例

单例模式算是设计模式中最容易理解,也是最容易手写代码的模式了吧。但是其中的坑却不少,所以也常作为面试题来考。本文主要对几种单例写法的整理,并分析其优缺点。很多都是一些老生常谈的问题,但如果你不知道如何创建一个线程安全的单例,不知道什么是双检锁,那这篇文章可能会帮助到你。

懒汉式,线程不安全

当被问到要实现一个单例模式时,很多人的第一反应是写出如下的代码,包括教科书上也是这样

- 单例模式

香水浓

java

懒汉 调用getInstance方法时实例化

public class Singleton {

private static Singleton instance;

private Singleton() {}

public static synchronized Singleton getInstance() {

if(null == ins

- 安装Apache问题:系统找不到指定的文件 No installed service named "Apache2"

AdyZhang

apachehttp server

安装Apache问题:系统找不到指定的文件 No installed service named "Apache2"

每次到这一步都很小心防它的端口冲突问题,结果,特意留出来的80端口就是不能用,烦。

解决方法确保几处:

1、停止IIS启动

2、把端口80改成其它 (譬如90,800,,,什么数字都好)

3、防火墙(关掉试试)

在运行处输入 cmd 回车,转到apa

- 如何在android 文件选择器中选择多个图片或者视频?

aijuans

android

我的android app有这样的需求,在进行照片和视频上传的时候,需要一次性的从照片/视频库选择多条进行上传

但是android原生态的sdk中,只能一个一个的进行选择和上传。

我想知道是否有其他的android上传库可以解决这个问题,提供一个多选的功能,可以使checkbox之类的,一次选择多个 处理方法

官方的图片选择器(但是不支持所有版本的androi,只支持API Level

- mysql中查询生日提醒的日期相关的sql

baalwolf

mysql

SELECT sysid,user_name,birthday,listid,userhead_50,CONCAT(YEAR(CURDATE()),DATE_FORMAT(birthday,'-%m-%d')),CURDATE(), dayofyear( CONCAT(YEAR(CURDATE()),DATE_FORMAT(birthday,'-%m-%d')))-dayofyear(

- MongoDB索引文件破坏后导致查询错误的问题

BigBird2012

mongodb

问题描述:

MongoDB在非正常情况下关闭时,可能会导致索引文件破坏,造成数据在更新时没有反映到索引上。

解决方案:

使用脚本,重建MongoDB所有表的索引。

var names = db.getCollectionNames();

for( var i in names ){

var name = names[i];

print(name);

- Javascript Promise

bijian1013

JavaScriptPromise

Parse JavaScript SDK现在提供了支持大多数异步方法的兼容jquery的Promises模式,那么这意味着什么呢,读完下文你就了解了。

一.认识Promises

“Promises”代表着在javascript程序里下一个伟大的范式,但是理解他们为什么如此伟大不是件简

- [Zookeeper学习笔记九]Zookeeper源代码分析之Zookeeper构造过程

bit1129

zookeeper

Zookeeper重载了几个构造函数,其中构造者可以提供参数最多,可定制性最多的构造函数是

public ZooKeeper(String connectString, int sessionTimeout, Watcher watcher, long sessionId, byte[] sessionPasswd, boolea

- 【Java命令三】jstack

bit1129

jstack

jstack是用于获得当前运行的Java程序所有的线程的运行情况(thread dump),不同于jmap用于获得memory dump

[hadoop@hadoop sbin]$ jstack

Usage:

jstack [-l] <pid>

(to connect to running process)

jstack -F

- jboss 5.1启停脚本 动静分离部署

ronin47

以前启动jboss,往各种xml配置文件,现只要运行一句脚本即可。start nohup sh /**/run.sh -c servicename -b ip -g clustername -u broatcast jboss.messaging.ServerPeerID=int -Djboss.service.binding.set=p

- UI之如何打磨设计能力?

brotherlamp

UIui教程ui自学ui资料ui视频

在越来越拥挤的初创企业世界里,视觉设计的重要性往往可以与杀手级用户体验比肩。在许多情况下,尤其对于 Web 初创企业而言,这两者都是不可或缺的。前不久我们在《右脑革命:别学编程了,学艺术吧》中也曾发出过重视设计的呼吁。如何才能提高初创企业的设计能力呢?以下是 9 位创始人的体会。

1.找到自己的方式

如果你是设计师,要想提高技能可以去设计博客和展示好设计的网站如D-lists或

- 三色旗算法

bylijinnan

java算法

import java.util.Arrays;

/**

问题:

假设有一条绳子,上面有红、白、蓝三种颜色的旗子,起初绳子上的旗子颜色并没有顺序,

您希望将之分类,并排列为蓝、白、红的顺序,要如何移动次数才会最少,注意您只能在绳

子上进行这个动作,而且一次只能调换两个旗子。

网上的解法大多类似:

在一条绳子上移动,在程式中也就意味只能使用一个阵列,而不使用其它的阵列来

- 警告:No configuration found for the specified action: \'s

chiangfai

configuration

1.index.jsp页面form标签未指定namespace属性。

<!--index.jsp代码-->

<%@taglib prefix="s" uri="/struts-tags"%>

...

<s:form action="submit" method="post"&g

- redis -- hash_max_zipmap_entries设置过大有问题

chenchao051

redishash

使用redis时为了使用hash追求更高的内存使用率,我们一般都用hash结构,并且有时候会把hash_max_zipmap_entries这个值设置的很大,很多资料也推荐设置到1000,默认设置为了512,但是这里有个坑

#define ZIPMAP_BIGLEN 254

#define ZIPMAP_END 255

/* Return th

- select into outfile access deny问题

daizj

mysqltxt导出数据到文件

本文转自:http://hatemysql.com/2010/06/29/select-into-outfile-access-deny%E9%97%AE%E9%A2%98/

为应用建立了rnd的帐号,专门为他们查询线上数据库用的,当然,只有他们上了生产网络以后才能连上数据库,安全方面我们还是很注意的,呵呵。

授权的语句如下:

grant select on armory.* to rn

- phpexcel导出excel表简单入门示例

dcj3sjt126com

PHPExcelphpexcel

<?php

error_reporting(E_ALL);

ini_set('display_errors', TRUE);

ini_set('display_startup_errors', TRUE);

if (PHP_SAPI == 'cli')

die('This example should only be run from a Web Brows

- 美国电影超短200句

dcj3sjt126com

电影

1. I see. 我明白了。2. I quit! 我不干了!3. Let go! 放手!4. Me too. 我也是。5. My god! 天哪!6. No way! 不行!7. Come on. 来吧(赶快)8. Hold on. 等一等。9. I agree。 我同意。10. Not bad. 还不错。11. Not yet. 还没。12. See you. 再见。13. Shut up!

- Java访问远程服务

dyy_gusi

httpclientwebservicegetpost

随着webService的崛起,我们开始中会越来越多的使用到访问远程webService服务。当然对于不同的webService框架一般都有自己的client包供使用,但是如果使用webService框架自己的client包,那么必然需要在自己的代码中引入它的包,如果同时调运了多个不同框架的webService,那么就需要同时引入多个不同的clien

- Maven的settings.xml配置

geeksun

settings.xml

settings.xml是Maven的配置文件,下面解释一下其中的配置含义:

settings.xml存在于两个地方:

1.安装的地方:$M2_HOME/conf/settings.xml

2.用户的目录:${user.home}/.m2/settings.xml

前者又被叫做全局配置,后者被称为用户配置。如果两者都存在,它们的内容将被合并,并且用户范围的settings.xml优先。

- ubuntu的init与系统服务设置

hongtoushizi

ubuntu

转载自:

http://iysm.net/?p=178 init

Init是位于/sbin/init的一个程序,它是在linux下,在系统启动过程中,初始化所有的设备驱动程序和数据结构等之后,由内核启动的一个用户级程序,并由此init程序进而完成系统的启动过程。

ubuntu与传统的linux略有不同,使用upstart完成系统的启动,但表面上仍维持init程序的形式。

运行

- 跟我学Nginx+Lua开发目录贴

jinnianshilongnian

nginxlua

使用Nginx+Lua开发近一年的时间,学习和实践了一些Nginx+Lua开发的架构,为了让更多人使用Nginx+Lua架构开发,利用春节期间总结了一份基本的学习教程,希望对大家有用。也欢迎谈探讨学习一些经验。

目录

第一章 安装Nginx+Lua开发环境

第二章 Nginx+Lua开发入门

第三章 Redis/SSDB+Twemproxy安装与使用

第四章 L

- php位运算符注意事项

home198979

位运算PHP&

$a = $b = $c = 0;

$a & $b = 1;

$b | $c = 1

问a,b,c最终为多少?

当看到这题时,我犯了一个低级错误,误 以为位运算符会改变变量的值。所以得出结果是1 1 0

但是位运算符是不会改变变量的值的,例如:

$a=1;$b=2;

$a&$b;

这样a,b的值不会有任何改变

- Linux shell数组建立和使用技巧

pda158

linux

1.数组定义 [chengmo@centos5 ~]$ a=(1 2 3 4 5) [chengmo@centos5 ~]$ echo $a 1 一对括号表示是数组,数组元素用“空格”符号分割开。

2.数组读取与赋值 得到长度: [chengmo@centos5 ~]$ echo ${#a[@]} 5 用${#数组名[@或

- hotspot源码(JDK7)

ol_beta

javaHotSpotjvm

源码结构图,方便理解:

├─agent Serviceab

- Oracle基本事务和ForAll执行批量DML练习

vipbooks

oraclesql

基本事务的使用:

从账户一的余额中转100到账户二的余额中去,如果账户二不存在或账户一中的余额不足100则整笔交易回滚

select * from account;

-- 创建一张账户表

create table account(

-- 账户ID

id number(3) not null,

-- 账户名称

nam