英飞凌-AURIX-TC3XX-内核架构:AURIX TriCore 1.6P

目录

-

- 英飞凌-AURIX-TC3XX-内核架构:AURIX TriCore 1.6P

-

- 1、AURIX TC1.6P内核简介及特点

- 2、AURIX TC1.6P系统组成及框架

-

- 2.1、AURIX TC1.6P CPU 具体实现图如下:

- 2.2、AURIX TC1.6P CPU 系统框架

- 2.2.1、指令获取单元- Instruction Fetch Unit

- 2.2.2、执行单元-Execution Unit

- 2.2.3、通用寄存器- General Purpose Register File

英飞凌-AURIX-TC3XX-内核架构:AURIX TriCore 1.6P

1、AURIX TC1.6P内核简介及特点

TC3XX 系列属于AURIX™ 2G 系列,AURIX™ 2G 系列系列单片机采用的是TC1.6.E和TC1.6P的核心组合。使用的是32位哈弗架构,将程序指令存储和数据存储分开。具有如下特点:

①、地址范围达到

4GB,分为16段,每段256MB;②、使用的16位和32位指令可减少代码大小,大多数指令能够在1个周期内执行;

③、数据、内存以及

CPU寄存器在单片机中是小端对齐方式;④、具有多种寻址方式:绝对、循环、位反转、长+短、基+偏移量;

⑤、多种指令类型:算术、地址算术、比较、地址比较、逻辑、MAC、移位、协处理器、位逻辑等;

⑥、通用寄存器组(

GPRS)包括16个32位数据寄存器、16个32位地址寄存器以及3个32位状态和程序计数器(PSW/PC/PCXI)。⑦、具有宽内存接口,用于快速上下文切换;

⑧、调试支持(

OCDS):Level 1需要CPS模块支持,Level 3则仅支持带有ED芯片的单片机;⑨、灵活的内存保护系统:具有18个数据存储器及10个代码存储器保护范围,分为6组。

⑩、时间保护系统,允许有时间限制的实时操作。

2、AURIX TC1.6P系统组成及框架

2.1、AURIX TC1.6P CPU 具体实现图如下:

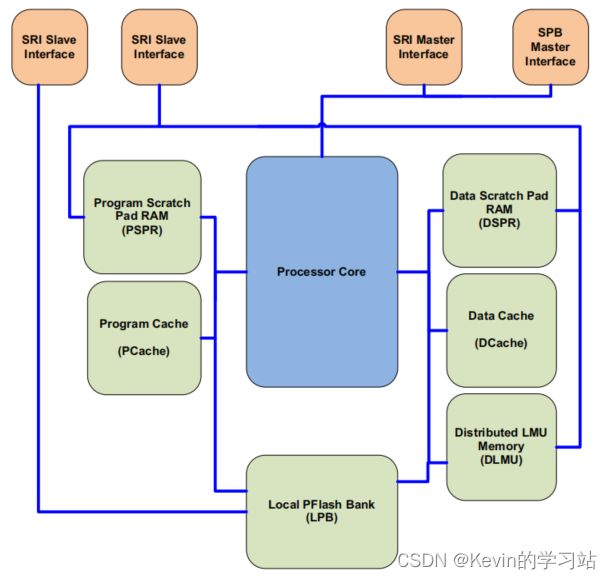

处理器核心连接到以下内存和总线接口:DSPR、PSPR、DCache、PCache、DLMU、LPB、SRI主机、SRI从机(x2)、SPB主机。

分析:

· LMU存储器的一部分(DLMU)分布在处理器之间,以提供对全局SRAM的高性能访问;

· PFlash存储器分布在处理器之间,以提供对本地PFlash库(LPB)的高性能访问;

· 增强的内存保护:保护集数量增加到6个(原为4个)PSW,代码保护范围的数量增加到10(原为8),数据保护范围数量增加到18(原为16);

· 临时保护系统得到扩展,以提供专用的异常计时器;

· 实现了独立的内核重置,可以根据需要独立重置单个内核;

· 存储缓冲区数据合并功能得到扩展,可以将连续的半字合并为字,将连续的字合并为双字;

· 安全保护系统以及扩展得到扩展,可以将连续的半字合并为字,将连续的字合并为双字;

· 安全保护系统已经扩展到涵盖对本地DSPR/PSPR 和 DIMU 的读取和写入访问,以及对LPB的读取访问;

· CPUID已更改为 0x00C0C020。

2.2、AURIX TC1.6P CPU 系统框架

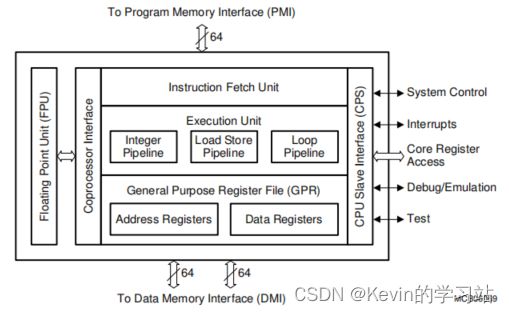

中央处理单元(CPU)包括指令获取单元、执行单元、通用寄存器文件(GPR)、CPU从机接口(CPS)和浮点单元(FPU)。系统框架图如下:

上方为程序存储器接口,具有指令缓存区,通过64位宽度的总线将指令传送到取指单元。取指单元根据指令的特点,分别把指令传送给整型流水线、循环流水线以及转载存储流水线。经过各个流水线处理后的结构分别传送至通用地址寄存器和数据寄存器中。

2.2.1、指令获取单元- Instruction Fetch Unit

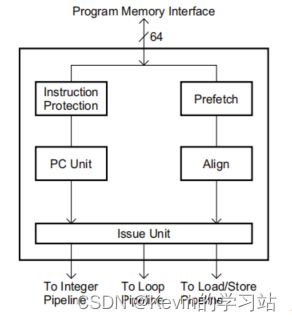

指令获取单元的流程:

①。取值单元从64位宽的程序存储器接口(PMI)传入的指令进行预取指操作并对齐;

②、指令在处理单元的fifo中按预测的程序顺序放置,处理单元fifo最大缓冲6条指令,并将指令分发到不同的流水线中;

③、指令保护单元检查是针对PMI的访问有效性以及从PMI提取的传入指令的完整性;

④、分支单元检测提取的指令的分支条件,根据先前的分支行为预测最可能的执行通道;

⑤、程序计数器单元(PC)负责更新计数器。

2.2.2、执行单元-Execution Unit

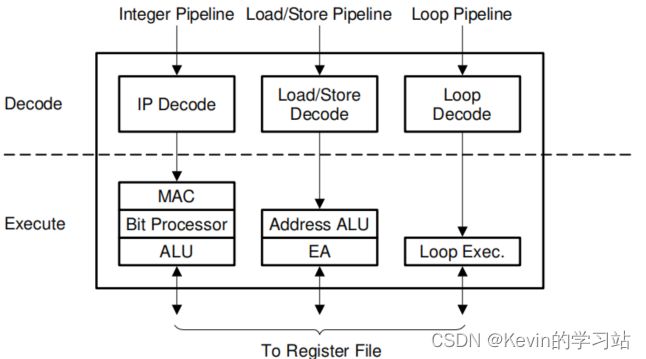

如上图执行单元流程:执行单元包括整数流水线、加载/存储流水线和循环流水线。

①、三条流水线并行运行,允许在一个时钟周期内执行多达三条指令;

②、在执行单元中,所有指令毒药经过一个解码阶段,然后执行与写回操作;

③、通过流水线之间使用转发路径,可将流水线危害降到最低,从而是一条指令的结果在结果可用时立即被下一条指令使用。

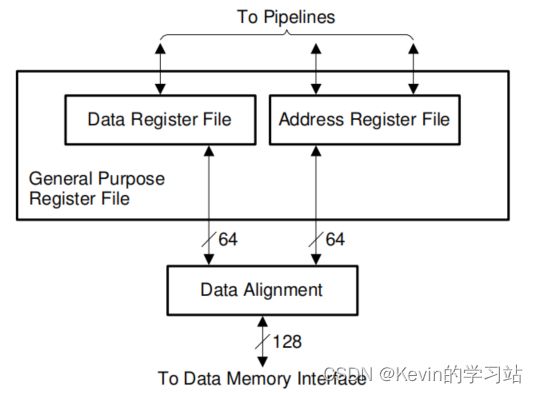

2.2.3、通用寄存器- General Purpose Register File

CPU具有通用寄存器(GPR)文件,该文件分为地址寄存器文件(寄存器A0-A15)和数据寄存器文件(D0-D15)。通过地址寄存器文件控制发布到加载/储存流水线的指令的数据流,通过数据寄存器文件控制向整数流水线发出的指令或从整数流水线发出的指令以及向装载/存储流水线发出的数据加载/存储指令的数据流。