Serdes基础

SerDes是什么?

SerDes是Serializer/Deserializer的缩写,即串行器和解串器,顾名思义是一种将并行数据转换成串行数据发送,将接收的串行数据转换成并行数据的”器件“。对于FPGA工程师来说“串并转换”再熟悉过不过了,只不过SerDes是一种需要数模硬件实现的,用于高速传输的“高级”串并转换器件。至于接口从最初从串口到并口,再回归到串口的历史发展,可以阅读相关的文献,借此可以了解一下系统同步、源同步的技术瓶颈。在未来高带宽、低成本的应用领域会越来越广泛。

高速接口SerDes为实现芯片间信号的有线传输,需要完成数字到模拟的转化,经过通道传输后,再将模拟信号转回数字信号。并保证传输过程保持比较低的误码率。

一、SerDes的整体理解

1.SerDes结构

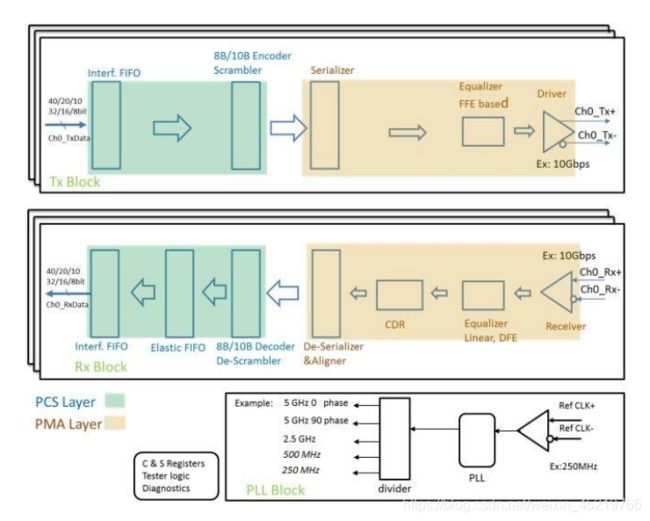

SerDes 的主要构成可以分为三部分,PLL 模块,发送模块 Tx,接收模块 Rx。为了方便维护和测试,还会包括控制和状态寄存器,环回测试,PRBS 测试等功能。

如上图所示蓝色背景子模块为 PCS 层,是标准的可综合 CMOS 数字逻辑,可以硬逻辑实现,也 可以使用 FPGA 软逻辑实现,相对比较容易被理解。褐色背景的子模块是 PMA 层,是数模 混合 CML/CMOS 电路,是理解 SerDes 区别于并行接口的关键。

发送方向(Tx)信号的流向,FPGA 软逻辑(fabric)送过来的并行信号,通过接口 FIFO(Interface FIFO),送给 8B/10B 编码器(8B/10B encoder)或扰码器(scambler),以避 免数据含有过长连零或者连 1。之后送给串行器(Serializer)进行 并->串 转换。串行数据 经过均衡器(equalizer)调理,有驱动器(driver)发送出去。

接收方向(Rx)信号的流向,外部串行信号由线性均衡器(Linear Equalizer)或 DFE (Decision Feedback Equalizer 判决反馈均衡)结构均衡器调理,去除一部分确定性抖动(Deterministic jitter)。CDR 从数据中恢复出采样时钟,经解串器变为对齐的并行信号。8B/10B 解码器(8B/10B decoder)或解扰器(de-scambler)完成解码或者解扰。如果是异步时钟系统(plesio-synchronous system),在用户 FIFO 之前还应该有弹性 FIFO 来补偿频差。

SerDes的整个模型就是经过串化后的数字信号流,经过TX Driver转化为NRZ编码的波形发送到TX输出端,经过信道传输,被RX前端采样和比较,解码得到正确的数据。模型上就是从{dk}到y(t)的过程。

TX发送端实际上就是完成了离散数字信号的连续化

信道对不同频率成分的衰减量是不一致的。而实际信号的频率会比较丰富,这会导致信号有比较严重的码间干扰,因此需要在接收端RX,采用不同的均衡手段,来降低信道的低通频率特性的影响,但为应对更大的信道衰减,在更高的数据率下,也需要在发送端集成均衡方案,这种均衡方式常称为前馈均衡(Feed-Forward Equalization,FFE),利用的是数字信号处理中最常见的有限长度冲激响应滤波器。

在这里涉及到了均衡(Equalization)的概念,接下来我们了解一下均衡是什么?有哪些均衡?以及用来做什么的?

在通信系统的基带或中频部分插入的,能够减少码间干扰, 起到补偿作用的滤波器。分为频域均衡器和时域均衡器。

常见收发器的均衡系统通常由发送端的前馈均衡(Feed Forward Equalizer,FFE),接收端的连续时间线性均衡(Continuous Time Linear Equalizer,CTLE)和判决反馈均衡(Decision Feedback Equalizer,DFE)组成。

8b/10b编码器

8b/10b编码是由IBM于1983年发明的,旨在解决系统互联以及GB以太网传输的问题。 是指将8b的数据通过某种编码规则扩展成10b,保证数据流中的“0”和“1”数量基本一致,通过降低效率来增加传输的数据恢复的可靠性。8b/10b 主要具有以下优点:

1)保证直流(DC)平衡

直流平衡是什么意思呢?由于我们的串行链路中会有交流耦合电容,信号频率越高,阻抗越低,反之频率越低,阻抗越高。当码型是高频的时候,基本上可以不损耗的传输过去,但是当码型为连续“0”或者“1”的情况时,电容的损耗就很大,导致幅度不断降低,带来的严重后果是无法识别到底是“1”还是“0”。因此编码就是为了尽量把低频的码型优化成较高频的码型,从而保证低损耗的传输过去。

8b/10b编码方式总输出位数是10个位,其中“0”与“1”出现的次数总共也仅在三种场合存在,分别为“5个位0与5个位1”、“4个位0与6个位1”、“6个位0与4个位1”。有一个8b/10b编码的技术专用语“不均等性(Disparity)”,其涵义就是指10个位中位0与位1出现次数的差。换句话说,8b/10b编码的“Disparity”就仅有“+2”(4个位0与6个位1)、“+0”(5个位0与5个位1)以及“-2”(6个位0与4个位1)三种状况。

2)有利于提取时钟

时钟恢复是依赖于“电平跳变沿“(后面会介绍),所以平衡”0“和”1“,可以简化了时钟恢复,降低了接收机成本。

3)方便错误检查

8B/10B编码采用冗余方式,将8位的数据和一些特殊字符按照特定的规则编码成10位的数据,根据这些规则,能检测出传输过程中单个和多个比特误码。有关8b/10b编码的编码算法可以进一步查阅相关文献。在SerDes中长常用编码方式除了8b/10b编码外,还有64b/66b编码等;

扰码

扰码是一种将数据重新排列或者进行编码以使其随机化的方法,但是必须能够解扰恢复。我们希望打乱长的连“0”和长的连“1”序列,将数据随机化。扰码产生是通过循环移位寄存器来实现的,而扰码生成多项式决定循环移位寄存器的结构。那么对信号加干扰有什么好处?解决EMI问题

当数据重复传输时,能量就会集中在某一频率上,产生EMI噪声;数据经过加扰后,能把集中的能量分散开,几乎变成白噪声。有利于提取时钟 ,同时又扩展了基带信号频谱,起到加密的效果

发送端均衡器

SerDes 信号从发送芯片到达接收芯片所经过的路径称为信道(channel),包括芯片封装, pcb 走线,过孔,电缆,连接器等元件。从频域看,信道可以简化为一个低通滤波器(LPF) 模型,如果 SerDes 的速率大于信道(channel)的截止频率,就会一定程度上损伤(distort)信号。 均衡器的作用就是补偿信道对信号的损伤。 对于SerDes的发送端均衡,我们要考虑的FIR就必须具有高通特性,以提前补偿一定程度的信道损耗,但考虑到电路实现时(特别是功耗),发送端的均衡器采用 FFE(Feed forward equalizers)结构,发送端的 equalizer 也称作加重器(emphasis)。

加重(Emphasis)分为去加重(de-emphasis)和预加重(pre-emphasis)。De-emphasis 降低差分信号的摆幅(swing)。Pre-emphasis 增加差分信号的摆幅。FPGA 大部分使用 de-emphasis 的方式,加重越强,信号的平均幅度会越小。这个去加重和预加重是两种方法,思想类似实现方式不一样,预加重是增加信号上升沿和下降沿处的幅度,其它地方幅度不变;而去加重是保持信号上升沿和下降沿处的幅度不变,其他地方信号减弱。 发送侧均衡器设计为一个高通滤波器(HPF),大致为信道频响 H(f)的反函数 H-1(f),FFE 的 目标是让到达接收端的信号为一个干净的信号。

FFE实现方式简单,因此广泛地被应用于SerDes系统中。然而对于发送机而言,其输出最大摆幅往往受限于电源电压,因此无法无限增大。这就导致信号的实际摆幅随着FFE均衡强度地提高而减小。因此,在实际设计中,FFE的均衡强度通常小于10dB,从而保证信号的实际摆幅。

如果说发送端在无均衡模式下,只能看做1bit的D/A转化器,那么包含FFE均衡的发送端就是多bit的ADC了。在实际的实现过程中,无论是电压型的SST结构和电流型的CML结构。都可以采用了多份叠加的实际思路

接收端均衡器

1)线形均衡器(Linear Equalizer)

接收端均衡器的目标和发送均衡器是一致的。对于低速(<5Gbps)SerDes,通常采用连续 时间域,线性均衡器实现如尖峰放大器(peaking amplifier), 均衡器对高频分量的增益大于对 低频分量的增益。

2)DFE均衡器(Decision Feedback Equalizer)

对于高速(>5Gbps)SerDes,由于信号的抖动(如 ISI 相关的确定性抖动)可能会超过或接近 一个符号间隔(UI, Unit Interval), 单单使用线性均衡器不再适用。线性均衡器对噪声和信号一 起放大,并没有改善 SNR 或者说 BER。对于高速 SerDes,采用一种称作 DFE (Decision Feedback Equalizer 裁决反馈均衡器)的非线性均衡器。DFE 通过跟踪过去多个 UI 的数据(history bits)来 预测当前 bit 的采样门限。DFE 只对信号放大,不对噪声放大,可以有效改善 SNR。

补充:Unit Interval 单位时间间隔:通常在通信信号的抖动测试中用来表示抖动幅度的单位。表 示一个等步信号的两个相邻的有效瞬时之间的标称时间差

串行器解串器(Serializer/Deserializer)

串行器 Serializer 把并行信号转化为串行信号。Deserializer 把串行信号转化为并行信号。 一般地,并行信号为 8 /10bit 或者 16/20bit 宽度,串行信号为 1bit 宽度(也可以分阶段串行化, 如 8bit->4bit->2bit->equalizer->1bit 以降低 equalizer 的工作频率)。采用扰码(scrambled)的协议 如 SDH/SONET, SMPTE SDI 使用 8/16bit 的并行宽度,采用 8B/10B 编码的协议如 PCIExpress,GbE 使用 10bits/20bits 宽度。

Serializer/Deserializer 的实现采用双沿(DDR)的工作方式,利用面积换速度的策略,降低 了电路中高频率电路的比例,从而降低了电路的噪声。 接收方向除了 Deserializer 之外,一般带有还有对齐功能逻辑(Aligner)。相对 SerDes 发送 端,SerDes 接收端起始工作的时刻是任意的,接收器正确接收的第一个 bit 可能是发送并行 数据的任意 bit 位置。因此需要对齐逻辑来判断从什么 bit 位置开始,以组成正确的并行数 据。对齐逻辑通过在串行数据流中搜索特征码字(Alignment Code)来决定串并转换的起始位置。

时钟数据恢复(CDR)

最开始接触SerDes的是,说“没有单独的时钟线,时钟嵌入在数据流中的”,脑海里第一反应就是在数据中插入一定规则的编码代表时钟的高电平或者低电平,回头一想,那时钟频率不就远低于数据的采集频率了吗?实际上,所谓的“时钟嵌在数据中”的意思,是时钟嵌在数据的跳变沿里。不难理解,极端情况下,假设一串数据流是"1"和"0"交替发送,那这不就是一个时钟了吗。

CDR( Clock and Data Recovery)即时钟和数据的恢复,是SerDes设计中非常重要的环节。CDR常用的技术有基于数字锁相环(PLL)和基于相位插值器两种。当数据经过时,CDR就会捕获数据边沿跳变的频率,如果数据长时间没有跳变,CDR就无法得到精确的训练,CDR采样时刻就会漂移,可能采到比真实数据更多的“0”或“1”。这就是为什么我们在发送的时候采用8b/10b编码或扰码来避免重复出现“0”或“1”,原因之一也在此。

恢复了时钟之后,需要恢复数据。第一步首先要将恢复出来的时钟与数据的边缘进行对齐,然后再将数据给读出来。在硬件原理上,使用PLL电路以及触发器即可。

参考文献

-

SerDes知识详解

-

SerDes 简单介绍

-

高速信号编码之8B/10B

-

8B/10B Encode/Decode详解

-

SERDES与CDR