如何跑通平头哥RISC-V E902的仿真验证

文章目录

- 引言

- 一、源代码结构

- 二、下载源码

- 三、下载工具链

- 四、编译仿真

- 五、查看波形

- 总结

引言

身边很多朋友在跑平头哥的RISC-V开源项目中的case仿真时,或多或少都碰到了一些问题,现在我用E902作为例子,来介绍下仿真流程,并且可能碰到的问题,以及解决方法。

一、源代码结构

E902的开源代码位于:

https://github.com/T-head-Semi/opene902

目录结构如下:

|--E902_RTL_FACRORY/

|--gen_rtl/ ##the source verilog code of E902

|--setup/ ##set the environment variables

|--smart_run/ ##the RTL simulation environment

|--impl/ ##sdc file

|--logical/ ##the SoC demo and test bench to run the simulation

|--setup/ ##GNU tool chain setting

|--tests/ ##include the test suit, linker file, boot code and so on

|--work/ ##the working directory

|--Makefile ##the simulation script

|--doc/ ##the user and integration manual of E902

官方文档里有一个RAEDME.md可供参考。接下来我们按照官方的流程走一遍,其中有些地方需要注意。

二、下载源码

官方文档里有一个RAEDME.md可供参考。接下来我们按照官方的流程走一遍,其中有些地方需要注意。

$ cd E902_RTL_FACTORY

$ source setup/setup.cs

接着进入smart_run目录,这是跑case的目录:

cd ../smart_run

三、下载工具链

在跑仿真之前还需要先下载并设置工具链,最新的版本是2.6.1,工具链的官网地址是:

https://occ.t-head.cn/community/download?id=4090445921563774976

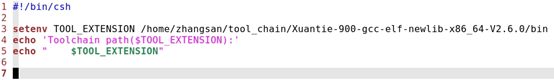

下载解压后,打开smart_run下的example_setup.csh,将TOOL_EXTENSION的值进行修改:

设置好之后,然后source下setup/example_setup.csh,可能会看到如下问题

我们将开头Line1-14的注释删掉,然后重新source就可以了,这样工具链就设置好了

四、编译仿真

接着就可以开始跑仿真了,如果不知道输入什么命令,可以输入make help看一下

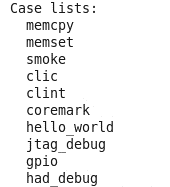

我们先执行make showcase查看一下有哪些case可以跑

如果我现在想跑hello_world这个case,在终端输入如下命令

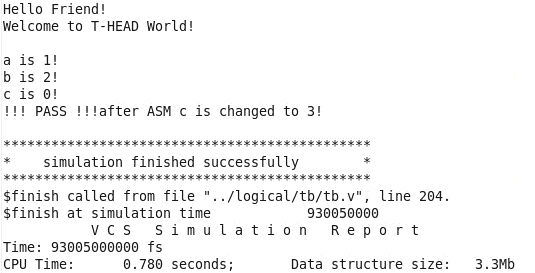

$ make runcase CASE=hello_world SIM=vcs DUMP=on

Makefile中默认使用的仿真工具是,而我用的是vcs,所以需要用SIM=vcs来指定使用vcs进行仿真,同时我希望可以dump波形,所以加了DUMP=on,执行上述命令之后,我们会看到如下结果

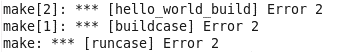

提示没有work目录,需要我们手动mkdir work,新建一个work目录,然后再重新执行上述命令,这个时候我们会看到另外一个问题

重新设置下tests目录下文件的权限

$ chmod 744 -R tests

然后再重新执行仿真命令,恭喜你,这时我们会看到仿真成功了

五、查看波形

仿真完成之后,我想使用verdi查看波形,Makefile中并没有添加verdi相关的设置,因此需要先进行相应的设置

以上两步设置完成之后,就可以在终端输入以下命令来启动Verdi

$ make verdi SIM=vcs

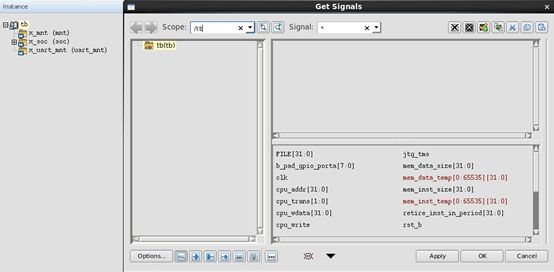

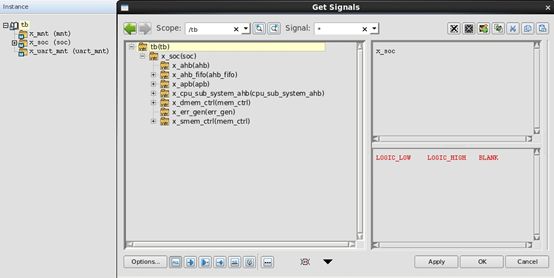

有一些朋友会碰到verdi打开波形之后,tb下hierarchy有问题的情况

如果是verdi2018以下的版本,建议将Makefile中line37的-debug_access换成-debug_all,如果是2018以上版本,则不用管,重新仿真之后,打开verdi就可以看到hierarchy了

总结

由于我使用的仿真工具是vcs,且我希望默认都dump波形,所以我对makefile做了如下的修改,这样在make的时候就不需要指定那么多参数了

关于makefile的知识点,后面我们会再单独介绍。对于上面流程,有什么不清楚的地方,欢迎私信我,更多更好的文章,请关注我的微信公众号 : Verifier_road