AXI总线个人理解笔记-------------(一)接口信号解析

第一次写这么较为复杂的接口介绍,第一是希望将自己学的东西整理一下、加强记忆,第二是希望对入门的同学有所帮助,第三希望有这方面经验的大佬看到有不对的地方能够给予指正。

AXI总线是计算机内部的一种高速总线,主要用于主机(master)和从机(slave)低延迟、高速的数据传输,是由ARM公司设计的为了代替AHB、APB总线而存在的总线标准。AXI可以细分为AXI4、AXI_lite、AXI_stream。

三种总线标准的特点应用为:

AXI4(AXI_full):拥有5个数据通道(注意是通道,每个通道里面都有一系列的信号线),可以进行多次带有地址和数据的突发(burst)传输,满足高性能的存储器映射,常应用于DDR的数据读写。

AXI_lite:也拥有5个数据通道,但是不能进行多次的突发传输,或者说只能进行一次突发传输,可以用于简单的低吞吐率的存储映射,例如内存的配置。

AXI_stream:算是AXI4的简化版,传输高数数据流,没有地址线,能够无次数限制的突发传输,可以应用于FIFO、PCIE、AD/DA的数据传输。

注释:突发(burst)对于新手来说可能理解有点困难,我的理解就是传输一次数据就是一次突发,不管你的数据线或者地址线的线宽/位数是多少。后面会涉及到burst size和burst length会具体讲到。还有在AXI的传输中,数据都是以字节(8bit)的方式进行理解,就是说数据的位宽都是字节的倍数。

本文主要针对AXI4总线进行讲解,因为它的标准里面接口线是最多的、最全的,通过AXI4的学习后去学习其他两个标准就会变得相对的简单。

接口信号解析

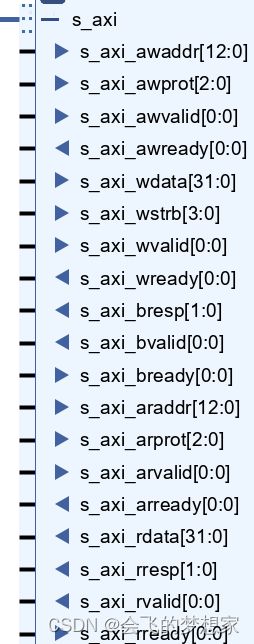

这里我们联系实际先看看在vivado的ip当中AXI4的接口有哪些,直接上图:注意这里的截图是从机接口的截图。

好家伙第一次看到的同学肯定头大有木有?反正我就是。不要方,我们先把这些信号分通道,前面我们提到了AXI4的接口分为5个通道,接下来我们详细讲。这5个通道在图中从上往下分解,分别为AW,W,B,AR,R,也是写地址通道、写数据通道、写响应通道、读地址通道、读数据通道。

读到这儿可能有的同学就疑惑了,为什么有写响应通道没有读响应通道呢?

其实是有的,只是在官方的设计中把读响应通道和读数据通道(W)合并了,也就是上图中的s_axi_rresp[1:0],为什么写操作不合并呢,简单说一下,对于主机来说,写是输出通道,而响应是需要从机产生响应,所以对主机来说是输入通道,一个输入一个输出显然不能合并,而读是输入通道,自然就可以合并了,同时减少了接线数量。

至于为什么不放在读地址通道(AW)而是放在读数据通道(W),大家可以想一想(我的理解是一方面为了不破坏读地址通道的完整性,另一方面是读数据本身就少了一根字节选通信号(strb[*]))。

全局时钟和复位(AXI_aclk/AXI_aresetn)

对了这里必须补充一下除开上面图中的5个通道的接口,还有两个接口AXI_aclk、AXI_aresetn,很好理解:

前者是AXI4的全局时钟,无论地址还是数据都要靠这个时钟来驱动,且都是在时钟的上升沿有效;

后者是全局复位信号,低电平有效,在有效期间像valid和ready这类握手信号都必须保持低电平,即拉低为0。且在赛灵思的官方设计当中要求的复位的方式为:在时钟上升沿检测到复位信号有效时才进行复位,简单来说就是异步复位,同步释放的方式。

接下来我们详细介绍5个通道每个组成信号:

注释:下面的所有input和output都是站在主机的角度,跟上图中的从机接口图是相反的。

(1)写地址通道/AW

awaddr[n:0]:output,写地址信号,在每次突发传输中只发送首地址即可。

awprot[2:0]:output,写安全信号,每一位都代表两种类型,标识着访问方式是否正常安全。

awvalid:output,写有效信号,由数据发送方输出给数据接收方,代表当前地址有效。

awready:input,写准备信号,数据接收方输出给数据发送方,代表接收方准备好接收地址了。

注释:在主机当中来说,当写的时候valid就是主到从是output,ready就是从到主是input;当读的时候主机就是接收方valid就是从到主input,ready就是主到从output。上面的截图是从机(slave)AXI接口,大家不要看错了,从机反过来就行了,只要记住valid是数据发送方产生,ready是接收方产生,后面就不做解释了。

(2)写数据通道/W

wdata[n:0]:output,写数据通道,位宽可以根据需求设置,但是都是8的倍数,也就是一个字节。

wstrb[((n+1)/8)-1:0]:output,字节选通信号,每一位代表wdata中的一个字节,当为1的时候,代表wdata对应字节有效,比如wstrb[N]=1,则代表wdata[(N+1)*8-1:N*8]这个字节有效。

wvalid:output,写有效信号,由数据发送方产生输出给数据接收方,代表当前数据有效。

wready:input,写准备信号,数据接收方产生输出给数据发送方,代表接收方准备好接收数据了。

(3)写响应信号/B

bresp[1:0]:input,写数据响应信号,由数据接收方产生,代表数据的接收是否正常,有4种状态。后面系列会补充。

bvalid:input,响应有效信号,由数据接收方产生输出给数据发送方,代表当前响应有效。

bready:output,响应准备信号,数据发送方产生输出给数据接收方,代表发送方准备好接收响应。

(4)读地址通道/AR

araddr[n:0]:output,读地址信号,在每次突发传输中只发送首地址即可。

arprot[2:0]:output,读安全信号,每一位都代表两种类型,标识着访问方式是否正常安全。

arvalid:output,读有效信号,由数据发送方输出给数据接收方,代表当前地址有效。

arready:input,读准备信号,数据接收方输出给数据发送方,代表接收方准备好接收地址了。

(5)读数据通道/R

rdata[n:0]:input,读数据通道,位宽可以根据需求设置,但是都是8的倍数,也就是一个字节。

rresp[1:0]:input,读数据响应信号,由数据接收方产生,代表数据的接收是否正常。

rvalid:input,读有效信号,由数据发送方产生输出给数据接收方,代表当前数据有效。

rready:output,读准备信号,数据接收方产生输出给数据发送方,代表接收方准备好接收数据了。

-----------------------------------------------------分界线-------------------------------------------------------------------

好了,贪多嚼不烂,今天这一文在这儿就结束了,比较枯燥大部分都是文字输出,没有办法,AXI理论的东西必须啃下来,大家共勉加油!