数字后端设计流程及GDS与OASIS区别

Physical Design Flow in details | ASIC Design Flow

Remark:Team VLSI

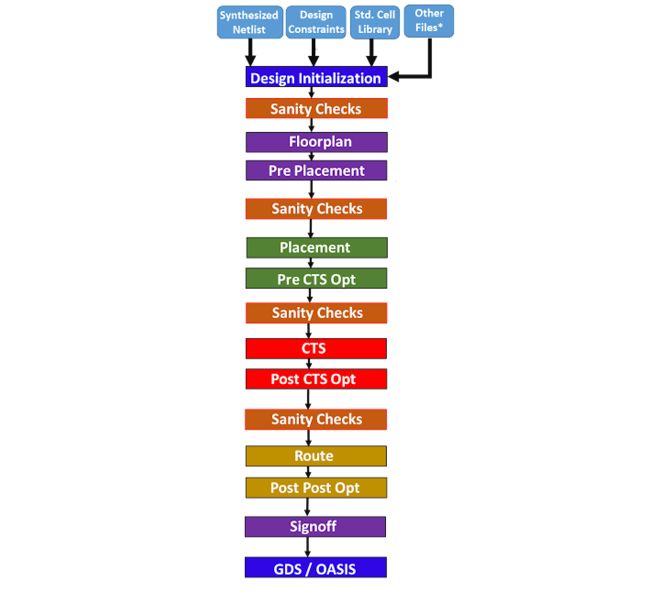

In RTL to GDS flow, Physical Design is an important stage. In physical design, synthesized netlist, design constraints and standard cell library are taken as inputs and converted to a layout (gds file) which should be as per the design rules provided by the foundry. Further, this layout is sent to the foundry for the fabrication of a chip.

将gate-level netlist 转换为layout 的整个过程称为物理设计physical design。在物理设计过程中,设计有各个阶段various stages of design,每个阶段都有各种强制性检查mandatory checks,并涉及到各种分析和验证analysis and verifications。In this article, we will see an overall flow总体流程 of physical design and details of each stage, sanity checks健全性检查, analysis and verifications will be covered in the coming articles.

Here is a basic physical design flow. There are some minor changes in this flow from company to company.

PrePlacement Stage

In Physical design, flow start with some set of input files and do the sanity check健全性检查 first once the design is loded into PnR tool. Sanity checks before floorplan are must in order to make sure that netlist, standard cell library and constraint are correct or not. After that floorplan stage starts where the macro placement is done. A good floorplan of design is a critical thing, it decides the overall quality整体质量 of your design. If floorplan is not well it may lead to several issues in the next stages and it is quite possible that we need to change the floorplan and start again. In general, there are many iterations多次迭代 are required for a physical design engineer to get a quality floorplan.If a block is macro dominant and cell density is high than the floorplan stage is more critical.(如果一个块占主导地位并且单元密度很高,那么布局规划阶段就更为关键。) A good floorplan help to achieve a less congestion拥塞 and good timing. How to do a good floorplan will be discussed in the other article.

Once the floorplan is done, we need to create the powerplanfollowed by adding antenna diodes, welltap cells, endcap cells, decap cells(powerplan后添加). What are these cells and why we need will be discussed in the coming article. Generally, this step is called pre-placement stage. Once the preplacement is done we need to again perform a sanity check before the placement stage.

Placement Stage

After the preplacement, we do the placement where all the standard cells are placed and legalized. There are various steps placement stage which tool performs, these steps will be discussed on a later article. Once the placement is done we need to perform the optimization for better timing and congestions.

CTS Stage

Before the Clock Tree Synthesis (CTS) stage the clock is ideal. CTS is a step in which clock is distributed to all the synchronous elements同步元件 in the design. Before start CTS we need to do sanity checks that the inputs of CTS is proper or not. In CTS there are basically two steps first build a clock tree and then balance the skew偏差 of the clock tree. Quality of CTS is very important in order to meet the timing requirements. After CTS we need to analyze the quality of the clock tree, timing and congestion.

Route Stage

Route stage comes once the Clock tree is built and routed. In routing, there are basically two stage global routing and detail routing. Power nets and Clock nets are already routed, In this stage, we need to route the data nets.

Signoff Stage

Once routing is done we need to insert fillers cells followed by metal fill and then Power signoff, timing signoff, and physical verification. Once all these steps are done in final we stream out the layout in the form of gds or OASIS file which is called tapeout. A detail discussion on each stage will be on coming articles.

OASIS:Switch to the Open Artwork System Interchange Standard (OASIS®) format, which can reduce both file sizes and loading times. The OASIS format has been available for almost 15 years and is accepted by every major foundry. It is also supported by all industry standard EDA tools.The OASIS format has several features that help reduce file size compared to the GDS format.

详细描述可以参考下面这篇文章

OASIS vs GDS