一文彻底搞懂流水线加法器

目录

1.流水线加法器应用场景

2.流水线加法器本质原理(与普通加法器区别)

3.流水线加法器实现

4.流水线加法器代码Verilog代码实现

1.流水线加法器应用场景

首先最重要的是明白我们流水线加法器是什么,我们其实对于流水线其实并不陌生,我们常常可以听到说工厂中存在流水线,他是一种工业上的生产方式,应用场景是生产众多产品的时候,采用流水线方式可以大大提高生产速度。那么我们的流水线加法器也是一样,是应用于多组数据相加,以提高整体计算速度,不让加法器闲置。比如我们计算如下一组数据:

第一组G1

a1 0011_1100 b1 1100_0011

第二组G2

a2 0100_1100 b2 1110_0011

第三组G3

a3 1010_1010 b3 1111_1100

如果仅仅是一组数据相加,那么流水线加法器和普通加法器比起没有什么优势,流水线加法器的优势体现在大量数据相加。

2.流水线加法器本质原理(与普通加法器区别)

为了方便理解,我们后面采用这上述一组包含3组数据的集合来讲解。上述数据如果我们用普通加法器,分成高四位和低四位分别计算,也就是用两个四位加法器。假设高四位和低四位计算分布都各自需要一个周期T,那么我们计算第一组数据需要2T秒(高四位结果需要等低四位的进位结果出来后才能计算得到,第四位耗费T,T秒后高四位开始计算,最后又消耗T,总消耗2T秒)第一组数据计算完毕以后,我们才可以计算第二组数据,同上又一次耗时2T,第三组数据同上2T,总耗时6T秒。

普通加法器时间序列(1)如下:图对于理解非常重要

观察上图我们发现,在我们计算高4位的时侯,低4位加法器是空着不工作的,计算高4位的是,低4位加法器是空着不工作的,这其实会浪费很多费时间。我们想到让高4位和低4位的加法器一直工作。这样可以节省时间,更快地得到所有结果。

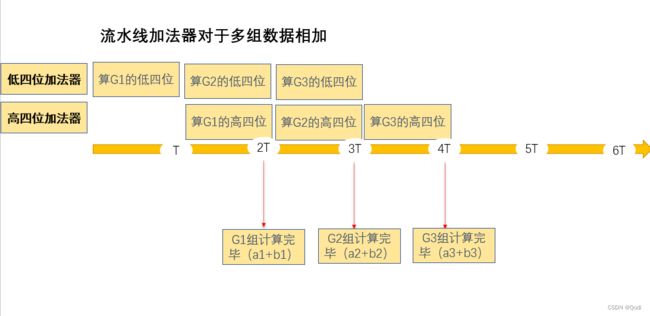

所以想到采用如下流水线加法器时间序列(2):

这时候我们发现每隔Ts后,都会有一组值计算完毕,这样使得总时间压缩到4T秒完成,这仅仅是两级流水,如果更多级可以更明显感受到时间的缩短。

总之就一句话,每一个加法器你都不能给我闲着!!都给我work!work!work!

3.流水线加法器实现

但是理想很丰满,现实很骨感,实际实现起来发现还是不容易的。对于普通加法器级联模式如下

如果采用上述序列(1)的普通加法器模式,我们可以直接利用上面加法器,把第一组数据同时输入到低四位和高四位加法器中,这时候低四位先计算完,它输出整体的低四位,它的输入值在T秒到2T秒不会改变,因而它可以等高四位计算完毕,2T秒的时候,高四位计算完毕,此时低四位和高四位综合得到的是G1组的低四位和高四位组合,也就是G1计算的最终整体值(低四位是在T秒时算出的,高四位是在2T秒算出的)

而如果采用流水线加法器序列(2),就得改装了,因为在T-2T秒的时候,低四位加法器的输入值会改变,观察上面流水线加法器时间序列(2)图,可以发现低四位加法器计算的是G2组的低四位,如果这时候还直接输出,则会在2T秒的时候接收到G2组的低四位,G1组的高四位组合值,这是错误的,我们期望得到G1组的高四位和第四位的组合值,所以在T秒G1组的低四位计算出来后,先存在寄存器中一个周期,在2T秒的时候释放出来,也就是我们的输出同步。改装如下

0-T秒 低四位加法器进行G1组的低四位计算,T秒时把结果存在寄存器一中

T-2T秒 低四位加法器进行G2组的低四位加法器,2T秒时寄存器一结果输出(为G1组低四位),再把G2组第四位结果存入寄存器一

2T-3T秒 低四位加法器进行G3组的低四位加法器,3T秒时寄存器一结果输出(为G1组低四位),再把G3组第四位结果存入寄存器一

再次观察上述流水线加法器时间序列(2)我们发现T秒的时候才把第一组的高位传入高位加法器计算。因而我们需要在高四位的输入加寄存器,使得高四位在寄存器存一个周期再进入高四位加法器计算。也就是我们同时要保证输入同步

0-T秒 0秒时把G1组高四位输入到寄存器二三,T秒时输入高四位加法器运算

T-2T秒 T秒时把G2组高四位输入到寄存器二三,2T秒时输入高四位加法器运算,2T秒时G1组高四位计算完毕输出。

2T-3T秒 2T秒时把G3组高四位输入到寄存器二三,3T秒时输入高四位加法器运算,3T秒时G2组高四位计算完毕输出。

3T-4T秒 4T秒时G3组高四位计算完毕输出。

综上,我们发现对于流水线加法器最重要的是输入输出同步,只有这样,某一个时刻(如T秒),我们输出的才是某一组数据的低四位和高四位和的组合,而不是交叉混乱的,这就是我们需要引入寄存器存放的原因。

4.流水线加法器代码Verilog代码实现