一些关于FPGA的参数(LUT LATCH FF)

目录

1、FPGA中LUT、LATCH、FF的概念

2、LUT、LATCH、FF的相互关系

3、verilog语句与LUT、LATCH、FF的对应关系

4、FPGA的一些参数:LE、ALM、eSRAM、M20K

5、RAM、ROM、FIFO

1、FPGA中LUT、LATCH、FF的概念

LUT(look up table):查找表

本质是一个RAM,将数据事先存储在其中。当输入一个信号后,根据信号所指向的地址进行查表,找出地址对应的内容进行输出。

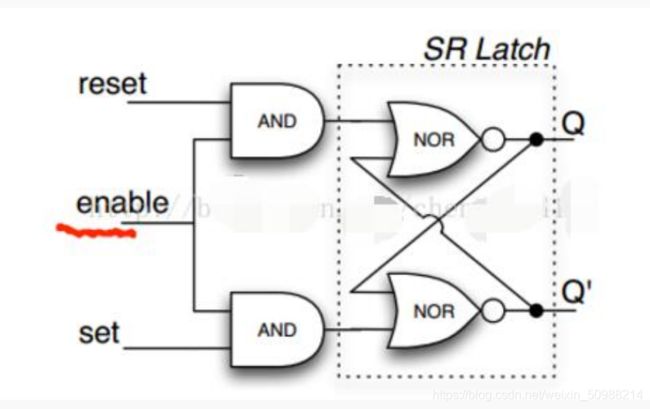

LATCH:一种锁存器。电平触发,非同步控制。在使能信号有效时,LATCH相当于通路(en=1,则 output =input);使能信号无效时,LATCH保存不变。(en=0,则output(当前)=output(之前))

Latch优点:

1、面积比ff小:门电路时构成组合逻辑电路的基础,锁存器和寄存器是时序逻辑电路的基础。构成顺序:晶体管==>门电路==>锁存器==>触发器。

2、latch锁存器速度比ff触发器速度快。

缺点:

1、电平触发,非同步设计,受到布线延迟影响大,容易导致输出产生毛刺

FF(Flip Flop):触发器,时钟沿触发,可以存储1bit的数据,是reg的基本存储单位。

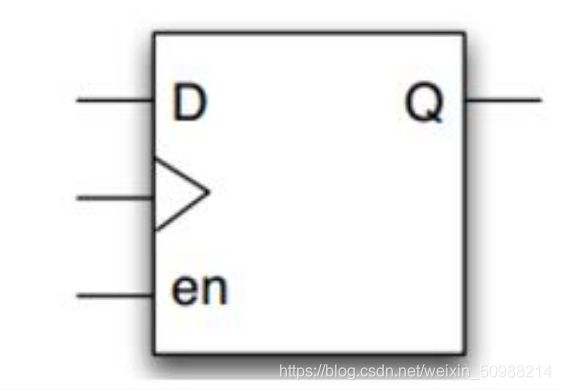

结构图如下:

DFF:D类触发器,是边沿触发,属于时序逻辑。(reg就是由DFF组成,一个8位寄存器,用了8个同步的D触发器)

FF的优点:

1、边沿触发,同步设计,不容易受到毛刺的影响。

2、时序分析简单。

缺点:

1、面积比latch大(锁存器==>寄存器)

2、LUT、LATCH、FF的相互关系

LUT与LATCH共同点:属于组合逻辑(不受时钟沿影响)

不同点:LUT是FPGA最小单元的组成结构,LATCH不是最小组成单元

LATCH和FF不同点:LATCH锁存器可以将输出进行保持不变;触发器FF是指通过时钟触发沿触发的存储单元;由敏感信号(电平,边沿)控制的锁存器就是触发器。

3、verilog语句与LUT、LATCH、FF的对应关系

1、always@(*) 或者 assign 时,综合出的为LUT(不受时钟控制)

2、always@(*)时,若if不完整(无else)或者case不完整(无default)时,会综合出latch,导致不稳定。

3、always@(posedge clk)时,综合出的为reg,即使if或case不完整时,也不会综合出latch

4、FPGA的一些参数:LE、ALM、eSRAM、M20K

4.1逻辑单元LE

用于完成用户逻辑的最小单元,在FPGA内部。(intel叫logic element,xilinx叫logic cell)。一个逻辑单元由以下部件组成:一个四输入的查找表(LookUpTable,LUT),一个可编程的寄存器,一条进位链,一条寄存器级连链。

4.2自适应逻辑模块(ALM)+ALM寄存器

解决LE级联和反馈才能产生具有较多输入函数的指标

4.3可编程的时钟树

4.4eSRAM存储器模块和eSRAM存储器容量

存储程序的位置。SRAM(Static Random-Access Memory)静态随机存取存储器。静态:只要存储器保持通电,存储的数据便可以保持。

4.5 M20K存储器模块+M20K存储器容量

大小为20kbit的memory块

4.6MLAB:

多功能的LAB,即可以做LAB,也可以在需要时作为memory使用。

4.7精度可调DSP+Peak定点性能+Peak浮点性能。

三个模块用于描述FPGA对精度和浮点运算性能的指标。

附:DSP模块有标注精度定点、高精度定点、单精度浮点,三种模式。设计人员利用这三种模式,可以实现从定点到符合 IEEE 754 的双精度浮点运算的各种不同算法。硬浮点处理支持设计人员以相同的定点性能和效率在浮点中实现其算法,且不会对功耗、面积或密度产生任何影响,也不会损失定点特性或功能。

通常来讲浮点数比定点数具有更高的动态表达范围和精度。

5、RAM、ROM、FIFO

5.1 FIFO、RAM、ROM概念

FIFO(First Input First Output):先入先出队列。其中的数据先进先出,先进的数据先读出来。

RAM(Random access memory):随机存取存储器,也叫主存。是与CPU直接交换数据的内部存储器。可随时读写,速度很快,常作为操作系统或其他正在运行中的程序的临时数据存储介质。读出的数据顺序和写入的数据顺序可以不一样,可以向RAM中任意位置写入数据,或者读取任意位置的数据。

ROM(Read-only memory):只读存储器,只能读出不能写入信息。信息一旦写入,断电后信息也不会丢失,因此又称固定存储器。ROM所存的数据通常是装机前写入,装机过程中只能读出,不可像RAM一样快速改写存储内容。ROM存储的数据稳定,断电后数据也不会改变,常用于存储各种固定程序和数据。

5.2 RAM、ROM和FIFO的不同

RAM与ROM最大的不同,RAM有数据的易失性,即一断电数据就丢失,用于暂存程序、数据和中间结果。

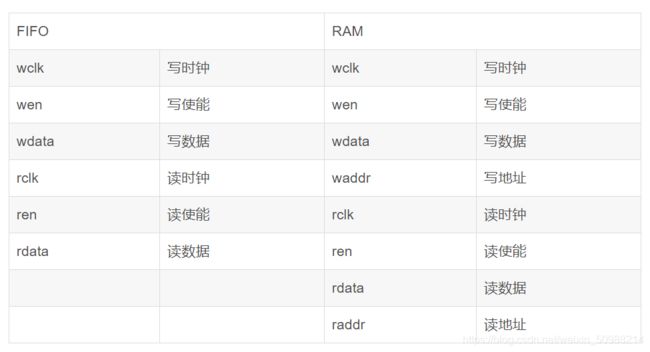

FIFO与RAM信号的不同

FIFO的信号中没有读地址与写地址,因此只能按顺序读写数据。而RAM的信号中含有读写地址,可以读写任意地址。

5.3应用场景

FIFO常用于数据传输通道,用于缓存数据,防止数据丢失。不同速率时钟模块间的数据传输就需要用到异步FIFO

RAM常用于存储指令或是中间的数据,如指令cache和数据cache就是由RAM实现。