- 钟表可以回到起点却已不是昨天

凉小夏

人生的路很长,但是我们只能前进不能后退就像钟表,可以回到起点,却已时过境迁,永远也找不到那个过去的昨天。因我们总是会对过去有着很多留恋不舍和怀念,会时常回头看看走过的脚印,时常想起过去的美好时光,时常想到那些悲伤和不如意。今天的到来时钟不可阻止,历史的记录,原人生最宝贵的不是金钱,不是地位,而是时间。拥有时间就等于拥有一切,因为拥有时间,我们不怕囊中羞涩,因为拥有时间我们不惮创业无门,因为拥有时间

- STM32中的计时与延时

lupinjia

STM32stm32单片机

前言在裸机开发中,延时作为一种规定循环周期的方式经常被使用,其中尤以HAL库官方提供的HAL_Delay为甚。刚入门的小白可能会觉得既然有官方提供的延时函数,而且精度也还挺好,为什么不用呢?实际上HAL_Delay中有不少坑,而这些也只是HAL库中无数坑的其中一些。想从坑里跳出来还是得加强外设原理的学习和理解,切不可只依赖HAL库。除了延时之外,我们在开发中有时也会想要确定某段程序的耗时,这就需要

- (179)时序收敛--->(29)时序收敛二九

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

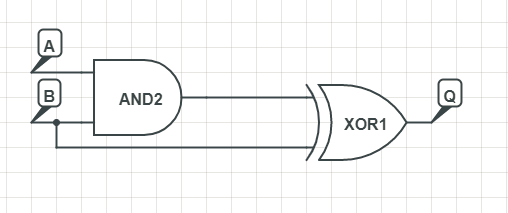

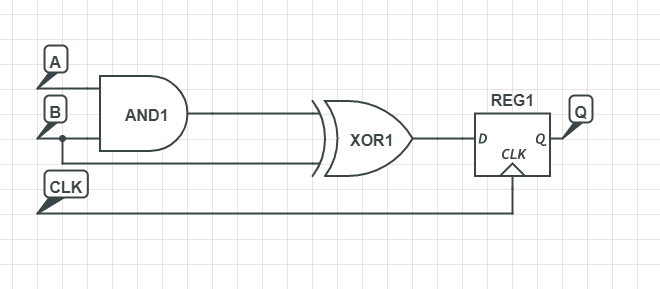

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛二九(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- (180)时序收敛--->(30)时序收敛三十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- (158)时序收敛--->(08)时序收敛八

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛八(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (159)时序收敛--->(09)时序收敛九

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛九(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (160)时序收敛--->(10)时序收敛十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (153)时序收敛--->(03)时序收敛三

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (182)时序收敛--->(32)时序收敛三二

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三二(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- 2023-08-11

Tom梁

当下,文玩之风可谓风靡,喜欢星月菩提的玩友越来多。有许多玩友发私信来问小编“盘玩星月菩提有没有攻略?”。所以今天给大家分享实用的星月菩提盘玩攻略,希望对大家有所帮助。一、挑选方法大家都知道挑选星月菩提的唯一标准就是密度。密度越低,上色越快;密度越高,上色就越慢。但是小编觉得高密籽更适合盘玩,虽然上色慢,但耐盘,生命周期比低密度的要长很多。那么怎么去判断它的密度呢?其实很简单,看星眼的大小、疏密、颜

- iOS内存管理简单理解

烧烤有点辣

什么是引用计数引用计数(ReferenceCount)是一个简单而有效的管理对象生命周期的方式。当我们创建一个新对象的时候,它的引用计数为1,当有一个新的指针指向这个对象时,我们将其引用计数加1,当某个指针不再指向这个对象是,我们将其引用计数减1,当对象的引用计数变为0时,说明这个对象不再被任何指针指向了,这个时候我们就可以将对象销毁,回收内存。由于引用计数简单有效,除了Objective-C和S

- 淘宝618每年活动是啥?今年618淘宝什么活动?

高省APP珊珊

淘宝618密令红包公布密令:【天降红包61666】5.29日20点准时,大额红包不要错过,具体时间同步更新今年的618活动周期和往年差不多,从5月29日开始到6月18日结束,持续20多天,今年的活动热度比往年都要高,而且玩法也更多更新颖,今天小编就给大家讲解一下淘宝天猫618有哪些玩法,基本涵盖了所有的玩法,绝对是最全面的,618活动看这一篇就够了!大家好,我是【高省】最大团队创始人珊珊,至于我为

- 从门氏元素周期表看三皇五帝在关中论

霜叶红似二月花y

世间所有物质,都是由不同元素组成的,科学家们”认识物质初期,所有元素也是多年逐一认识的。著名的俄罗斯化学家门捷列耶夫(DmitriMendeleev1834-1907),在1869年首创的元素周期表,想必大家都很熟悉。他是怎么发现元素周期规律并制成表的?最权威的说法是他自己笔记中所记载的,是他做梦所得。门氏元素周期表这个表开始并不完善,但已经有个雏形了。当时只有已知的63种元素。但门氏预测应该有1

- 51单片机——I2C总线存储器24C02的应用

老侯(Old monkey)

51单片机嵌入式硬件单片机

目标实现功能单片机先向24C02写入256个字节的数据,再从24C02中一次读取2个字节的数据、并在数码管上动态显示,直至读完24C02中256个字节的数据。1.I2C总线简介I2C总线有两根双向的信号线,一根是数据线SDA,另一根是时钟线SCL。I2C总线通过上拉电阻接正电源,因此,当总线空闲时为高电平。2.I2C通信协议起始信号、停止信号由主机发出。在数据传送时,当时钟线为高电平时,数据线上的

- Kubernetes数据持久化

看清所苡看轻

kubernetes(k8s)emptyDirHostPathpvpvckubernetes

在k8s中,Volume(数据卷)存在明确的生命周期(与包含该数据卷的容器组(pod)相同)。因此Volume的生命周期比同一容器组(pod)中任意容器的生命周期要更长,不管容器重启了多少次,数据都被保留下来。当然,如果pod不存在了,数据卷自然退出了。此时,根据pod所使用的数据卷类型不同,数据可能随着数据卷的退出而删除,也可能被真正持久化,并在下次容器组重启时仍然可以使用。从根本上来说,一个数

- Kubernetes的3种数据持久化方式

Seal^_^

【云原生】容器化与编排技术持续集成#Kuberneteskubernetes容器云原生EmptyDir面试HostPath

Kubernetes的3种数据持久化方式1.EmptyDir2.HostPath3.PersistentVolume(PV)TheBegin点点关注,收藏不迷路Kubernetes提供了几种数据持久化方式,以满足不同场景的需求:1.EmptyDir用途:临时数据存储,Pod内容器间共享。特点:生命周期与Pod相同,Pod删除时数据也删除。2.HostPath用途:访问宿主机特定文件或目录。特点:增

- 音视频知识图谱 2022.04

关键帧Keyframe

前些时间,我在知识星球上创建了一个音视频技术社群:关键帧的音视频开发圈,在这里群友们会一起做一些打卡任务。比如:周期性地整理音视频相关的面试题,汇集一份音视频面试题集锦,你可以看看《音视频面试题集锦2022.04》。再比如:循序渐进地归纳总结音视频技术知识,绘制一幅音视频知识图谱。下面是2022.04月知识图谱新增的内容节选:1)图谱路径:**采集/音频采集/声音三要素/响度******主观计量响

- Java面试笔记记录6

今天背八股了吗

java面试笔记

1.Spring是什么?特性?有哪些模块?Spring是一个轻量级、非入侵式的控制反转Ioc和面向切面AOP的框架。特性:1.Ioc和DISpring的核心就是一个大的工厂容器,可以维护所有对象的创建和依赖关系,Spring工厂用于生成Bean,并且管理Bean的生命周期,实现高内聚低耦合的设计理念。2.AOP编程Spring提供面向切面编程,可以方便实现对程序进行权限拦截、运行监控等切面功能。3

- 读书:《精神病学的人际关系理论》-引言-人格理论

家妤

1.基本观点:人际关系。沙利文认为,人的本质是人的社会性,这种社会性表现为人际关系。也就是说,人是人际关系的存在,人只有在人际情境中才能生存和发展。2.人格含义:人际情境的持久模式。沙利文将人格定义为:使人类生活具有特征的周期性人际情境的相对持久的模式。他说“每个人有多少种人际关系,它就有多少种人格。”3.人格动态过程:紧张与能量转化。沙利文认为人类具有趋于心理健康的动力,同时每个人都有减少内心紧

- Github 2024-09-12 Go开源项目日报Top10

老孙正经胡说

githubgolang开源Github趋势分析开源项目PythonGolang

根据GithubTrendings的统计,今日(2024-09-12统计)共有10个项目上榜。根据开发语言中项目的数量,汇总情况如下:开发语言项目数量Go项目10C项目1Terraform:基础设施即代码的开源工具创建周期:3626天开发语言:Go协议类型:OtherStar数量:40393个Fork数量:9397次关注人数:40393人贡献人数:358人OpenIssues数量:1943个Git

- Python和MATLAB及C++信噪比导图(算法模型)

亚图跨际

算法交叉知识Python视频图像修复模数转换信号链噪音频谱计算量化周期性视觉刺激高斯噪声的矩形脉冲心率失常检测算法

要点视频图像修复模数转换中混合信号链噪音测量频谱计算和量化周期性视觉刺激脑电图高斯噪声的矩形脉冲总谐波失真周期图功率谱密度各种心率失常检测算法胶体悬浮液跟踪检测计算交通监控摄像头图像噪音计算Python信噪比信噪比是科学和工程中使用的一种测量方法,用于比较所需信号水平与背景噪声水平。信噪比定义为信号功率与噪声功率之比,通常以分贝表示。高于1:1(大于0dB)的比率表示信号大于噪声。信噪比是影响处理

- Dubbo架构概览:服务注册与发现、远程调用、监控与管理

木南曌

dubbo架构

Dubbo是一个成熟的、高性能的、基于Java的微服务开发框架,它主要用于解决分布式系统中的服务治理问题,包括服务的注册与发现、远程过程调用(RPC)、服务监控与管理等多个关键环节。以下是Dubbo架构概览的详细介绍:服务注册与发现Dubbo的服务注册与发现机制是其核心功能之一,它依赖于注册中心来管理服务的生命周期和定位服务提供者。1.服务提供者(Provider)服务提供者是实际提供服务的节点,

- Xilinx 7系列FPGA架构之器件配置(二)

FPGA技术实战

FPGA器件架构XinxFPGA硬件设计fpga开发

引言:本文我们介绍下7系列FPGA的配置接口,在进行硬件电路图设计时,这也是我们非常关心的内容,本文主要介绍配置模式的选择、配置管脚定义以及如何选择CFGBVS管脚电压及Bank14/15电压。1.概述Xilinx®7系列设备有五个配置接口。每个配置接口对应一个或多个配置模式和总线宽度,如表1所示。有关接口详细的时序信息,可以参阅相应的7系列FPGA数据手册。配置时序主要与FPGA配置时钟管脚CC

- STM32 的 RTC(实时时钟)详解

千千道

STM32stm32物联网单片机

目录一、引言二、RTC概述三、RTC的工作原理1.时钟源2.计数器3.闹钟功能4.备份寄存器四、RTC寄存器1.RTC_TR(TimeRegister,时间寄存器)2.RTC_DR(DateRegister,日期寄存器)3.RTC_SSR(SubsecondRegister,亚秒寄存器)4.RTC_PRER(PrescalerRegister,预分频器寄存器)5.RTC_CR(ControlReg

- Orange Pi编译脚本的分析

点点吃得太多了

linuxlinuxbash

脚本的运行流程/scripts/main.sh变量设置DEST=“${SRC}”/outputREVISION=“2.2.2”DOWNLOAD_MIRROR==“china”NTP_SERVER=“cn.pool.ntp.org”通过网络校准您计算机上的时钟BUILD_ALLCOLUMNS,LINESTTY_X,TTY_YLANGUAGE=“en_US:en”CONSOLE_CHAR=“UTF-8

- Servlet容器的作用、HttpServlet的工作机制流程图

烟雨国度

servlet流程图hive

HttpServletRequest解析过程是否GETPOST其他方法Servlet生命周期init-初始化Servletservice-处理请求destroy-销毁ServletgetMethod返回HTTP方法getRequestURI返回请求URIgetQueryString返回查询字符串getParameter返回特定参数值客户端发送HTTP请求服务器接收请求Web容器创建ServletR

- quartus频率计 时钟设置_FPGA021 基于QuartusⅡ数字频率计的设计与仿真

weixin_39876739

quartus频率计时钟设置

摘要随着科技电子领域的发展,可编程逻辑器件,例如CPLD和FPGA的在设计中得到了广泛的应用和普及,FPGA/CPLD的发展使数字设计更加的灵活。这些芯片可以通过软件编程的方式对内部结构进行重构,使它达到相应的功能。这种设计思想改变了传统的数字系统设计理念,促进了EDA技术的迅速发展。数字频率计是一种基本的测量仪器。它被广泛应用与航天、电子、测控等领域。采用等精度频率测量方法具有测量精度保持恒定,

- 【python版】示波器输出的csv文件(时间与电压数据)如何转换为频率与幅值【方法②】

cxylay

pythonpython开发语言示波器csv文件频谱频域时域

要将示波器输出的CSV文件中包含的时间与电压数据转换为频率与幅值数据,你可以按照以下步骤进行处理。这里假设你的数据是一个周期性信号,可以通过傅里叶变换来实现这种转换。1、准备数据①导入CSV文件首先,使用Python、Excel或任何数据处理工具导入你的CSV文件。CSV文件中应该有两列数据,分别为时间(time)和电压(voltage)。②检查数据确保时间列的单位是一致的(例如秒),电压列是以伏

- Spring1-概述

Onlooker129

Springspring

目录Spring是什么Spring的狭义和广义SpringFramework特点Spring模块组成Spring是什么Spring是一款主流的JavaEE轻量级开源框架,Spring由“Spring之父”RodJohnson提出并创立,其目的是用于简化Java企业级应用的开发难度和开发周期。Spring的用途不仅限于服务器端的开发。从简单性、可测试性和松耦合的角度而言,任何Java应用都可以从Sp

- 注册中心 Nacos 异常实例需要30s才能剔除 Nacos心跳时间设置(踩坑)

2401_84046645

程序员java开发语言

instance.setPort(9999);Mapmetadata=newHashMap();//设置心跳的周期,单位为秒,这里将心跳间隔设置为3秒:metadata.put(PreservedMetadataKeys.HEART_BEAT_INTERVAL,“3000”);//设置心跳超时时间,单位为秒,这里将心跳超时时间设为6秒,//即服务端6秒收不到客户端心跳,会将该客户端注册的实例设为不

- html

周华华

html

js

1,数组的排列

var arr=[1,4,234,43,52,];

for(var x=0;x<arr.length;x++){

for(var y=x-1;y<arr.length;y++){

if(arr[x]<arr[y]){

&

- 【Struts2 四】Struts2拦截器

bit1129

struts2拦截器

Struts2框架是基于拦截器实现的,可以对某个Action进行拦截,然后某些逻辑处理,拦截器相当于AOP里面的环绕通知,即在Action方法的执行之前和之后根据需要添加相应的逻辑。事实上,即使struts.xml没有任何关于拦截器的配置,Struts2也会为我们添加一组默认的拦截器,最常见的是,请求参数自动绑定到Action对应的字段上。

Struts2中自定义拦截器的步骤是:

- make:cc 命令未找到解决方法

daizj

linux命令未知make cc

安装rz sz程序时,报下面错误:

[root@slave2 src]# make posix

cc -O -DPOSIX -DMD=2 rz.c -o rz

make: cc:命令未找到

make: *** [posix] 错误 127

系统:centos 6.6

环境:虚拟机

错误原因:系统未安装gcc,这个是由于在安

- Oracle之Job应用

周凡杨

oracle job

最近写服务,服务上线后,需要写一个定时执行的SQL脚本,清理并更新数据库表里的数据,应用到了Oracle 的 Job的相关知识。在此总结一下。

一:查看相关job信息

1、相关视图

dba_jobs

all_jobs

user_jobs

dba_jobs_running 包含正在运行

- 多线程机制

朱辉辉33

多线程

转至http://blog.csdn.net/lj70024/archive/2010/04/06/5455790.aspx

程序、进程和线程:

程序是一段静态的代码,它是应用程序执行的蓝本。进程是程序的一次动态执行过程,它对应了从代码加载、执行至执行完毕的一个完整过程,这个过程也是进程本身从产生、发展至消亡的过程。线程是比进程更小的单位,一个进程执行过程中可以产生多个线程,每个线程有自身的

- web报表工具FineReport使用中遇到的常见报错及解决办法(一)

老A不折腾

web报表finereportjava报表报表工具

FineReport使用中遇到的常见报错及解决办法(一)

这里写点抛砖引玉,希望大家能把自己整理的问题及解决方法晾出来,Mark一下,利人利己。

出现问题先搜一下文档上有没有,再看看度娘有没有,再看看论坛有没有。有报错要看日志。下面简单罗列下常见的问题,大多文档上都有提到的。

1、address pool is full:

含义:地址池满,连接数超过并发数上

- mysql rpm安装后没有my.cnf

林鹤霄

没有my.cnf

Linux下用rpm包安装的MySQL是不会安装/etc/my.cnf文件的,

至于为什么没有这个文件而MySQL却也能正常启动和作用,在这儿有两个说法,

第一种说法,my.cnf只是MySQL启动时的一个参数文件,可以没有它,这时MySQL会用内置的默认参数启动,

第二种说法,MySQL在启动时自动使用/usr/share/mysql目录下的my-medium.cnf文件,这种说法仅限于r

- Kindle Fire HDX root并安装谷歌服务框架之后仍无法登陆谷歌账号的问题

aigo

root

原文:http://kindlefireforkid.com/how-to-setup-a-google-account-on-amazon-fire-tablet/

Step 4: Run ADB command from your PC

On the PC, you need install Amazon Fire ADB driver and instal

- javascript 中var提升的典型实例

alxw4616

JavaScript

// 刚刚在书上看到的一个小问题,很有意思.大家一起思考下吧

myname = 'global';

var fn = function () {

console.log(myname); // undefined

var myname = 'local';

console.log(myname); // local

};

fn()

// 上述代码实际上等同于以下代码

m

- 定时器和获取时间的使用

百合不是茶

时间的转换定时器

定时器:定时创建任务在游戏设计的时候用的比较多

Timer();定时器

TImerTask();Timer的子类 由 Timer 安排为一次执行或重复执行的任务。

定时器类Timer在java.util包中。使用时,先实例化,然后使用实例的schedule(TimerTask task, long delay)方法,设定

- JDK1.5 Queue

bijian1013

javathreadjava多线程Queue

JDK1.5 Queue

LinkedList:

LinkedList不是同步的。如果多个线程同时访问列表,而其中至少一个线程从结构上修改了该列表,则它必须 保持外部同步。(结构修改指添加或删除一个或多个元素的任何操作;仅设置元素的值不是结构修改。)这一般通过对自然封装该列表的对象进行同步操作来完成。如果不存在这样的对象,则应该使用 Collections.synchronizedList 方

- http认证原理和https

bijian1013

httphttps

一.基础介绍

在URL前加https://前缀表明是用SSL加密的。 你的电脑与服务器之间收发的信息传输将更加安全。

Web服务器启用SSL需要获得一个服务器证书并将该证书与要使用SSL的服务器绑定。

http和https使用的是完全不同的连接方式,用的端口也不一样,前者是80,后

- 【Java范型五】范型继承

bit1129

java

定义如下一个抽象的范型类,其中定义了两个范型参数,T1,T2

package com.tom.lang.generics;

public abstract class SuperGenerics<T1, T2> {

private T1 t1;

private T2 t2;

public abstract void doIt(T

- 【Nginx六】nginx.conf常用指令(Directive)

bit1129

Directive

1. worker_processes 8;

表示Nginx将启动8个工作者进程,通过ps -ef|grep nginx,会发现有8个Nginx Worker Process在运行

nobody 53879 118449 0 Apr22 ? 00:26:15 nginx: worker process

- lua 遍历Header头部

ronin47

lua header 遍历

local headers = ngx.req.get_headers()

ngx.say("headers begin", "<br/>")

ngx.say("Host : ", he

- java-32.通过交换a,b中的元素,使[序列a元素的和]与[序列b元素的和]之间的差最小(两数组的差最小)。

bylijinnan

java

import java.util.Arrays;

public class MinSumASumB {

/**

* Q32.有两个序列a,b,大小都为n,序列元素的值任意整数,无序.

*

* 要求:通过交换a,b中的元素,使[序列a元素的和]与[序列b元素的和]之间的差最小。

* 例如:

* int[] a = {100,99,98,1,2,3

- redis

开窍的石头

redis

在redis的redis.conf配置文件中找到# requirepass foobared

把它替换成requirepass 12356789 后边的12356789就是你的密码

打开redis客户端输入config get requirepass

返回

redis 127.0.0.1:6379> config get requirepass

1) "require

- [JAVA图像与图形]现有的GPU架构支持JAVA语言吗?

comsci

java语言

无论是opengl还是cuda,都是建立在C语言体系架构基础上的,在未来,图像图形处理业务快速发展,相关领域市场不断扩大的情况下,我们JAVA语言系统怎么从这么庞大,且还在不断扩大的市场上分到一块蛋糕,是值得每个JAVAER认真思考和行动的事情

- 安装ubuntu14.04登录后花屏了怎么办

cuiyadll

ubuntu

这个情况,一般属于显卡驱动问题。

可以先尝试安装显卡的官方闭源驱动。

按键盘三个键:CTRL + ALT + F1

进入终端,输入用户名和密码登录终端:

安装amd的显卡驱动

sudo

apt-get

install

fglrx

安装nvidia显卡驱动

sudo

ap

- SSL 与 数字证书 的基本概念和工作原理

darrenzhu

加密ssl证书密钥签名

SSL 与 数字证书 的基本概念和工作原理

http://www.linuxde.net/2012/03/8301.html

SSL握手协议的目的是或最终结果是让客户端和服务器拥有一个共同的密钥,握手协议本身是基于非对称加密机制的,之后就使用共同的密钥基于对称加密机制进行信息交换。

http://www.ibm.com/developerworks/cn/webspher

- Ubuntu设置ip的步骤

dcj3sjt126com

ubuntu

在单位的一台机器完全装了Ubuntu Server,但回家只能在XP上VM一个,装的时候网卡是DHCP的,用ifconfig查了一下ip是192.168.92.128,可以ping通。

转载不是错:

Ubuntu命令行修改网络配置方法

/etc/network/interfaces打开后里面可设置DHCP或手动设置静态ip。前面auto eth0,让网卡开机自动挂载.

1. 以D

- php包管理工具推荐

dcj3sjt126com

PHPComposer

http://www.phpcomposer.com/

Composer是 PHP 用来管理依赖(dependency)关系的工具。你可以在自己的项目中声明所依赖的外部工具库(libraries),Composer 会帮你安装这些依赖的库文件。

中文文档

入门指南

下载

安装包列表

Composer 中国镜像

- Gson使用四(TypeAdapter)

eksliang

jsongsonGson自定义转换器gsonTypeAdapter

转载请出自出处:http://eksliang.iteye.com/blog/2175595 一.概述

Gson的TypeAapter可以理解成自定义序列化和返序列化 二、应用场景举例

例如我们通常去注册时(那些外国网站),会让我们输入firstName,lastName,但是转到我们都

- JQM控件之Navbar和Tabs

gundumw100

htmlxmlcss

在JQM中使用导航栏Navbar是简单的。

只需要将data-role="navbar"赋给div即可:

<div data-role="navbar">

<ul>

<li><a href="#" class="ui-btn-active&qu

- 利用归并排序算法对大文件进行排序

iwindyforest

java归并排序大文件分治法Merge sort

归并排序算法介绍,请参照Wikipeida

zh.wikipedia.org/wiki/%E5%BD%92%E5%B9%B6%E6%8E%92%E5%BA%8F

基本思想:

大文件分割成行数相等的两个子文件,递归(归并排序)两个子文件,直到递归到分割成的子文件低于限制行数

低于限制行数的子文件直接排序

两个排序好的子文件归并到父文件

直到最后所有排序好的父文件归并到输入

- iOS UIWebView URL拦截

啸笑天

UIWebView

本文译者:candeladiao,原文:URL filtering for UIWebView on the iPhone说明:译者在做app开发时,因为页面的javascript文件比较大导致加载速度很慢,所以想把javascript文件打包在app里,当UIWebView需要加载该脚本时就从app本地读取,但UIWebView并不支持加载本地资源。最后从下文中找到了解决方法,第一次翻译,难免有

- 索引的碎片整理SQL语句

macroli

sql

SET NOCOUNT ON

DECLARE @tablename VARCHAR (128)

DECLARE @execstr VARCHAR (255)

DECLARE @objectid INT

DECLARE @indexid INT

DECLARE @frag DECIMAL

DECLARE @maxfrag DECIMAL

--设置最大允许的碎片数量,超过则对索引进行碎片

- Angularjs同步操作http请求with $promise

qiaolevip

每天进步一点点学习永无止境AngularJS纵观千象

// Define a factory

app.factory('profilePromise', ['$q', 'AccountService', function($q, AccountService) {

var deferred = $q.defer();

AccountService.getProfile().then(function(res) {

- hibernate联合查询问题

sxj19881213

sqlHibernateHQL联合查询

最近在用hibernate做项目,遇到了联合查询的问题,以及联合查询中的N+1问题。

针对无外键关联的联合查询,我做了HQL和SQL的实验,希望能帮助到大家。(我使用的版本是hibernate3.3.2)

1 几个常识:

(1)hql中的几种join查询,只有在外键关联、并且作了相应配置时才能使用。

(2)hql的默认查询策略,在进行联合查询时,会产

- struts2.xml

wuai

struts

<?xml version="1.0" encoding="UTF-8" ?>

<!DOCTYPE struts PUBLIC

"-//Apache Software Foundation//DTD Struts Configuration 2.3//EN"

"http://struts.apache