CXL 2.0白皮书解读&翻译:计算快速链路,相对于CXL 1.1的改进,有哪些提升和要求

原著:

Debendra Das Sharma 博士 - 英特尔院士兼 I/O 技术和标准总监

以及Siamak Tavallaei - Microsoft Azure 硬件架构首席架构师、CXL™ 联盟技术工作组联合主席

Compute Express Link (CXL) 是一种开放式行业标准互连,提供高带宽、低

主机处理器和设备(例如加速器、内存缓冲区和智能 I/O 设备。 它旨在通过以下方式解决不断增长的高性能计算工作负载。

支持具有人工智能应用的异构处理和存储系统,机器学习、分析、云基础设施、网络和边缘的云化,通信系统和高性能计算。 它通过启用一致性和基于 PCI Express® (PCIe®) 5.0 的 I/O 语义之上的内存语义,用于优化在不断发展的使用模型中的性能。

这在处理这些数据时变得越来越重要,新兴应用程序需要混合部署标量、矢量、矩阵和空间架构,在 CPU、GPU、FPGA、智能 NIC 和其他加速器中。

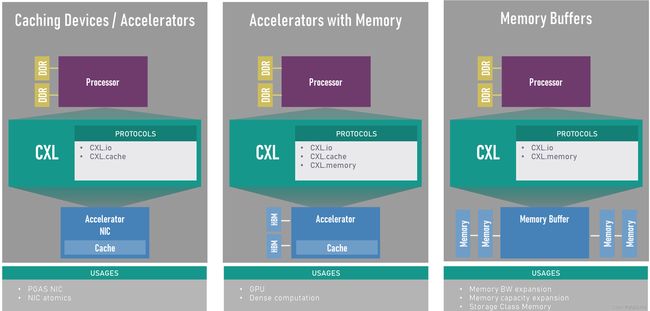

CXL 1.0 于 2019 年 3 月首次亮相,支持一组丰富的协议之间的动态多路复用

包括I/O(CXL.io,基于PCIe)、缓存(CXL.cache)和内存(CXL.memory)语义。 CXL在 CPU(主处理器)和任何内存之间保持一个统一的、连贯的内存空间,附加的 CXL 设备。

这允许 CPU 和设备共享资源并在同一平台上运行,用于更高性能、减少数据移动和减少软件堆栈的内存区域,复杂性,导致如图 1 所示的三种主要用法。

此外,由于CPU是主要负责一致性管理,它可以降低设备成本和复杂性,以及

传统上与跨 I/O 链路的一致性相关的开销。 CXL 1.1 于 2019 年 7 月推出

包括合规性测试细节。

以 130 多家成员公司证明的 CXL 的行业成功和接受度为基础,在积极参与的情况下,我们很高兴地宣布 CXL 2.0 的可用性,大约在 CXL 1.1之后一年,启用其他使用模型,同时保持与 CXL 1.1 和CXL 1.0。

CXL 2.0 通过引入三个主要领域增强了 CXL 1.1 的体验:CXL Switch、支持

用于持久内存和安全性。

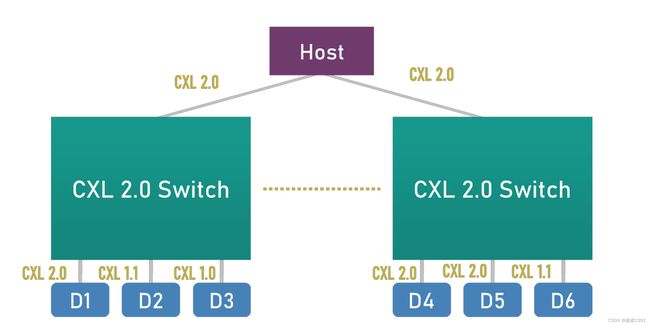

CXL 2.0 的一项新功能是支持单级切换以实现多级扇出

如图 2 所示的设备。这将使平台中的许多设备能够迁移到 CXL,同时,保持 CXL 的向后兼容性和低延迟特性。

图 2:CXL 2.0 交换机支持扇出到多个设备,同时保持向后兼容性

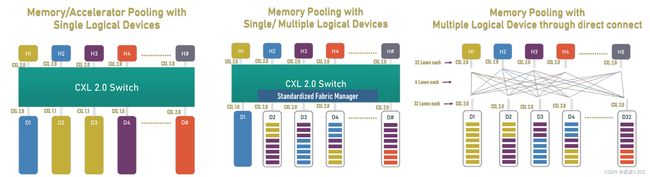

CXL 2.0 功能集的重要方面之一是支持多个逻辑设备的池化

(MLD) 以及单个逻辑设备,借助连接到多个主机的 CXL 交换机(根端口)。

此功能使服务器能够集中资源,例如加速器和/或内存,这些资源可以根据工作负载分配给不同的服务器。

假设一个服务器需要两个FPGA和一个GPU,它可以向机架中的资源管理器请求这些资源,并在可用时获取这些资源,并在完成工作后放弃它们。

同样,内存可以灵活地分配和释放到不同的服务器(又名节点或主机)根据需要。

这使系统设计人员不会过度配置机架中的每台服务器,同时获得最佳性能。 CXL 2.0 允许通过使用耦合到Type-3 多逻辑设备(MLD),如下图 3 所示。 主机 (H) 中的每种颜色代表一个定义层次结构的域或服务器。

A CXL 2.0 交换机可以处理多个域(最多 16 个此类层次结构可以到达任何一个 MLD)。

Type-3 MLD 设备在其每个 CXL 端口上最多可支持 16 个域。 类型也是可能的,3 MLD 设备对其 CXL 资源进行分区并直接连接到多个主机,每个主机都有一个专用的CXL 链路,如图 3 所示。

这有助于实现与直接连接相同的性能,因为交换机延迟被消除,这对内存访问很重要。

CXL 2.0 通过定义能够同时池化的协议增强来实现这些目标

维护不同域的服务质量和可靠性隔离要求。

它还定义了托管热插拔流程以添加/删除资源。

最重要的是 CXL 2.0 定义了一个标准化的fabric manager 确保用户拥有相同的体验,同时独立于不同类型的池,设备、主机、交换机或它们的使用模型。

图 3:使用或不使用 CXL 2.0 交换机的 CXL 设备池

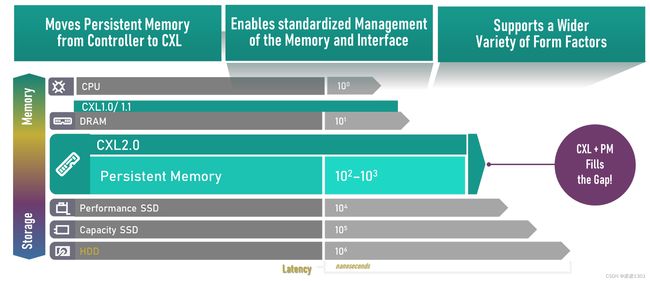

该行业的一项重要创新是围绕非易失性存储器,它正在接近 DRAM 的延迟和带宽特性,同时具有高容量和持久性的优势。 这实现了很多高性能记忆。

整个数据集都可以存储在 CXL 等存储互连架构中的加载应用程序的挑战之一是保证(将数据存储提交到持久内存中)坚持。

CXL 2.0 通过软件的架构流程和标准内存管理接口来应对这一挑战,从而使持久内存从基于控制器的方法转变为直接内存管理(图 4)。

图 4:CXL 2.0 解决了安全持久性是关键持久内存的问题

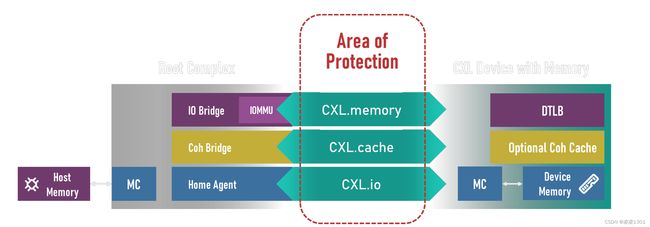

考虑到如此普遍的漏洞攻击,这是任何技术成功的基石。 CXL 在这方面取得了长足的进步,与其他行业合作,PCI-SIG 和 DMTF 等标准机构,以确保我们在提供最佳安全机制的同时拥有无缝的用户体验。 CXL 2.0 在有效的链路上启用加密与设备 TLB 等现有安全机制无缝衔接,如图 5 所示。

图 H5:CXL 2.0 的安全增强功能发布了两个版本的规范,以超越 CXL 2.0。

一年半的时间,根据计算机的反馈,CXL C 联盟是行业和终端社区,我们正在努力实现 CXL 3.0 的下一个修订版,以包含更多用途并提供更高的性能。 请加入我们这个激动人心的用户场景之旅,让我们变得更好

解读:

CXL 2.0 是一项新技术,可以让不同的设备(例如 CPU、GPU、内存和加速器)更快、更高效地进行通信。 它使用一种称为 CXL 的通用语言,可以支持不同类型的数据和操作。 它还允许设备共享内存和资源,以便它们可以更好地协同工作。 CXL 2.0 与当今计算机中广泛使用的以前版本的 CXL 和 PCIe 兼容。 CXL 2.0 还引入了新功能,例如交换、持久内存和安全性,以支持更灵活和安全的设计。 CXL 2.0 专为高性能应用而设计,例如人工智能、机器学习、云计算和边缘计算。

CXL 2.0完全兼容CXL 1.1和1.0,使用相同的PCIe 5.0物理层进行通信,所以也占用16个PCIe 5.0通道