STM32整体架构(重点待更新)

STM32系列产品命名规则

STM32F1、F4,F1是基于Cortex-M0内核,主频72MHZ。F4高性能,基于Cortex-M4内核,主频180M.

系列 :STM32 = 基于ARM®的32位微控制器

类型:F = 通用类型

产品子系列:

101 = 基本型、102 = USB基本型, USB 2.0全速设备、103 = 增强型、105或107 = 互联型

引脚数目:

T = 36脚、C = 48脚、R = 64脚、V = 100脚、Z = 144脚

闪存存储器容量:

4 = 16K字节的闪存存储器、6 = 32K字节的闪存存储器、8 = 64K字节的闪存存储器、B = 128K字节的闪存存储器、

C = 256K字节的闪存存储器、D = 384K字节的闪存存储器、E = 512K字节的闪存存储器

封装:H = BGA、T = LQFP、U = VFQFPN、Y = WLCSP64

温度范围:6 = 工业级温度范围, -40°C~85°C、7 = 工业级温度范围, -40°C~105°C

如 STM32F103ZET6 命名解释——基于ARM®的32位微控制器通用类型增强型144脚512K字节的闪存存储器LQFP封装工业级温度范围-40°C~85°C

STM32F103C8T6——基于ARM®的32位微控制器通用类型增强型48脚64K字节的闪存存储器LQFP封装工业级温度范围-40°C~85°C

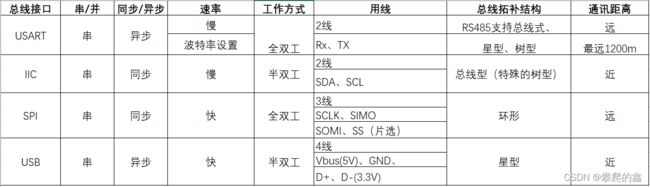

总线接口USRT、I2C、SPI、USB的异同点

GPIO

根据数据手册中列出的每个I/O端口的特定硬件特征, GPIO端口的每个位可以由软件分别配置成多种模式(具体看中文参考手册中关于GPIO功能描述部分)GPIO可以设定为4种工作模式,分别为准双向口、推挽输出、高阻输入、开漏

─ 输入浮空

─ 输入上拉

─ 输入下拉

─ 模拟输入

模拟输入上拉电阻和下拉电阻是没有用的

弱上拉和下拉电阻禁止

施密特触发器停用,施密特触发器输出值强制为0

输出缓存被禁止

读输入数据期存器, 读到的值为0

注意:IO配置成模拟输入时,不能容忍5V电压

─ 开漏输出:输出寄存器上的’0’激活N-MOS,而输出寄存器上的’1’将端口置于高阻状态(PMOS从不被激活)

─ 推挽式输出:输出寄存器是 0 时,激活 N-MOS, 而输出寄存器是 1 时,激活 P-MOS

─ 推挽式复用功能

─ 开漏复用功能

IIC(半双工)

IIC协议时序图必须会画出来

IIC协议有两根线,一根串行SCL时钟线,一根双向串行 SDA数据线

开始信号和结束信号的电平状态。

开始后,因为IIC总线最多可以挂多少个设备由IIC地址决定,8位地址,减去1位广播地址,是7位地址,2^7=128,但是地址0x00不用,那就是127个地址, 所以理论上可以挂127个从器件,所以先发送一个设备地址,选中这个设备,设备地址最后一位代表了是写还是读。选中设备后,再发送寄存器地址,代表选中某个寄存器,再开始传输数据。

八位设备地址=7位从机地址+读/写地址,

再给地址添加一个方向位位用来表示接下来数据传输的方向,

0表示主设备向从设备(write)写数据,

开始信号:SCL 为高电平时,SDA 由高电平向低电平跳变,开始传送数据。

结束信号:SCL 为高电平时,SDA 由低电平向高电平跳变,结束传送数据。

应答信号:接收数据的 IIC 在接收到 8bit 数据后,向发送数据的 IIC 发出特定的低电平脉冲,表示已收到数据。CPU 向受控单元发出一个信号后,等待受控单元发出一个应答信号,CPU 接收到应答信号后,根据实际情况作出是否继续传递信号的判断。若未收到应答信号,由判断为受控单元出现故障。

IIC信号在数据传输过程中,当SCL=1高电平时,数据线SDA必须保持稳定状态,不允许有电平跳变,只有在时钟线上的信号为低电平期间,数据线上的高电平或低电平状态才允许变化。SCL=1时 数据线SDA的任何电平变换会看做是总线的起始信号或者停止信号。

SPI(高速全双工的通信总线)

SPI四种模式,简述其中一种模式,画出时序图

在芯片资料上极性和相位一般表示为CPOL(Clock POLarity)和CPHA(Clock PHAse), 极性和相位组合成4种工作模式。

| CPOL | CPHA | |

|---|---|---|

| MODE0 | 0 | 0 |

| MODE1 | 0 | 1 |

| MODE2 | 1 | 0 |

| MODE3 | 1 | 1 |

spi四种模式SPI的相位(CPHA)和极性(CPOL)分别可以为0或1,对应的4种组合构成了SPI的4种模式(mode)

Mode 0 CPOL=0, CPHA=0

Mode 1 CPOL=0, CPHA=1

Mode 2 CPOL=1, CPHA=0

Mode 3 CPOL=1, CPHA=1

主机与从机需要工作在相同的模式下才可以正常通讯,实际中采用较多的是“模式 0”与“模式 3”。

时钟极性CPOL: 即SPI空闲时,时钟信号SCLK的电平(1:空闲时高电平; 0:空闲时低电平) 时钟相位CPHA: 即SPI在SCLK第几个边沿开始采样(0:第一个边沿开始; 1:第二个边沿开始)

sd卡的spi常用的是mode 0 和mode 3,这两种模式的相同的地方是都在时钟上升沿采样传输数据,区别这两种方式的简单方法就是看空闲时,时钟的电平状态,低电平为mode 0 ,高电平为mode 3。

spi的具体通信过程

NSS、 SCK、 MOSI 信号都由主机控制产生,而 MISO 的信号由从机产生,主机通过该信号线读取从机的数据。 MOSI 与 MISO 的信号只在 NSS 为低电平的时候才有效,在 SCK 的每个时钟周期 MOSI 和 MISO 传输一位数据。

SPI 通讯的 起始信号:NSS 信号线由高变低

SPI 通讯的停止信号 :NSS 信号线由低变高

UASRT

串口通讯协议分为物理层和协议层

物理层:规定通讯系统中具有机械、电子功能部分的特性,确保原始数据在物理媒体的传输。

协议层:规定通讯逻辑,统一收发双方的数据打包、解包标准。

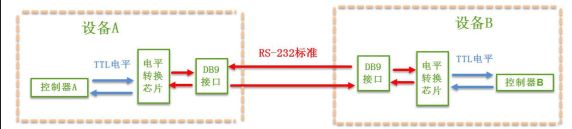

串口通讯可分为 TTL标准及 RS-232标准

RS-232 标准主要规定了信号的用途、通讯接口以及信号的电平标准

两个通讯设备的“DB9 接口”之间通过串口信号线建立起连接,串口信号线中使用“RS-232标准”传输数据信号。

RS-232电平标准的信号不能直接被控制器直接识别,所以这些信号会经过一个**“电平转换芯片”转换成控制器能识别的“TTL 标准”的电平信号,才能实现通讯**。

中断

概念

STM32 每个外设都可以产生中断 ,F103 在内核上搭载了一个中断响应系统, 支持为数众多的系统异常和外部中断。

其中系统中断有 8 个(如果把 Reset 和 HardFault 也算上的话就是 10 个) ,外部中断有 60个。除了个别中断的优先级被定死外,其它中断的优先级都是可编程的。

NVIC 的了解:

NVIC 是嵌套向量中断控制器,控制着整个芯片中断相关的功能,它跟内核紧密耦合,是内核里面的一个外设。 STM32的 NVIC 是 Cortex-M3 的 NVIC 的一个子集 。

中断配置

配置中断时我们一般只用 ISER、 ICER 和 IP 这三个寄存器

ISER ——使能中断**

ICER ——失能中断**

IP ——设置中断优先级

中断优先级定义

中断优先级寄存器 NVIC_IPRx,用来配置外部中断的优先级, IPR宽度为 8bit,原则上每个外部中断可配置的优先级为 0~255,数值越小,优先级越高。但是绝大多数 CM3 芯片都会精简设计,以致实际上支持的优先级数减少,在 F103 中,只使用了高 4bit

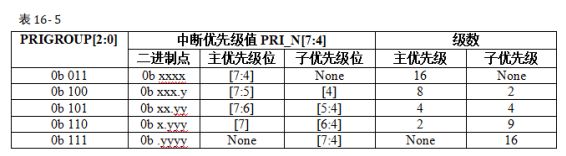

表格 16‑4 F103 使用 4bit 表达优先级

被分组成抢占优先级和子优先级。如果有多个中断同时响应,抢占优先级高的就会抢占抢占优先级低的优先得到执行,如果抢占优先级相同,就比较子优先级。如果抢占优先级和子优先级都相同的话,就比较他们的硬件中断编号,编号越小,优先级越高。

优先级分组

优先级的分组由内核外设 SCB 的应用程序中断及复位控制寄存器 AIRCR 的 PRIGROUP[10:8] 位决定, F103 分为了 5 组,具体如下:主优先级 = 抢占优先级

设置优先级分组可调用库函数 HAL_NVIC_SetPriority() 实现,有关 NVIC 中断相关的库函数都在库文件 stm32f1xx_hal_cortex.c 和 stm32f1xx_hal_cortex.h 中。

中断编程

配置中断的3各编程要点:

**1、 使能外设某个中断,这个具体由每个外设的相关中断使能位控制。**比如:串口有发送完成中断,接收完成中断,这两个中断都由串口控制寄存器的相关中断使能位控制。

2、配置 EXTI 中断源、配置中断优先级。

(1)用来设置中断源,不同的中断中断源不一样,且不可写错,即使写错了程序也不会报错,只会导致不响应中断。

(2)PreemptionPriority:抢占优先级,具体的值要根据优先级分组来确定

(3)SubPriority:子优先级,具体的值要根据优先级分组来确定

3、编写中断服务函数

在启动文件 startup_stm32f103xe.s 中预先为每个中断都写了一个中断服务函数,只是这些中断函数都是为空,为的只是初始化中断向量表。实际的中断服务函数都需要我们重新编写,关于中断服务函数的函数名必须跟启动文件里面预先设置的一样,如果写错,系统就在中断向量表中找不到中断服务函数的入口,直接跳转到启动文件里面预先写好的空函数,并且在里面无限循环,实现不了中断。