FPGA面试题

面试题摘自尤老师FPGA 。

1

2

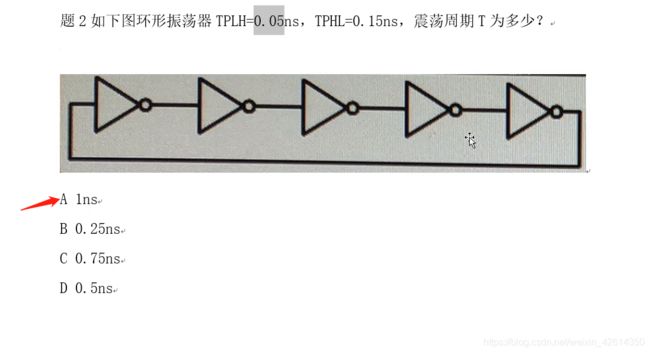

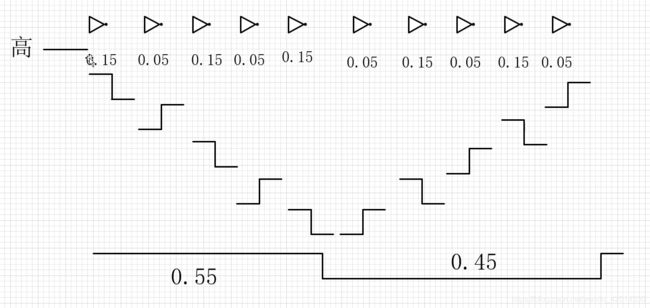

TPLH:脉冲由低电平变成高电平的延迟时间

TPHL: 脉冲由高电平变成低电平的延迟时间

本题采用假设法,假设开始输入信号为高电平,经过两次非门是一个时钟周期 (TPHL+TPLH = 0.2 ns) ,震荡周期意思为下次到达起始位置时的电平信号与第一次到达起始位置的电平信号相同时所花的时间。

所以跑完一轮是2.5个时钟周期,此时回到起始位置为低电平,与第一次开始的高电平不等,故还要经过一轮;总共经过两轮也就是五个时钟周期才满足一个震荡周期。所以震荡周期为 0.2 * 5 = 1 ns 。

图解法 :

3

4

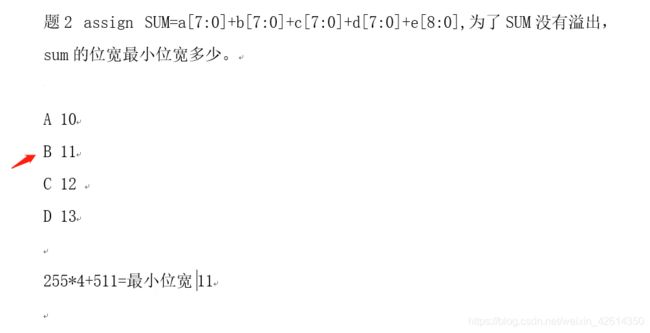

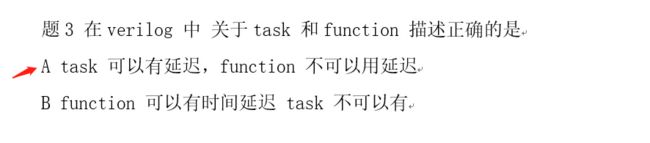

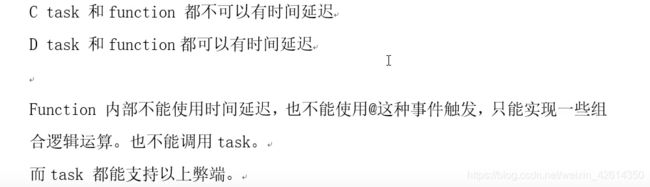

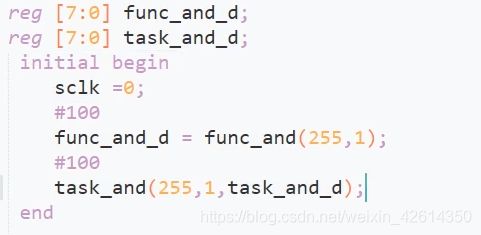

5 task 和 function 关系

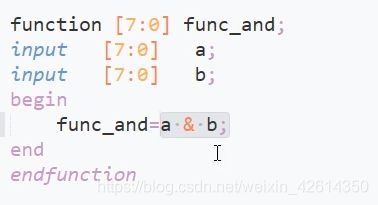

function 语法 :

function function的信号名 (相当于输出信号)

输入信号定义

(逻辑语法)

返回值 (指定信号 = …)

endfunction

注意 : function 只能是组合逻辑,不可以是时序逻辑 。不能加时延 。 function 中不能去调用 task 。

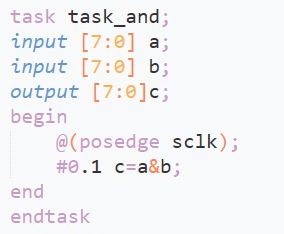

task 语法 :

task 中 使用 always @ (posedge clk) 和 使用 @ (posedge clk) 的区别 :

always@(posedge clk)中的任务没有执行完的情况下是不会在下一个时钟上升沿到来的时候再次重复执行的

在前面不带always的情况下,@(posedge)仅会按顺序执行一次。即在 task 语句中如果有多个 @ (posedge clk) 语句,那么在每个时钟上升沿到来时就按照顺序执行 @ (posedge clk) 的一行 。

task 语法 :

task

输入输出信号定义

逻辑赋值 (图中是经过 0.1 ns 延迟后再赋值)

endtask

调用方式:

本工程是在 initial 块中调用

例化 function 方法中 需要赋值输入信号的形参,将 function 的结果赋值给输出信号 。

例化 task 的方法中将输入信号和输出信号都要赋值到 task 的形参中去 。注意输出信号赋值的位置即可 。

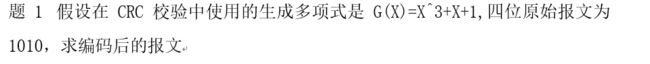

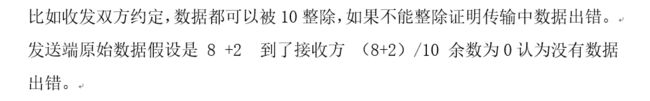

6 CRC 问题

CRC校验 : 循环冗余校验的缩写

6.1 举例说明 :

CRC 可以理解为校验发送数据 和 接收数据之间的误差(有无错误)。

6.2 CRC 生成多项式

6.2.1 生成多项式用到二进制异或除法

6.2.2 求解校验位过程 :

题中的生成多项式的最高次幂 表示校验位的位宽 。

四位原始报文为 信息位 。

编码后的报文 = 信息位 与 校验位 的 组合 。

6.2.3解题方法

题中生成多项式最高次幂 = 校验位位宽 = 3

信息位 = 原始报文 = 1010

信息位低位添0 (增加个数为校验位位宽大小) = 1010 000

之后该数进行异或 后 除生成多项式 ; 直到余数小于等于 3 位后得到校验位 。

(1) 生成多项式求法

G(X) = X^3 + X + 1

生成多项式的最高次幂 + 1 = 生成多项式位宽 (本题为4位)

生成多项式 G(X) 中 :

X^3 的系数 = 1 第四位

X^2 的系数 = 0 第三位

X^1 (X) 的系数 = 1 第二位

X^0 (1) 的系数 = 1 第一位

故生成多项式为 1011 (即生成多项式的另一种表现形式) = X^3 + X + 1

(2) 异或计算

信息位添 0 后的数 异或 生成多项式

1010 000

1011

异或等于

0001 000

1 011

异或等于

0 011

故校验位为 011 (3位)

编码后的报文 = 信息位 (1010) + 校验位 (011) = 1010011

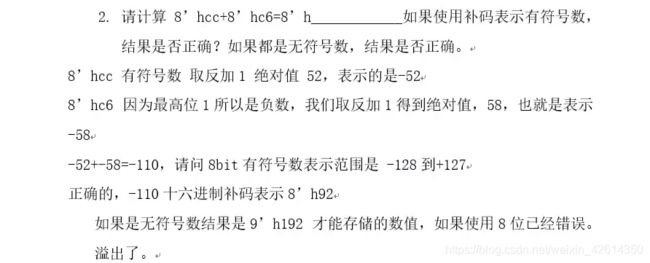

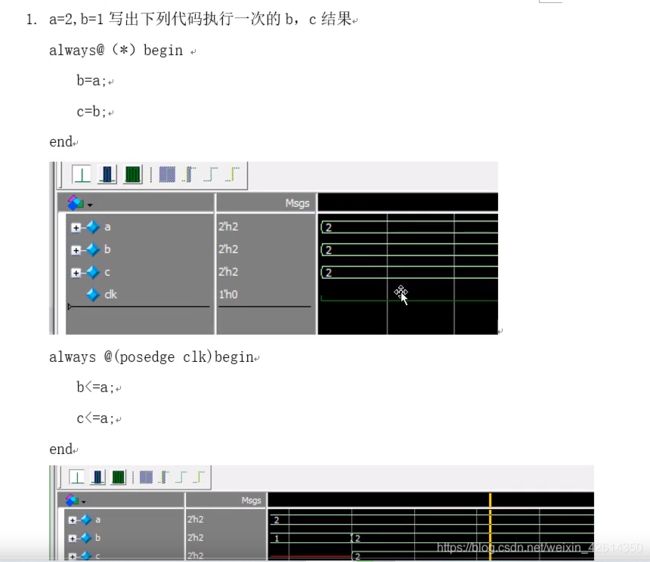

7

always @ (*) 组合逻辑,当其运算式子中的 任一信号发生改变,就触发逻辑块中的代码进行计算 。本题中 a 和 b 的值都发生变化,所以 b 和 c 也都进行计算得到新值 。 (按照先后顺序计算)

always @ (posedge clk) 时序逻辑,是在时钟上升沿后触发。

所以 b 和 c 的值是在时钟上升沿之后才得到的计算后的值 。

8

9

首先说明“由于国家标准规定,逻辑图中最低有效位(LSB)到最高有效位(MSB)的电路排列顺序应从上到下,从左到右。因此定义移位寄存器中的数据从低位触发器移向高位为右移,反之则为左移。这一点与通常计算机程序中规定相反,后者从自然二进制数的排列考虑,将数据移向高位定义为左移,反之为右移。”此内容摘自《电子技术基础-数字部分》康华光主编教材。

图示为:

9 级 移位寄存器,即由九个移位寄存器组成的 将位宽为九的数据进行左移移位操作的电路。经复位后的数据为 9’b1_1111_1111,第一个移位寄存器从输入的第0位数据开始移位到第1位,第二个移位寄存器将第1位数据右移到第2位,以此类推。其中将第4位和第8位进行异或操作后的数赋值给经过移位后的数据的第0位。将经过以为后的数据的第6位赋值给输出的数据 pi 。

代码实现如下 :

10

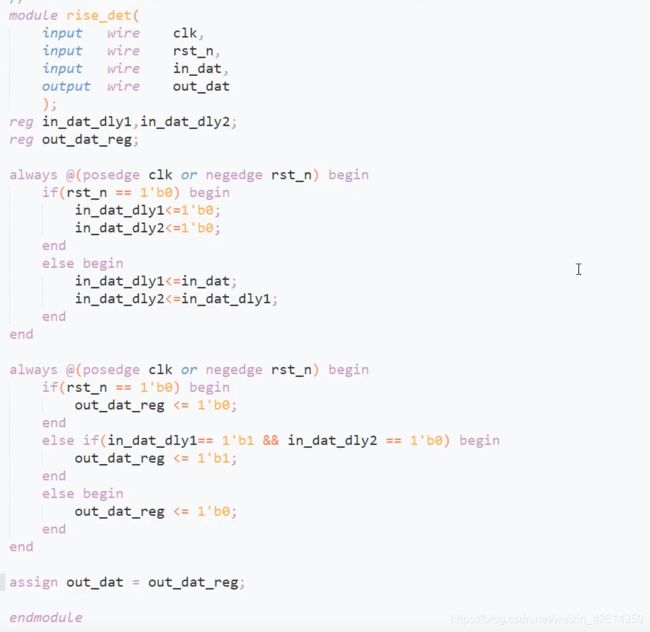

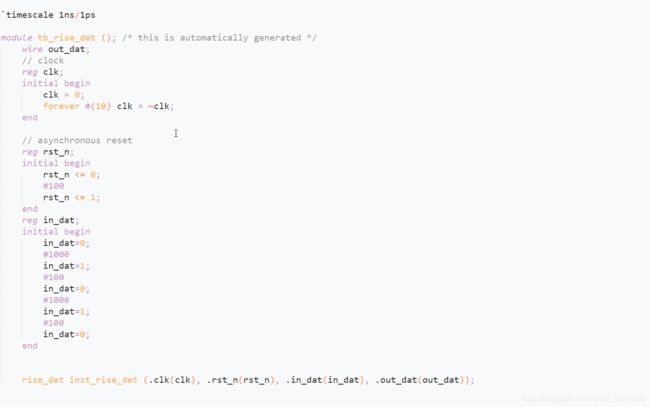

题目及其解读如下图 :

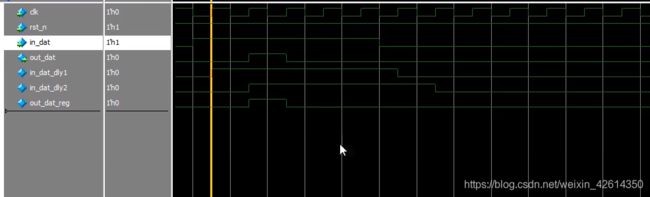

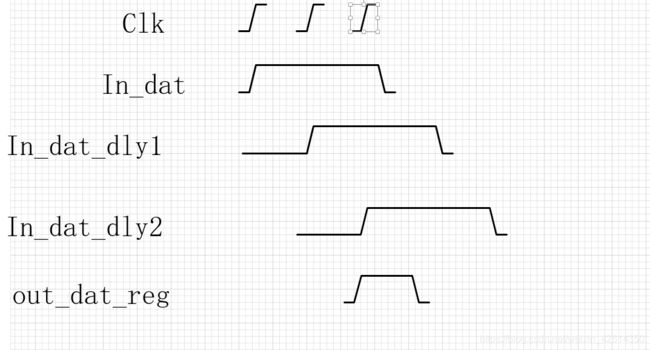

信号波形图解如下图所示 :

本题考验对时序设计的理解,尤其是触发器概念的理解。时序信号 (触发器内信号) 的判定为在时钟上升沿到来前进行逻辑判断,在时钟上升沿到来后进行当前输出信号赋值。

in_dat_dly1 和 in_dat_dly2 都是 reg 型信号,采用时序逻辑进行赋值 (本题中是对 in_dat 进行延迟 1 clk 赋值给 in_dat_dlly1 , 对 in_dat 延迟 2 clk 赋值给 in_dat_dly2) 。

out_dat_reg 是 reg 型信号,用来判断 in_dat_dly1 和 in_dat_dly2 的时序逻辑 。

注意 : 时序逻辑中异步复位的写法

always @ (posedge clk or negedge rst_n) begin

逻辑语句块

end

ps : rst_n 为 低电平复位信号

具体代码如下 :

仿真波形图所下图所示 :

11

问答题