EDA基础概念

EDA基础概念

- EDA和CAD

-

- CAD工具

- EDA工具

- EDA技术实现目标

- 可编程逻辑器件简称PLD发展历程

- FPGA简介

- CPLD简介

- FPGA和CPLD区别

- 是否需要同时学习FPGA和CPLD

- Xilinx(赛灵思)公司介绍(AMD收购)

-

- 开发工具

- Xilinx产品

- Altera(阿尔特拉)公司介绍(Intel收购)

-

- 开发工具

- Altera产品

- Xilinx和Altera产品对比

- Lattice公司(中文:莱迪思)

- Microsemi(中文:美高森美)

- Xilinx ZYNQ简介

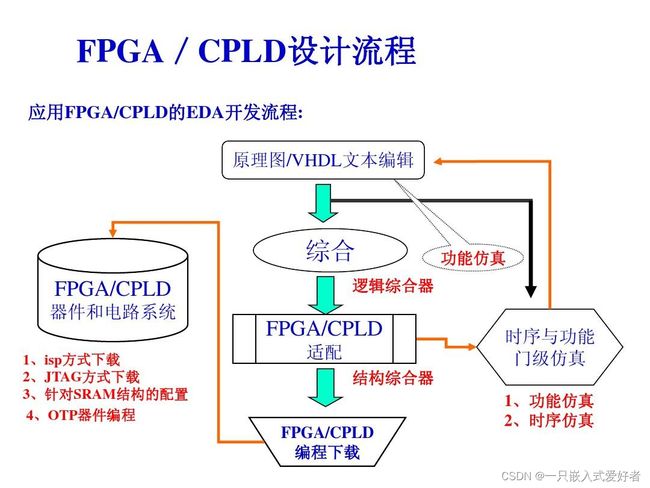

- FPGA/CPLD设计流程

- 硬件描述语言(HDL)

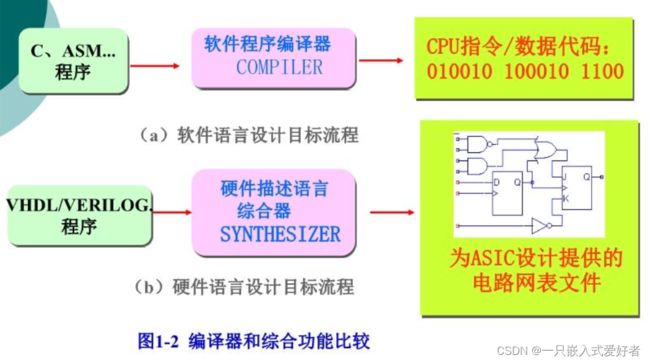

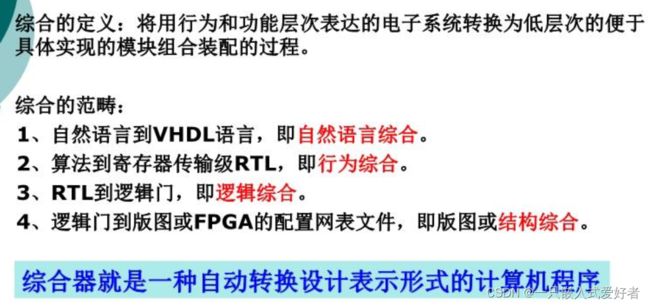

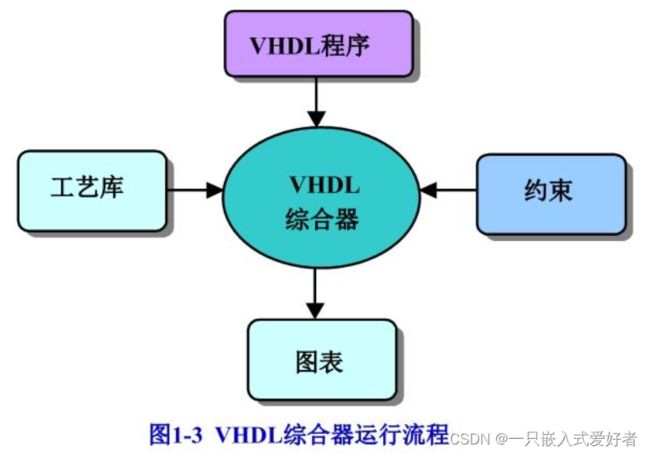

- HDL综合

EDA和CAD

CAD工具

计算机辅助设计工具,主要作用:绘图工具,使用者:遍布各个行业。电气CAD系统的目标与范围有:机械产品电气设计包括电路图、接线图、安装图、接线盒和电柜以及按钮站的设计。这五个部分之间不是孤立存在的,而是互相联系,这五个部分既能单独运行又能实现信息共享。为此电气CAD系统的目标与范围是:建立适应完成以上功能要求、保证设计质量又能提高效率、缩短设计周期、减少人工劳动的电气CAD系统,包括电路图、接线图、安装图、接线盒和电柜、按钮站的设计。

EDA工具

EDA:Electronic Design Automation,即电子设计自动化,是指是以计算机为平台,使用通用软件包,开展电子电路设计、电子电路仿真、PCB设计,CPLD/FPGA设计,IC设计等工作。也即在CAD绘图技术基础上融合了应用电子技术、计算机技术、信息处理技术等实现电子产品的自动设计。使用者:特指有关电子系统的相关的行业。

1.电子电路设计

例如:multisim和matlab都能进行电路仿真,例如可以画出电路图,仿真观察电压电流的波形

2.PCB设计(电路板设计)

例如:Protel、altium desinger可以进行PCB图的绘制

3.IC设计(芯片设计)

很复杂,包括模拟IC和数字IC。例如:芯片设计工具Cadence

4.PLD设计工具(可编程逻辑器件)

FPGA(现场可编程门阵列)的工具有Quartus是Altera公司出的软件,可以对其公司的FPGA芯片进行编程,下载。

注:

1.很多软件的功能非常复杂,在电子系统的各个级别(物理级、电路级、系统级)都有很强的功能。如:quartus既能做数字IC设计,也能做FPGA设计。

2.流程图绘制工具:Visio是半个EDA软件

EDA技术实现目标

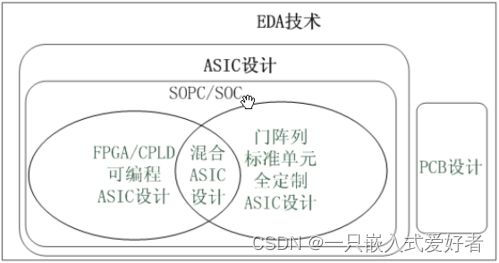

利用EDA技术进行电子系统设计的最后的目标,是完成专用集成电路ASIC或印制电路板(PCB)的设计和实现。

作为EDA技术最终实现目标的ASIC,可以通过三种途径来完成:

1、可编辑逻辑器件

FPGA/CPLD是实现这一途径的主流器件

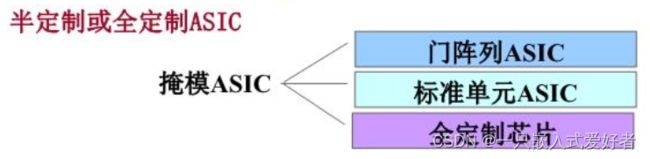

2、半定制或全定制ASIC

统称为掩膜ASIC,或直接称ASIC,分为以下三种

3、混合ASIC

可编程逻辑器件简称PLD发展历程

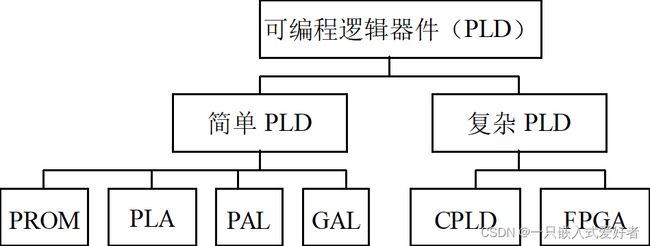

可编程逻辑器件简称PLD(Programable Logic Device),它是EDA技术发展的一个重要支持点,也是实现电子系统非常重要的一种方法,PLD的发展推动了EDA工具的发展,也改变了电子系统的设计方法。PLD的集成度分类:

复杂PLD(CPLD与FPGA):

- 1985年,美国Xilinx公司推出了现场可编程门阵列(FPGA,Field Programmable Gate Array)

- CPLD(Complex Programmable Logic Device),即复杂可编程逻辑器件,是从Altera 的 EPLD 改进而来的。

FPGA简介

- FPGA(Field- Programmable Gate Array),即现场可编程门阵列,它是在 PAL、GAL、CPLD等可编程器件的基础上进一步发展出来的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

- FPGA 普遍用于实现数字电路模块,用户可对 FPGA 内部的逻辑模块和 I/O模块重新配置,以实现用户的需求。它还具有静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改。

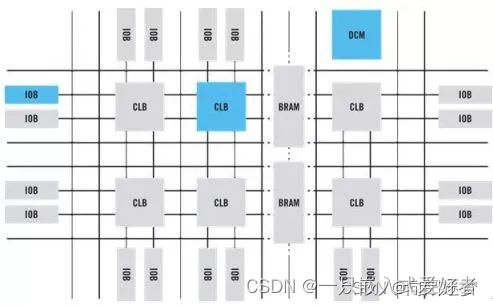

- FPGA的基本结构包括可编程输入输出单元,可配置逻辑块,数字时钟管理模块,嵌入式块 RAM,布线资源,内嵌专用硬核,底层内嵌功能单元。

- FPGA 的设计流程包括算法设计、代码仿真以及设计、板级调试,设计者以及实际需求建立算法架构,利用 EDA 建立设计方案或 HD 编写设计代码,通过代码仿真保证设计方案符合实际要求,最后进行板级调试,利用配置电路将相关文件下载至 FPGA 芯片中,验证实际运行效果。

FPGA 架构主要包括可配置逻辑块 CLB(Configurable Logic Block)、输入输出块 IOB(Input Output Block)、内部连线(Interconnect)和其它内嵌单元四个部分。

CLB是FPGA的基本组件,它提供逻辑和存储功能。基本逻辑块可以是晶体管、与非门、多路复用器、查找表 (LUT)、类似PAL的结构甚至处理器之类的任何东西。Xilinx和Altera都使用基于查找表 (LUT) 的逻辑块来实现逻辑和存储功能。CLB实际数量和特性会依器件的不同而改变,但是每个 CLB 都包含一个由 4 或 6个输入、若干选择电路(多路复用器等)和触发器组成的可配置开关矩阵。基于Xilinx的FPGA中的逻辑块称为可配置逻辑块或CLB,而基于Altera的FPGA中的类似结构称为逻辑阵列块或LAB。

FPGA 可支持许多种 I/O 标准,因而可以为系统设计提供理想的接口桥接。FPGA 内的 I/O 按 bank 分组,每个 bank 能独立支持不同的 I/O 标准。目前最先进的 FPGA 提供了十多个 I/O bank,能够提供灵活的 I/O 支持。

CLB 提供了逻辑性能,灵活的互连布线则负责在 CLB 和 I/O 之间传递信号。布线有几种类型,从设计用于专门实现 CLB 互连(短线资源)、到器件内的高速水平和垂直长线(长线资源)、再到时钟与其它全局信号的全局低 skew 布线(全局性专用布线资源)。

CPLD简介

CPLD主要是由可编程逻辑宏单元(LMC,Logic Macro Cell)围绕中心的可编程互连矩阵单元组成,其中LMC逻辑结构较复杂,并具有复杂的I/O单元互连结构,可由用户根据需要生成特定的电路结构,完成一定的功能。由于 CPLD内部采用固定长度的金属线进行各逻辑块的互连,所以设计的逻辑电路具有时间可预测性,避免了分段式互连结构时序不完全预测的缺点。到90年代,CPLD发展更为迅速,不仅具有电擦除特性,而且出现了边缘扫描及在线可编程等高级特性。较常用的有Xilinx公司的EPLD和Altera公司的CPLD。

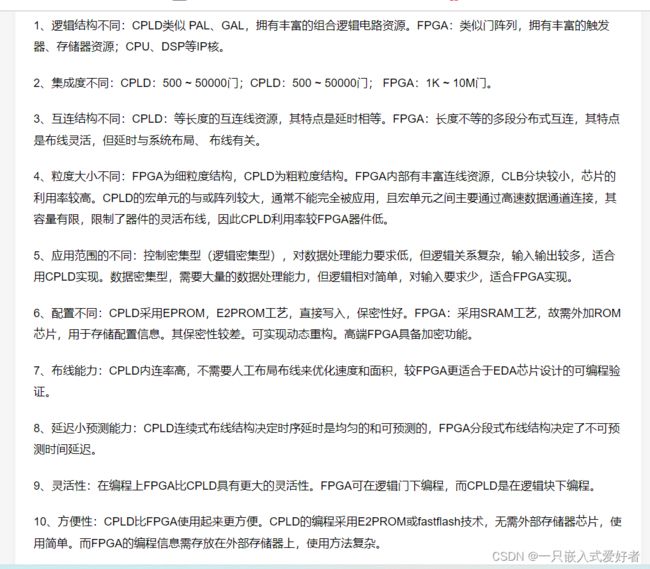

FPGA和CPLD区别

各个厂家叫法不尽相同:

PLD(Programmable Logic Device)是可编程逻辑器件的总称,早期多EEPROM工艺,基于乘积项(Product Term)结构。FPGA (Field Programmable Gate Arry)是指现场可编程门阵列,最早由Xilinx公司发明。多为SRAM 工艺,基于查找表(Look Up Table)结构,要外挂配置用的EPROM。

Xilinx把SRAM工艺,要外挂配置用的EPROM的PLD叫FPGA,把Flash工艺(类似EEPROM工艺),乘积项结构的PLD叫CPLD;

Altera把自己的PLD产品:MAX系列(EEPROM工艺),FLEX/ACEX/APEX系列(SRAM工艺)都叫作CPLD,即复杂PLD(Complex PLD)。由于FLEX/ACEX/APEX系列也是SRAM工艺,要外挂配置用的EPROM,用法和Xilinx的FPGA一样,所以很多人把Altera的FELX/ACEX/APEX系列产品也叫做FPGA

下面整理一下CPLD和FPGA的主要区别:

1、CPLD的逻辑阵列更适合可重复编程的EEPROM或Flash技术来实现。而FPGA显然是利用SRAM技术更合适。

2、 由于是EEPROM或者Flash工艺决定了CPLD是有一定的擦写次数限制的。而FPGA在实际使用中几乎可以说是无配置次数限制。

3、CPLD由于采用的是EEPROM或者Flash工艺所以配置掉电后不丢失,也就不需要外挂配置芯片。而FPGA采用的是SRAM工艺,配置在掉电后就没有了,因此需要一个外部配置芯片。

4、CPLD的安全性更高。由于配置芯片的存在,FPGA的保密性就会比CPLD略差。逻辑数据有可能被读取。(当然FPGA芯片会有一定的加密措施)

5、 CPLD由于不需要上电重新配置,所以上电后可以马上工作。而FPGA上电后需要配置时间,逻辑量的大小配置方式的区别也会影响配置时间的长短。

6、由于CPLD的连续式布线结构,决定了它的时序延时是均匀和固定的。而FPGA采用的分段式布线结构造成了延时不固定。

7、由于工艺难度的差异,CPLD一般集成度较低,大多为几千门或几万门的芯片规模,做到几十万门已经很困难。而FPGA基于SRAM工艺,集成度更高,可以轻松做到几十万门甚至几百万门的芯片规模,最新的FPGA产品已经接近千万门的规模。

8、 同样由于结构的差异,CPLD更适合完成的是复杂的组合逻辑,如编、译码的工作。而FPGA更适合做复杂的时序逻辑。换句话说就是FPGA更适合触发器丰富的逻辑结构,CPLD适合于触发器有限但是乘积项丰富的逻辑结构。

9、也是由于工艺的原因,一般CPLD会比FPGA的功耗高。

当然以上只是CPLD和FPGA通常意义上的区别,技术是在不断发展中的,这些差异也不能一概而论。随着技术的发展,CPLD和FPGA也在不断的更新当中。

是否需要同时学习FPGA和CPLD

完全没有必要,因为FPGA和CPLD的设计语言都是Verilog,至于CPLD和FPGA内部结构不一样,在编码阶段完全看不出来,软件会根据CPLD还是FPGA自动生成编程文件,所以学习的话建议值学习FPGA即可,FPGA学会了,基本就会用CPLD了。另外现在的电路设计规模越来越大,动不动都是上万个或者几十万个甚至上百万个寄存器规模,这种规模下,CPLD资源太少,不会被考虑。

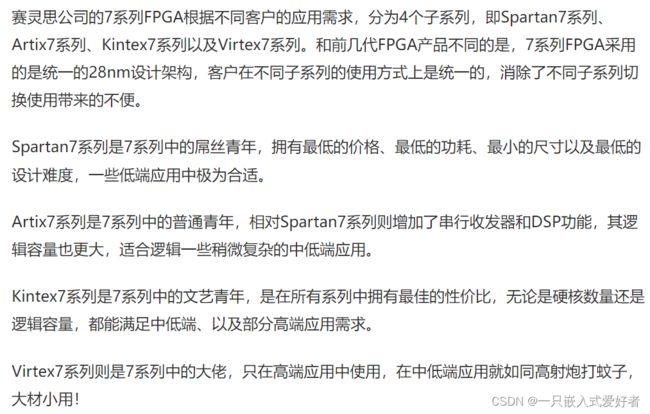

Xilinx(赛灵思)公司介绍(AMD收购)

XILINX成立于1984年位于美国,是全球领先的可编程逻辑完整解决方案的供应商,也是目前排名第一的FPGA解决方案提供商。首创了现场可编程逻辑阵列(FPGA)并催生了一个新的行业,并于1985年首次推出商业化产品。1994年,Xilinx发布了Virtex®FPGA,完成了其原始FPGA在架构和性能方面的突破。2012年,Xilinx推出了第一款28nmZynq®器件,这是一款支持应用处理器并包含缓存、内存控制器、外设、FPGA逻辑、DSP模块和SerDes模块的完整SoC系统。Xilinx第二代ZynqSoC(异构MPSoC)于2017年问世,并添加了新的处理引擎,目标是为正确的任务启用正确的硬件引擎,优化复杂系统的处理要求。2018年,Xilinx发布了Alveo™数据中心加速卡,简化了数据中心高性能、适应性强的FPGA加速的开发和部署。2019年,Xilinx发布了第一个自适应计算加速平台(ACAP)Versal。Versal®ACAP支持多种特定领域架构(DSA)和计算结构,其核心优势在于其作为多核通用SoC的功能,包括额外的硬件和软件可编程引擎,以实现最佳的功率和性能权衡。

美国当地时间2022年2月14日,AMD宣布以全股份交易(all-stock transaction)方式完成对赛灵思(Xilinx)的收购。

开发工具

Vivado和ISE。ISE是老开发软件了,目前基本上已经被vivado取代,只有xilinx公司的一些十几年前生产的FPGA才使用ISE开发,新的FPGA都支持更好用的vivado。

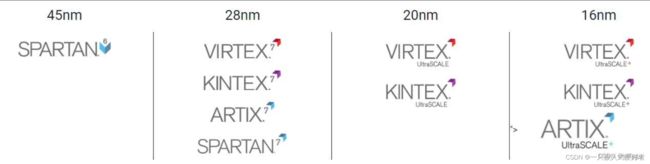

Xilinx产品

其FPGA产品包括如下几个部分:

1、Spartan系列:定位于低端市场,目前最新器件为Spartan7,为28nm工艺,Spartan6以前都是45nm工艺,该系列器件价格实惠,逻辑规模相对较小。

2、Artix系列:Xilinx推出Artix系列FPGA产品,其目的应该是作为低端Spartan和中高端Kintex系列FPGA的过渡产品,尤其在通信接口方面,Artix系列相比Spartan有很大优势,所以,如果设计不是仅仅需要逻辑资源,而是需要先进的高速接口,不妨考虑Artix系列。

3、Kintex和Virtex系列为Xilinx的中、高端产品,包含有28nm的Kintex7和Virtex7系列,20nm的Kintex7 Ultrascale和Virtex7 Ultrascale系列,还有16nm的Kintex7 Ultrascale+ 和Virtex7 Ultrascale+系列。其拥有丰富的高速接口,主要用于通信,雷达,信号处理,IC验证等高端领域。

4、全可编程SoC和MPSoC系列,包括有Zynq-7000和Zynq UltraScale+ MPSoC系列FPGA,内嵌有ARM Cortex系列CPU内核。

XILINX FPGA型号系列分类参考

XILINX FPGA型号

Altera(阿尔特拉)公司介绍(Intel收购)

业界与Xilinx齐名的FPGA供应商,2015年被CPU芯片届的大佬Intel收购了,因此现在也称为Intel的FPGA。

开发工具

QuartusII。

Altera产品

产品系列:

1、MAXII系列

MAXII 系列为CPLD,Altera以其CPLD闻名。

2、Cyclone系列

最新为Cyclone10,性价比高,类似于xilinx 公司的Spartan系列和Artix系列。

3、Stratix系列

最新为Stratix10,为高端应用,与Xilinx的Kintex、Virtex系列竞争。

4、Arria系列

SOC系列FPGA, 内置ARM Cotex A9的核。

5、Intel的新产品arria 10 fpga系列

支持DDR4存储器接口的FPGA。硬件设计人员现在可以使用最新的Quartus II软件v14.1,在Arria10 FPGA和SoC设计中实现DDR4数据读写。

Altera FPGA型号系列分类参考

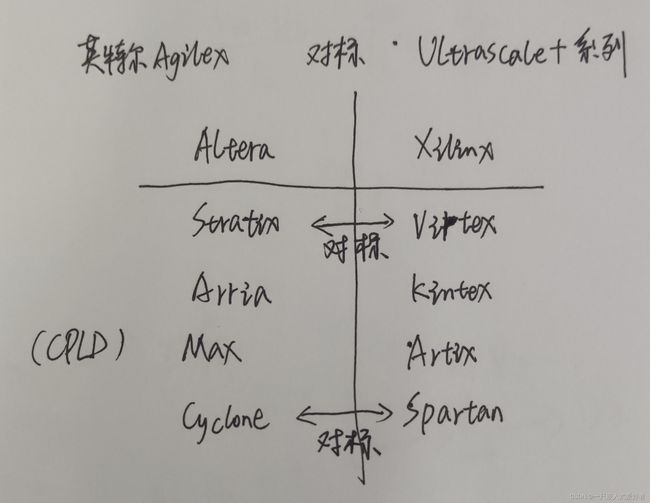

Xilinx和Altera产品对比

总的来说,目前国内用的最多的还是xilinx和altera(Intel)的FPGA,但从目前市场上的用户需求来看,xilinx的FPGA使用量又大大超过altera的FPGA,因此建议小白直接从xilinx公司的FPGA开始入门

Lattice公司(中文:莱迪思)

著名的可编程逻辑解决方案供应商,实力仅次于Xilinx和Altera。

开发工具:ISPLEVER

产品介绍:

1、ECP系列为Lattice自己的开发的FPGA系列,提供低成本,高密度的FPGA解决方案,而且还有高速Serdes等接口,适用于民品解决方案居多。

2、ICE系列为收购SilioncBlue的超低功耗FPGA,也曾用在iPhone7里面,实现了FPGA首次在消费类产品中应用,可见其功耗有多低。

3、Mach系列替代CPLD,实现粘合逻辑的最佳选择。作为CPLD的发明者,Lattice在CPLD领域依然表现卓越。

Microsemi(中文:美高森美)

并购了actel,专注于美国军工和航空领域,产品为反熔丝结构FPGA和基于Flash的FPGA为主,具有抗辐照和可靠性高的优势,最近Microsemi又被Microchip(微芯)并购。

开发工具:Libero

产品介绍:

1、基于FLASH的通用FPGA系列,包括有PolarFireMid-Range FPGAs,RTG4Radiation-Tolerant FPGAs,IGLOO2Low-Density FPGAs三个高、中、低端系列。

2、特殊领域应用系列…

Xilinx ZYNQ简介

ZYNQ 的全称是 Zynq-7000 All Programmable SoC,也就是说,ZYNQ 实际上是一个片上系统(System on Chip,SoC),ZYNQ 是赛灵思公司(Xilinx)推出的新一代全可编程片上系统(APSoC),它将处理器的软件可编程性与 FPGA 的硬件可编程性进行完美整合,以提供无与伦比的系统性能、灵活性与可扩展性。与传统 SoC解决方案不同的是,高度灵活的可编程逻辑(FPGA)可以实现系统的优化和差异化,允许添加定制外设与加速器,从而适应各种广泛的应用。

Zynq-7000 系列是 Xilinx 于 2010 年 4 月推出的行业第一个可扩展处理平台,旨在为视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理能力与计算性能。这款基于 ARM 处理器的 SoC可满足复杂嵌入式系统的高性能、低功耗和多核处理能力等要求。

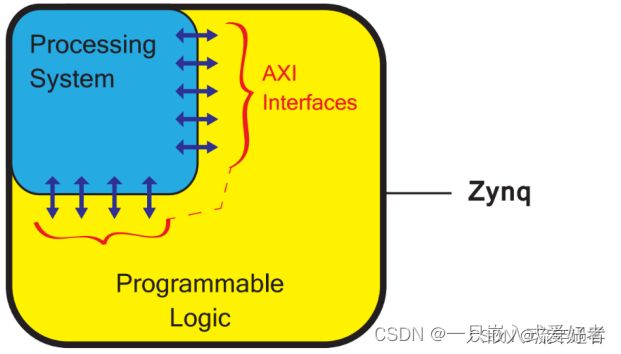

ZYNQ 的本质特征,ZYNQ 是由两个主要部分组成的:一个由双核 ARM Cortex-A9 为核心构成的处理系统(PS,Processing System),和一个等价于一片 FPGA 的可编程逻辑(PL,Programmable Logic)部分。由于该新型器件的可编程逻辑部分基于赛灵思 28nm 工艺的 7 系列 FPGA,因此该系列产品的名称中添加了“7000”,以保持与 7 系列 FPGA 的一致性,同时也方便日后本系列新产品的命名。ZYNQ 架构的简化模型如下图所示:

上图中,PS 具有固定的架构,包含了处理器和系统的存储器;而 PL 完全是灵活的,给了设计者一块“空白画布”来创建定制的外设。在 ZYNQ 上,ARM Cortex-A9 是一个应用级的处理器,能运行像 Linux 这样的操作系统,而可编程逻辑是基于 Xilinx 7 系列的 FPGA 架构。

ZYNQ 架构实现了工业标准的 AXI 接口,在芯片的两个部分之间实现了高带宽、低延迟的连接。这意味着处理器和逻辑部分各自都可以发挥最佳的用途,而不会产生在两个分立器件之间的接口开销。与此同时,又能获得系统被简化为单一芯片所带来的好处,包括物理尺寸和整体成本的降低。

FPGA/CPLD设计流程

硬件描述语言(HDL)

硬件描述语言HDL(Hardware Description Language ) 类似于高级程序设计语言. 它是一种以文本形式来描述数字系统硬件的结构和行为的语言, 用它可以表示逻辑电路图、逻辑表达式,复杂数字逻辑系统的逻辑功能。用HDL编写设计说明文档易于存储和修改,并能被计算机识别和处理.

HDL是高层次自动化设计的起点和基础,目前常用的HDL有VHDL、Verilog HDL、System Verilog和System C(C++语言的硬件描述扩展),VHDL和Verilog HDL是电子设计主流描述语言,同时也是IEEE推出的两种标准。

HDL综合

HDL综合器的作用,是将用HDL语言描述的RTL级电路转化成门级网表。生成的网表是由用导线相互连接的寄存器传输级功能块组成。在这一转化过程中,包含了三个步骤:

(1)转化:将系统的HDL描述,转化为各个功能单元连接的电路结构的门级网表;

(2)优化:根据设计者施加的时序、面积等约束条件,针对实际目标器件的结构将转化的门级网表按一定的算法进行逻辑重组和优化;

(3)映射:根据时序和面积约束条件,从目标器件的工艺库中搜索恰当的单元来构成电路。