MIPI D-PHYv2.5笔记(21) -- Forward High-Speed Data Transmission Timing

声明:作者是做嵌入式软件开发的,并非专业的硬件设计人员,笔记内容根据自己的经验和对协议的理解输出,肯定存在有些理解和翻译不到位的地方,有疑问请参考原始规范看

DDR时钟差分信号和Data差分信号的时序关系如下图所示:

图1 Data to Clock Timing Definitions

数据以正交于时钟的关系被发出,因此时钟信号边沿可以被接收器直接用于采样接收到的数据。

发送器要确保在一次burst传输的第一个载荷bit期间,发送一个DDR时钟的上升沿,这样第一个载荷bit能够在这个上升时钟沿上被接收器所采样,第二个载荷bit在下降沿上被采样,随后的数据bits,会在交替的上升沿和下降沿上被采样。

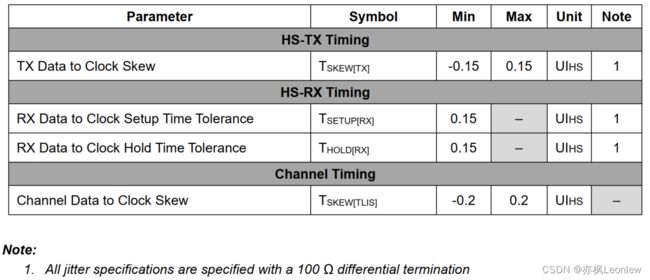

数据时钟时序规范

Data Rate ≥ 0.08 Gbps and ≤ 1 Gbps

图2 Data-Clock Timing Specifications for ≥ 0.08 Gbps and ≤ 1 Gbps

Skew的规范![]() 表示数据发出时间对于理想的位移½UIINST的正交时钟边沿(displaced quadrature clock edge)所允许的偏差。

表示数据发出时间对于理想的位移½UIINST的正交时钟边沿(displaced quadrature clock edge)所允许的偏差。![]() 和

和![]() 都描述了数据和时钟之间的关系。

都描述了数据和时钟之间的关系。![]() 是在一个时钟上升沿和下降沿到来之前,数据建立的最小时间;

是在一个时钟上升沿和下降沿到来之前,数据建立的最小时间;![]() 是在一个时钟上升或下降沿之后,数据保持的最小时间。

是在一个时钟上升或下降沿之后,数据保持的最小时间。

Data Rate > 1 Gbps and ≤ 1.5 Gbps

图3 Data-Clock Timing Specifications for > 1 Gbps and ≤ 1.5 Gbps

Data Rate > 1.5 Gbps and ≤ 4.5 Gbps 图4 Data-Clock Timing Specifications for > 1.5 Gbps and ≤ 4.5 Gbps

图4 Data-Clock Timing Specifications for > 1.5 Gbps and ≤ 4.5 Gbps

规范的SSC(Normative Spread Spectrum Clocking)

展频时钟(有时也被称为“Specturm Spread Clocking”)是一种常见的技术,在发送器的时钟增加了一个低频调制,用来减少能量峰值(peak emission)。

图5 Spread Spectrum Clocking Requirements

D-PHY v2.0版本及以上的发送器和接收器,数据速率大于2.5Gbps的情况要支持SSC。

D-PHY v2.0版本及以上的发送器要提供给系统集成者启用/禁用SSC传输的机制。

SSC能够被用于HS Data Transmission模式。如果在HS Data Transmission模式中使用,SSC传输在整个模式期间要保持一致。

SSC不能用于Escape Mode。SSC在发送器内部实现,在时钟和所有High-Speed Data Lanes之间有共同的:1. 单个调制格式表(modulated profile),2. 单个调制速率(modulation rate),3. 单个SSC偏差(deviation)。

所有SSC参数都是为HS Clock定义的。

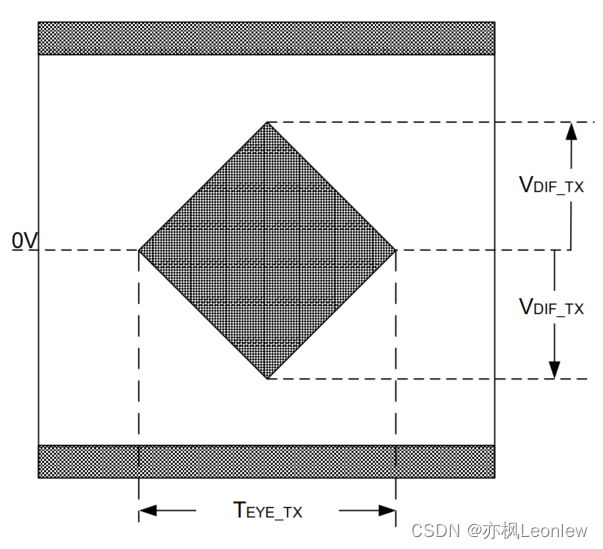

发送器眼图规范

眼图的规范对于数据速率 1.5 Gbps和4.5 Gbps之间的发送器都适用,对于Data Lanes和Clock Lanes都适用。

图6 TX Eye Diagram Specification

图7 Transmitter Eye Diagram Specification

图8 Transmitter Eye Diagram Validation Setup

图8 Transmitter Eye Diagram Validation Setup

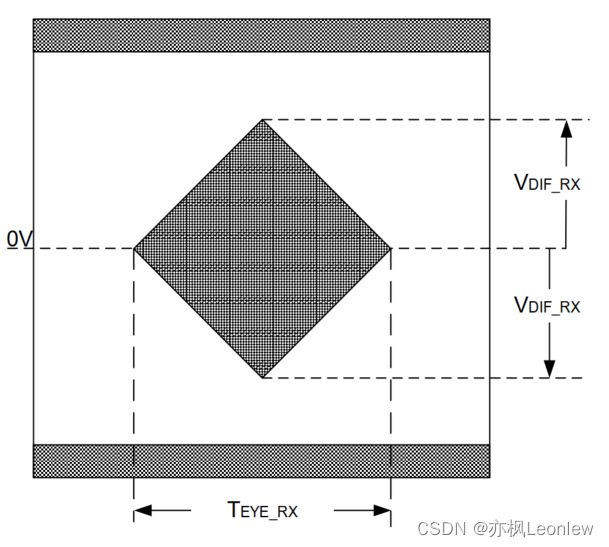

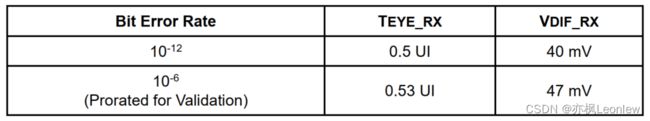

接收器眼图规范

下图展示的接收器眼图规范定义了接收器所容忍的最坏情况下的眼图。这个眼图规范适用于数据速率在1.5Gbps和4.5Gbps之间的接收器。

图9 Receiver Eye Diagram Specification

图10 Receiver Eye Diagram Specification

图11 Receiver Eye Diagram Validation Setup