ARM Cortex-M 调试器 - 基础知识

文章目录

- 前言

- Processor memory map

- 内核寄存器

- SFR(特殊功能寄存器)

-

- 0xE000E000-0xE000ED8F (CPUID/AIRCR)

- 0xE000EF00-0xE000EFFF

- Core Debug

-

- DBG_HCSR: 0xE000EDF0

- DBG_CRSR: 0xE000EDF4

- DBG_CRDR: 0xE000EDF8

- DBG_EMCR: 0xE000EDFC

- DP- Debug Port

-

- DP0_ABORT (0x00 SW W)

- DP0_IDCODE (0x00 SW R)

- DP4_CTRL/STAT (0x04 SW W/R)

- DP8_SELECT (0x08 SW W)

- DP8_RESEND register 0x08 (SW R)

- DPc_RDBUFF register 0x0C (SW R)

- AP Access Port

-

- AP0_CSW (Control and Status Word Register) 0x00

- AP4_TAR (Transfer Address Register) 0x04~08

- APc_DRW (Data Read/Write Register) 0x0C

- AP_BDR0-3 (Banked Data Registers 0-3)

- AP_DRAR (Debug ROM Address Register)

- IDR (ID Register)

- System Debug

- AHB-AP

-

- CSW 0x00

- TAR 0x04~08

- DRW 0x0C

- Bandked Data 4 0x10-0x1C

- Debug ROM Address 0xF8

- IDR 0xFC

- SWD 时序

- MCU连接过程

-

- 1. SWD初始化

- 2. 解锁 AP

- MCU 读写操作

- MM32-LINK 测试(MT304)

-

- 1. SWD Connect: read DP_IDCODE

- 2. Set DP_CTRL/STAT PWR UP

- 3. Read CPUID(`0xE000_ED00`)

- 4. Unknow: Read from 0xE000_1028/38/48/58

- 5. DBG_HCSR(`0xE000_EDF0`) = 0xA05F_0003, Halt CPU, DBG_EN

- 7. DBG_EMCR(`0xE000_EDFC`) = 0x0100_0001, Catch Reset & Trace

- 8. DBG_AIRCR(`0xE000_ED0C`) = 0x05FA_0004, SYS_RST_REQ

- 9. nRST = 0. dalay xxms

- 10. nRST = 1. delay 20ms

- 11. read DBG_HCSR(`0xE000_EDF0`) 3times

- 12. DBG_EMCR(`0xE000_EDFC`) = 0x0100_0000, Trace(3 times)

- while true: step11 cycle

- 总结

推荐博文1: SWD协议通信的简单总结

前言

根据《ARM Technical Reference Manual cortex_m3_r1p1_trm》和《Arm® Debug Interface Architecture Specification ADI v6.0.pdf》进行梳理。

Processor memory map

内核寄存器

Cortex-M3 处理器实现了ARM v7-M架构。这包括整个 16 位的Thumb指令集和基本的 Thumb-2 32位指令集架构。处理器无法执行ARM指令。

- Thumb 指令集是 ARM 指令集的一个子集,被重新编码为 16 位。它支持更高的代码密度和具有 16 位宽或 16 位窄的内存数据总线的系统。

- Thumb-2 是对 Thumb 指令集体系结构(ISA)的一个主要增强。Thumb-2 支持比 Thumb 更高的代码密度,并提供更高的性能。

The processor has the following 32-bit registers:

- 13 General-Purpose Registers,

r0-r12 - Stack Point alias of banked registers, SP_process & SP_main.

SP - Link Register,

r14 - Program Counter,

r15 - one Program Status Register,

xPSR.

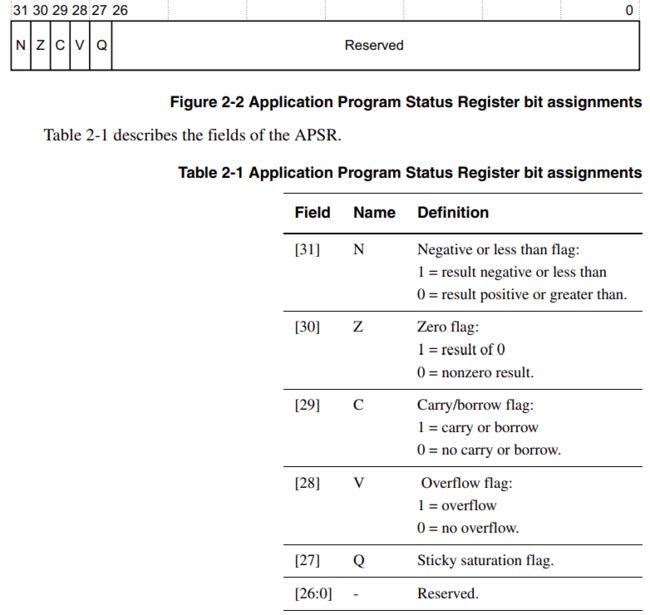

R16寄存器 xPSR

Special-purpose Program Status Registers,系统级的处理器状态分为三类:

SFR(特殊功能寄存器)

0xE000E000-0xE000ED8F (CPUID/AIRCR)

NVIC register map:

- 0xE000E000 - 0xE000E00F. Interrupt Type Register

- 0xE000E004

Interrupt Control Type Registerr

- 0xE000E004

- 0xE000E010 - 0xE000E0FF. System Timer

- 0xE000E010

SysTick Control and Status Registerr/w - 0xE000E014

SysTick Reload Value Registerr/w - 0xE000E018

SysTick Current Value Registerr/wc - 0xE000E01C

SysTick Calibration Value Registerr

- 0xE000E010

- 0xE000E100 - 0xE000ECFF. NVIC

- 0xE000E100

Irq 0 to 31 Set Enable Registerr/w - 0xE000E11C

Irq 224 to 239 Set Enable Registerr/w - 0xE000E180

Irq 0 to 31 Clear Enable Registerr/w - 0xE000E19C

Irq 224 to 239 Clear Enable Registerr/w - 0xE000E200

Irq 0 to 31 Set Pending Registerr/w - 0xE000E21C

Irq 224 to 239 Set Pending Register - 0xE000E280

Irq 0 to 31 Clear Pending Register - 0xE000E29C

Irq 224 to 239 Clear Pending Register - 0xE000E300

Irq 0 to 31 Active Bit Register - 0xE000E31C

Irq 224 to 239 Active Bit Register - 0xE000E400

Irq 0 to 31 Priority Register - 0xE000E4F0

Irq 236 to 239 Priority Register

- 0xE000E100

- 0xE000ED00 - 0xE000ED8F. SCB

System Control Block, 包括:CPUID \ System Control, Configuration & Status\ Fault reporting.- 0xE000ED00

CPUID Base Registerr - 0xE000ED04

Interrupt Control State Registerr/w - 0xE000ED08

Vector Table Offset Registerr/w - 0xE000ED0C

Application Interrupt/Reset Control Registerr/w - 0xE000ED10

System Control Registerr/w - 0xE000ED14

Configuration Control Registerr/w - Fault reporting

- 0xE000ED00

1. CPUID 0xE000ED00

- m3_r1p1 复位值为 0x411F

C231。

根据 CPUID 识别 ARM 内核: - bit [31:24]: 0x41 = ARM

- bit [23:20]: variant number

- bit [19:16]: 0xF

bit[15:14]: b11= Cortex Familybit[13:12]: b00 = versionbit[11:10]: b00 = reservedbit[9:8]: b10 = M(v7-M)bit[7:4]: b0011 = Cortex-M3. Family member- bit [3:0]: revision numer

通过对ARM 全系列CPUID进行整理,可得:

| Part No. | Core |

|---|---|

| 0xC20 | Cortex-M0 |

| 0xC21 | Cortex-M1 |

| 0xC23 | Cortex-M3 |

| 0xC24 | Cortex-M4 |

| 0xC27 | Cortex-M7 |

| 0xC60 | Cortex-M0+ |

| 0xD20 | Cortex-M23 |

| 0xD21 | Cortex-M33 |

| 0xD22 | Cortex-M55 |

2. AIRCR 0xE000ED0C

应用程序中断和复位控制寄存器 (Application Interrupt/Reset Control Registe)

- [31:16] VECTKEY 。寄存器键。写入这个寄存器需要在

VECTKEY字段中输入0x05FA。否则,写值将被忽略。 - [31:16] VECTKEYSTAT。读入 0xFA05

- [15] ENDIANESS。数据字节顺序。

ENDIANESS在复位时从大端输入端口采样。您不能在重置之外更改ENDIANESS- 1 =大端

- 0 =小端

- [14:11] reserved

- [10:8] 中断优先级分组字段:

PRIGROUP字段是一个二进制点位指示符,用于为具有相同抢占级别的异常创建子优先级 - [2]

SYSRESETREQ:导致向外部系统断言一个信号,表明请求复位

用于强制除调试外的所有主要组件的大型系统重置。设置此位不会阻止“Halting Debug ”运行 - [1]

VECTCLRACTIVE:清除活动向量位:- 1 清除所有活动NMI、故障、中断的状态信息

- 0 =不清除

重新初始化堆栈是应用程序的责任。该位用于在调试期间返回到已知状态。(自动清零)该操作不会清除IPSR。因此,如果应用程序使用它,它必须只能在基本激活级别上使用,或者在可以设置活动位的系统处理程序中使用

- [0]

VECTRESET:系统复位。重置系统,除调试组件外:- 1 =复位系统

- 0 =不重启系统

VECTRESET位会自动清除。Reset清除VECTRESET位。对于调试,只有当core 被 halted 时才写入此位。

*注意:

SYSRESETREQ由系统复位清除,这意味着同时断言VECTRESET可能会导致SYSRESETREQ在写入的同一周期内被清除。 这可能会阻止外部系统看到SYSRESETREQ。 因此,建议独占使用VECTRESET和SYSRESETREQ,切勿两者同时写1。

0xE000EF00-0xE000EFFF

- 0xE000EF00 - 0xE000EF0F. Software Trigger Exception Register

- 0xE000EF00

Software Trigger Interrupt Registerw - 0xE000EFD0

Peripheral identification register (PID4)r - 0xE000EFDC

Peripheral identification register (PID7) - 0xE000EFE0

Peripheral identification register Bits 7:0 (PID0)r - 0xE000EFEC

Peripheral identification register Bits 31:24 (PID3) - 0xE000EFF0

Component identification register Bits 7:0 (CID0) - 0xE000EFFC

Component identification register Bits 31:24 (CID3)

- 0xE000EF00

- 0xE000EFD0 - 0xE000EFFF. ID Space

Core Debug

核心调试通过核心调试寄存器访问。对这些寄存器的调试访问是通过高级高性能总线(AHB-AP)端口进行的.处理器可以通过内部的私有外围总线(PPB)直接访问这些寄存器。

Halt mode debugging / 内核 Halt 状态下的调试方法

- 调试器可以通过设置调试暂停控制和状态寄存器的

C_DEBUGEN和C_HALT位来暂停内核。 内核通过设置调试停止控制和状态寄存器的S_HALT位在停止时进行确认。 - 通过暂停内核,将

C_STEP位设置为1,然后将C_HALT位清除为0,内核可以单步执行。内核通过设置DBG_HCSR.S_HALT位确认单步完成并重新暂停。

退出内核调试

- Core 可以通过清除调试停止和状态寄存器中的

C_DEBUGEN位来退出停机调试。

DBG_HCSR: 0xE000EDF0

-

C_Halt: Halts the core.

暂停核心。当核心停止时,该位是自动设置的。例如断点。此位在核心重置时清除。该位只能在C_DEBUGEN为1时写入,否则将被忽略。当设置该位为1时,C_DEBUGEN也必须以相同的值写入1(值[1:0]为 2’b11)。核心可以停止自己,但只有当C_DEBUGEN已经是1并且只有当它使用b11进行写操作时)。 -

C_DebugEN:Enables debug.

启用调试。这只能由 AHB-AP 编写,而不是由 core 编写。它在内核写入时被忽略,内核不能设置或清除它。当写入C_HALT来停止自身时,核心必须向它写入1。

READ: -

S_REGRDY:

调试内核寄存器选择器寄存器上的寄存器读/写可用。 最后一次传输完成。 -

S_HALT

当 S_HALT 为高时,内核处于调试状态 -

S_SLEEP

表示内核正在休眠.WFI、WFE 或 SLEEP-ON-EXIT, 必须使用 C_HALT 来获得控制权或等待中断唤醒。 -

S_LOCKUP:

如果内核正在运行(未停止)并且存在锁定条件,则读取为 1。 -

S_RETIRE_ST: Indicates that an instruction has completed since last read. This is a sticky bit that clears on read. This determines if the core is stalled on a load/store or fetch. 表示自上次读取后指令已完成。 这是一个在读取时清除的粘性位。 这确定核心是否在加载/存储或获取时停止。

-

S_RESET_ST

表示自从上次读取该位以来,内核已被复位或正在被复位。 这是一个在读取时清除的粘性位。 因此,读取两次并得到 1 然后 0 意味着它在过去被重置。 读取两次并获得 1 意味着它现在正在重置(仍然保持在重置状态)。

DBG_CRSR: 0xE000EDF4

DBG_CRDR: 0xE000EDF8

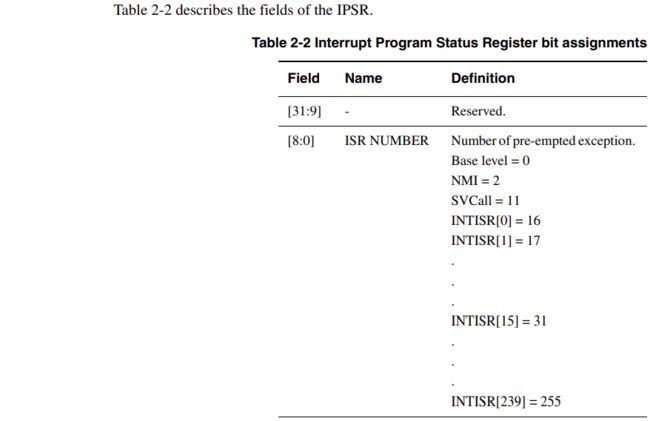

DBG_EMCR: 0xE000EDFC

- VC_CoreReset: Reset Vector Catch.

复位向量。如果内核 Core 发生复位,停止正在运行的系统 - TRCENA:

该位必须设置为 1 以启用跟踪和调试块:数据观察点和跟踪 (DWT)/仪器跟踪宏单元 (ITM)/嵌入式跟踪宏单元 (ETM)/跟踪端口接口单元(TPIU). 除非需要跟踪,否则这可以控制电源使用。 应用程序可以启用此功能,供 ITM 使用或由调试器使用。

注意:如果 TIEOFF_TRCENA 定义在实施期间在 CM3Defs.v 中未注释,则无法设置 TRCENA。 - MON_REQ:

这使监视器能够确定其唤醒的原因:1 =由 MON_PEND; 0 = debug异常唤醒。 - MON_STEP:

当 MON_EN = 1 时,这会步进内核。 当 MON_EN = 0 时,该位被忽略。 这相当于 C_STEP。 中断仅根据监视器的优先级和 PRIMASK、FAULTMASK 或 BASEPRI 的设置进行步进。 - MON_PEND:

当优先级允许时,挂起监视器以激活。 这可以通过 AHB-AP 端口唤醒显示器。 它等效于用于监视器调试的 C_HALT。该寄存器不会在系统复位时复位。 它只能通过上电复位来复位。 复位处理程序或更高版本中的软件,或由 DAP 提供的软件必须启用调试监视器。 - MON_EN:Enable the debug monitor.

启用调试监视器。 启用后,系统处理程序优先级寄存器控制其优先级。 如果禁用,则所有调试事件都会进入硬故障。 调试停止控制和状态寄存器中的 C_DEBUGEN 覆盖该位。矢量捕获是半同步的。 当看到匹配事件时,请求停止。 因为处理器只能在指令边界上停止,它必须等到下一个指令边界。 结果,它在异常处理程序的第一条指令处停止。 但是,当向量捕获已触发时,存在两种特殊情况:- 如果在向量化、向量读取或堆栈推送错误期间发生故障,则在或响应的故障处理程序上发生停止,用于向量错误或堆栈推送。- 如果在引导过程中出现迟到的中断,则不接受。 也就是说,在这种情况下,支持延迟到达优化的实现必须抑制它。 - VC_HARDERR: Debug trap on Hard Fault

- VC_INTERR: Debug Trap on interrupt/exception service errors. These are a subset of

other faults and catches before BUSERR or HARDERR. - VC_BUSERR: Debug Trap on normal Bus error.

- VC_STATERR:Debug trap on Usage Fault state errors

- VC_CHKERR:Debug trap on Usage Fault enabled checking errors.

- VC_NOCPERR:Debug trap on Usage Fault access to Coprocessor which is not present

or marked as not present in CAR register. - VC_MMERR:Debug trap on Memory Management faults.

- VC_CORERESET

重置向量捕获。 如果发生核心重置,则停止运行系统。仅当 C_DEBUGEN = 1 时可用。

该寄存器不会在系统复位时复位。该寄存器由上电复位复位。 位 [19:16] 总是在内核复位时清零。调试监视器由复位处理程序或更高版本中的软件启用,或者由 AHB-AP 端口启用。

矢量捕获是半同步的。 当看到匹配事件时,请求停止。 因为处理器只能在指令边界上停止,它必须等到下一个指令边界。 结果,它在异常处理程序的第一条指令处停止。 但是,当向量捕获已触发时,存在两种特殊情况:- 如果在向量读取或堆栈推送错误期间发生故障,则在向量错误或堆栈推送的相应故障处理程序上发生暂停。- 如果在向量读取或堆栈推入错误期间检测到迟到中断,则不接受。 也就是说,在这种情况下,支持迟到优化的实现必须抑制它。

矢量捕获只能用于停止调试。高16位是用于监控控制,低16位是暂停、异常支持。

DP- Debug Port

#define DP_IDCODE 0x00U // IDCODE Register (SW Read only)

#define DP_ABORT 0x00U // Abort Register (SW Write only)

#define DP_CTRL_STAT 0x04U // Control & Status

#define DP_WCR 0x04U // Wire Control Register (SW Only)

#define DP_SELECT 0x08U // Select Register (JTAG R/W & SW W)

#define DP_RESEND 0x08U // Resend (SW Read Only)

#define DP_RDBUFF 0x0CU // Read Buffer (Read Only)

DP0_ABORT (0x00 SW W)

- ORUNERRCLR, bit[4]

要将 CTRL/STAT.STICKYORUN 溢出错误位清除为 0b0,请将 0b1 写入该位。

To clear the CTRL/STAT.STICKYORUN overrun error bit to 0b0, write 0b1 to this bit. - WDERRCLR, bit[3]

要将 CTRL/STAT.WDATAERR 写入数据错误位清除到 0b0,请将 0b1 写入该位。

To clear the CTRL/STAT.WDATAERR write data error bit to 0b0, write 0b1 to this bit. - STKERRCLR, bit[2]

要将 CTRL/STAT.STICKYERR 粘滞错误位清除为 0b0,请将 0b1 写入该位。

To clear the CTRL/STAT.STICKYERR sticky error bit to 0b0, write 0b1 to this bit. - STKCMPCLR, bit[1]

要将 CTRL/STAT.STICKYCMP 粘性比较位清除为 0b0,请将 0b1 写入该位。 是否实现 CTRL/STAT.STICKYCMP 位由实现定义。

To clear the CTRL/STAT.STICKYCMP sticky compare bit to 0b0, write 0b1 to this bit. It is IMPLEMENTATION DEFINED whether the CTRL/STAT.STICKYCMP bit is implemented. - DAPABORT, bit[0]

要生成中止当前 AP 事务的 AP 中止,请将 0b1 写入该位。

仅当调试器在较长时间内收到 WAIT 响应时才执行此写入操作。

To generate an AP abort, which aborts the current AP transaction, write 0b1 to this bit.

Do this write only if the debugger has received WAIT responses over an extended period

DP0_IDCODE (0x00 SW R)

DP4_CTRL/STAT (0x04 SW W/R)

- CSYSPWRUPACK, bit[31],

ro. System powerup acknowledge.

系统上电确认。 指示 CSYSPWRUPACK 信号的状态。 - CSYSPWRUPREQ, bit[30],

rw. System powerup request.

系统上电请求。 该位控制 CSYSPWRUPREQ 信号。上电复位后,该位为 0b0。 - CDBGPWRUPACK, bit[29],

ro. Debug powerup acknowledge.

调试上电确认。 指示 CDBGPWRUPACK 信号的状态。 - CDBGPWRUPREQ, bit[28]. Debug powerup request.

调试上电请求。 该位控制 CDBGPWRUPREQ 信号。 上电复位后,该位为 0b0。 - CDBGRSTACK, bit[27]

ro. Debug reset acknowledge.

调试复位确认。 指示 CDBGRSTACK 信号的状态。 请参阅调试重置控制行为(Debug reset control behavior on page B2-86). - CDBGRSTREQ, bit[26]. Debug reset request.

调试复位请求。 该位控制 CDBGRSTREQ 信号。 该位是 RW 还是 RAZ/WI 由实现定义。 上电复位后,该位为 0b0。 - ERRMODE, bit[24].

错误模式。 指示 CTRL/STAT.STICKYERR 字段的重置行为。 0b0:AP 事务设置错误 CTRL/STAT.STICKYERR 和 CTRL/STAT.STICKYERR 保持设置直到明确清除。 0b1:AP 事务上的错误设置 CTRL/STAT.STICKYERR,当输出 FAULT 响应时清除 CTRL/STAT.STICKYERR。

如果 ERRMODE 为 0b1,则 AP 事务上发生的错误可能会通过 FAULT 报告给调试器 响应,但不需要调试器显式清除 CTRL/STAT.STICKYERR。 导致 FAULT 响应的 JTAG-DP 或 SW-DP 事务不成功,并且 CTRL/STAT.STICKYERR 被清除为 0b0,允许尝试将来的事务。 上电复位后,该字段的值为 0b0。 - TRNCNT, bits[23:12]. Transaction counter.

交易计数器。 上电复位后,该字段的值为 UNKNOWN。

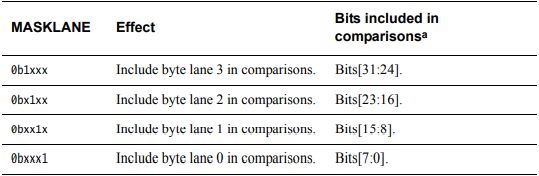

注意:该字段是否实现由 IMPLEMENTATION DEFINED 定义。 MINDP 配置中不支持 TRNCNT。 在 MINDP 配置中,将非零值写入 TRNCNT 或 TRNMODE 的效果是 UNPREDICTABLE。 - MASKLANE, bits[11:8]

对于推送操作,DP 对 AP 写事务中提供的字与目标 AP 地址处的当前字进行逐字节比较。 MASKLANE 字段用于选择要包含在此比较中的字节。 MASKLANE 字段的四位中的每一位对应于要比较的字的四个字节之一。 因此,每一位被称为控制比较操作的一个字节通道。

表 B2-4 显示了 MASKLANE 的位如何控制比较屏蔽。。

- a: 是否包含其他位由 MASKLANE 的其他位决定:为了比较整个字,将 MASKLANE 设置为 0b1111 以包含所有字节通道。 如果 MASKLANE 位为 0b0,则从比较中排除相应的字节通道。

注意:以下内容适用于 MASKLANE 字段: - MASKLANE 仅在传输模式字段 TRNMODE 为 0b01(用于推送验证操作)或 0b10(用于推送比较操作)时才相关。 上电复位后,MASKLANE 的值为未知

- a: 是否包含其他位由 MASKLANE 的其他位决定:为了比较整个字,将 MASKLANE 设置为 0b1111 以包含所有字节通道。 如果 MASKLANE 位为 0b0,则从比较中排除相应的字节通道。

- WDATAERR, bit[7] . Write Data Error.

如果发生以下写入数据错误之一,则该位设置为 0b1: - 写入数据阶段的奇偶校验或帧错误。 - 已被 DP 接受的写入将被丢弃而不提交给 AP。 SW-DP,所有实现:访问是 RO/WI。 要将 WDATAERR 清除为 0b0,请将 0b1 写入 ABORT 寄存器中的 ABORT.WDERRCLR 字段。 如有必要,可以使用 ABORT 寄存器的单次写入来清除多个标志。 清除 WDATAERR 标志后,通常必须重新发送损坏的数据。 上电复位后,WDATAERR 为 0b0. - READOK, bit[6]

在 SW-DP 上,访问是 RO/WI。如果对先前 AP 读取或 RDBUFF 读取的响应是 OK,则该位设置为 0b1。 如果响应不正常,则清零为 0b0。此标志始终指示对最后一次 AP 读取访问的响应。 上电复位后,该位为 0b. - STICKYERR, bit[5]

如果 AP 事务返回错误,则该位设置为 0b1 - STICKYCMP, bit[4]

当在推送比较操作期间发生不匹配或在推送验证操作期间发生匹配时,该位设置为 0b1. - TRNMODE, bits[3:2]

此字段设置 AP 操作的传输模式。- 在正常操作中,AP 交易被传递给 AP 进行处理;- 在推送验证和推送比较操作中,DP 将 AP 写入事务中提供的值与目标 AP 地址中保存的值进行比较。TRNMODE 可以具有以下值之一:- 0b00 正常操作。- 0b01 推送验证模式。- 0b10 推送比较模式。- 0b11 保留。上电复位后,该字段的值为未知. - STICKYORUN, bit[1]

如果启用了溢出检测,则在发生溢出时该位设置为 0b1。SW-DP:访问为 RO/WI。要将 STICKYORUN 清零为 0b0,请将 0b1 写入 ABORT 寄存器中的 ABORT.ORUNERRCLR 字段。 如有必要,可以使用 ABORT 寄存器的单次写入来清除多个标志。在清除 CTRL/STAT.STICKYORUN 后,您必须找出哪个 DP 或 AP 事务引发了导致设置标志的溢出,并重复这些事务 事务计数器指向的事务中的 DP 或 AP。上电复位后,该位为 0b0. - ORUNDETECT, bit[0] 。Overrun detection

0b0 溢出检测被禁用。0b1 启用溢出检测。上电复位后,该位为 0b0

DP8_SELECT (0x08 SW W)

- APSEL=0X00: 表示AHB访问

- APBANKSEL: 选择当前AP的 bank 地址。

DP8_RESEND register 0x08 (SW R)

DPc_RDBUFF register 0x0C (SW R)

NOTE: 电源和复位控制

DP 支持 CTRL/STAT 寄存器中的以下电源和复位控制字段:

- 系统和调试电源控制、

CDBGPWRUPREQ、CDBGPWRUPACK、CSYSPWRUPREQ和CSYSPWRUPACK的控制字段。有关详细信息,请参阅2.1节《系统和调试电源控制行为 System and debug power control behavior》。 - 调试复位控制、

CDBGRSTREQ和CDBGRSTACK的控制字段。有关详细信息,请参阅 2.2节《调试复位控制行为》。

这些控制位可由调试器编程,并将信号驱动到目标系统。

当由 CTRL/STAT 寄存器中的电源和复位控制字段控制时,可以使用 CDBGRSTREQ 字段实现调试逻辑复位,但 CTRL/STAT 不提供任何用于请求系统复位的控制位。然而,调试器的物理接口通常包含一个系统复位引脚 nSRST,它旨在为现有的电源和复位控制器提供提示或激励。有关如何实现系统复位管脚的详细信息,请参见第 B2-88 页的系统复位控制行为。

Arm 建议仅将 CDBGRSTREQ 用作解除锁定系统阻塞的最后手段。 CDBGRSTREQ 可能影响的不仅仅是锁定逻辑,必须小心使用。

nSRST 也可能导致调试逻辑复位,但需要释放调试逻辑复位以允许调试器在保持系统复位的同时对调试逻辑进行编程。

ADI不更换系统电源和复位控制器,ADI规范对系统电源和复位控制器的操作没有任何要求

电源控制要求和操作。

**1 系统和调试电源控制行为 **

System and debug power control behavior

1.1 ADI功率域模型

The ADI power domains model ADI 支持多个电源域,为可断电的调试组件提供支持。实现对三个电源域进行建模:

- Always-on power domain :必须(始终)上电的区域,用于debugger连接device。

必须为调试器上电才能连接到设备的电源域[感谢评论区1层层主建议] - 系统电源域:包括系统组件的电源域。

- 调试电源域:包括整个调试子系统的电源域。

如有必要,可以细分系统和调试电源域。然而,要定义一个简单的调试接口,必须在顶层将设备划分为系统和调试电源域。任何更细粒度的控制都超出了此模型的范围。

在大多数情况下,调试器会启动整个 SoC。但是,如果调试器正在调查电源管理问题,它可能只想启动调试域。为了实现这一目标,SoC 设计人员可能希望将电源控制器映射到一个总线段,当只有调试电源域上电时,ADI 可以访问该总线段。

使用 ADI 时,为了使调试过程正常工作,系统不得在调试会话期间断开 DP 的电源。如果断电,DP 控制器状态将丢失。但是,ADI 旨在允许 ADI 的其余部分和系统在保持对 DP 供电的同时断电和调试。

DP 寄存器位于始终开启的电源域中,位于 DP 的外部接口侧。因此,它们始终可以被驱动,从而能够向系统电源控制器发出上电请求。电源和复位控制位是 DP CTRL/STAT 寄存器的一部分。有关此寄存器中的复位控制位的更多信息,请参见第 B2-86 页的调试复位控制行为。

ADIv6 定义了两对电源控制信号:

CDBGPWRUPREQDP_CTRL_STAT.bit[28] 和CDBGPWRUPACKDP_CTRL_STAT.bit[29]CSYSPWRUPREQDP_CTRL_STAT.bit[30] 和CSYSPWRUPACKDP_CTRL_STAT.bit[31]

1.1.1 CDBGPWRUPREQ & CDBGPWRUPACK

CDBGPWRUPREQ 是从调试接口到电源控制器的信号。该信号请求系统电源控制器完全上电并确保时钟在调试电源域中可用。

CDBGPWRUPACK 是从电源控制器到调试接口的信号。当 CDBGPWRUPREQ 置位时,电源控制器启动调试电源域,然后置位 CDBGPWRUPACK 以确认它已响应请求。

哪些组件在由 CDBGPWRUPREQ 控制的调试电源域中是实现定义的。例如,此域可能包括系统中的所有调试组件,或者可能仅限于排除具有额外功率控制级别的组件。CDBGPWRUPREQ 信号指示调试器需要这些组件的调试资源是可通信的。通信意味着调试器可以访问至少足够的调试资源寄存器,以确定资源的状态。

资源是否处于活动状态由实现定义。电源和时钟控制器必须加电并运行所需数量的域的时钟,以符合来自调试器的此请求,以使资源可通信。

只要 CDBGPWRUPREQ 被断言,电源和时钟控制器就必须遵守它。例如,如果调试电源域中的组件请求断电,则必须针对该电源域内的非调试逻辑模拟该请求,包括具有单个共享域的所有组件。

如果某个组件的某些调试资源不在调试电源域中,则至少该组件的最小调试接口必须上电。如果满足以下要求,则可以从组件的其余部分移除电源:

- 有一些方法可以保存和恢复调试资源的状态。

- 当组件的其余部分未通电时,调试器可以与调试资源通信。

保存和恢复这些资源中保存的值的方法可能包括软件解决方案。如果当从组件的其余部分移除电源时调试资源确实失去了它们的价值,那么调试接口必须包括让调试器发现编程值已经丢失的装置。

CDBGPWRUPACK 是 CDBGPWRUPREQ 请求信号的确认信号。只要 CDBGPWRUPREQ 被断言,CDBGPWRUPACK 就必须被断言。请参见第 B2-84 页的上电请求和确认时间。

1.1.2 CSYSPWRUPREQ and CSYSPWRUPACK

CSYSPWRUPREQ 是从调试接口到电源控制器的信号。该信号请求系统电源控制器完全启动并确保时钟在系统电源域中可用。

CSYSPWRUPACK 是从电源控制器到调试接口的信号。当 CSYSPWRUPREQ 置位时,电源控制器启动系统电源域,然后置位 CSYSPWRUPACK 以确认它已响应请求。

由 CSYSPWRUPREQ 控制的系统电源域中的哪些组件是实现定义的。此域可能包括系统中的所有调试组件,或者可能受到限制,例如排除具有额外功率控制级别的组件,例如实现独立核心的处理器

通电请求控件。

CSYSPWRUPREQ 信号指示调试器需要这些组件的所有调试资源处于活动状态。激活意味着调试资源可以执行其调试功能。一个活跃的资源也是可以交流的。

只要 CSYSPWRUPREQ 被断言,电源和时钟控制器就必须遵守它。

CSYSPWRUPREQ 对由 CDBGPWRUPREQ 控制的调试组件没有影响,因为这些组件在系统电源域中没有调试逻辑。但是,对于某些调试资源位于由 CSYSPWRUPREQ 控制的系统电源域中的组件,必须为该电源域内的非调试逻辑模拟请求。

CSYSPWRUPACK 是 CSYSPWRUPREQ 请求信号的确认信号。只要 CSYSPWRUPREQ 被断言,CSYSPWRUPACK 就必须被断言。请参阅第 B2-84 页的上电请求和确认时间。

当 CSYSPWRUPREQ 被调试器断言时,CDBGPWRUPREQ 也必须被断言。

1.2 电源控制要求和操作

Power control requirements and operation

本节适用于 system 和 debug 域,并使用以下符号:

CxxxPWRUPREQ指的是CSYSPWRUPREQ或CDBGPWRUPREQ。CxxxPWRUPACK是指CSYSPWRUPACK或CDBGPWRUPACK。

本节中描述的所有信号都是高电平有效,因此 assert 表示将信号设为高电平,而 deassert 表示将信号设为低电平。

powerup 请求和确认的操作规则是:

-

调试器不得同时将

CTRL/STAT.CSYSPWRUPREQ设为1、CTRL/STAT.CDBGPWRUPREQ设为0。对这种请求组合的响应是不可预测的。 -

要初始化powerup,DP 必须断言

CxxxPWRUPREQ。- 如果相应的电源域断电或处于低功耗保持状态,则电源控制器必须在检测到

CxxxPWRUPREQ被断言时为域上电。域上电后,控制器必须置位CxxxPWRUPACK。 - 如果在电源控制器检测到

CxxxPWRUPREQ被置位时相应的电源域已经上电,控制器仍必须通过置位CxxxPWRUPACK来响应,即使它不影响电源域。

- 如果相应的电源域断电或处于低功耗保持状态,则电源控制器必须在检测到

-

Arm 强烈建议工具仅在

CDBGPWRUPREQ和CDBGPWRUPACK被断言时才启动 AP 传输。如果CDBGPWRUPREQ或CDBGPWRUPACK为LOW,则任何 AP 传输都可能生成故障响应。 -

DP 通过置低

CxxxPWRUPREQ请求断开域的电源。

当电源控制器接受关闭域的请求时,它会取消断言CxxxPWRUPACK。

注意:电源控制器置低CxxxPWRUPACK,并不表示该域已掉电,仅表示电源控制器已识别并接受断电请求。 -

CxxxPWRUPACK必须默认为LOW状态,并且只有在收到CxxxPWRUPREQ请求时才会变为HIGH。 -

在检测到

CxxxPWRUPREQ的置低后,电源控制器必须正常关闭域,除非从域中移除电源会影响系统操作。例如,如果电源控制器有其他保持电源的请求,它可能会保持对域的电源。 -

通过取消断言

CxxxPWRUPREQ请求断电后,工具必须等到CxxxPWRUPACK为低电平后才能发出新的上电请求。

此要求确保不违反电源控制握手机制。

第 B2-84 页的图 B2-1 显示了电源控制信号的时序

注意:

Arm 强烈建议在时间 T2 和 T3 之间为 CDBGPWRUPREQ 和 CDBGPWRUPACK 发起所有 AP 事务,如图 B2-1 所示。

2 调试复位控制行为

Debug reset control behavior

…

AP Access Port

#define AP_CSW 0x00 // Control and Status Word

#define AP_TAR 0x04 // Transfer Address

#define AP_DRW 0x0C // Data Read/Write

#define AP_BD0 0x10 // Banked Data 0

#define AP_BD1 0x14 // Banked Data 1

#define AP_BD2 0x18 // Banked Data 2

#define AP_BD3 0x1C // Banked Data 3

#define AP_ROM 0xF8 // Debug ROM Address

#define AP_IDR 0xFC // Identification Register

AP0_CSW (Control and Status Word Register) 0x00

Mode: 读取或写入数据访问时的自动地址递增和打包模式。 仅当当前事务完成且没有错误时才会增加。

访问分组数据寄存器 0x10 - 0x1C 时不会执行自动地址递增和打包传输。 在这些情况下,这些位的状态将被忽略。

在 4 KB 地址边界内递增和回绕,例如对于从 0x1000 到 0x1FFC 的字递增。 如果从 0x14A0 开始,则计数器递增到 0x1FFC,回绕到 0x1000,然后继续递增到 0x149C。

0b00 自动增量 关闭

0b01 增量 单次。从相应的字节通道进行一次传输。

0b10 包 增量

AP4_TAR (Transfer Address Register) 0x04~08

APc_DRW (Data Read/Write Register) 0x0C

AP_BDR0-3 (Banked Data Registers 0-3)

使用这些寄存器直接将AHB-AP访问映射到AHB传输,而无需重写AHB- AP传输地址寄存器(TAR)

提供一种通过 DAP 访问直接映射到 AHB 传输的机制,而无需在四个位置边界内重写 TAR,例如 BD0 从 TAR 读取/写入,BD1 从 TAR+4 读取/写入。

如果 DAPADDR[7:4] == 0x0001,因此访问 0x10-0x1C 范围内的 AHB-AP 寄存器,则派生的 HADDR[31:0] 如下:

- 读取模式:从外部地址 TAR[31:4] + DAPADDR[3:0] 读取当前传输的数据值。 对 BD0-BD3 的 DAP 访问不执行自动地址递增。

- 写入模式:将当前传输的数据值写入外部地址 TAR[31:4] + DAPADDR[3:0]。

BANK 传输仅支持 word。 当前忽略非word传输大小,假设 word 访问。

AP_DRAR (Debug ROM Address Register)

IDR (ID Register)

System Debug

- Flash Patch and Breakpoint (FPB) unit to implement breakpoints and code

patches. - Data Watchpoint and Trace (DWT) unit to implement watchpoints, trigger

resources, and system profiling. - Instrumentation Trace Macrocell (ITM) for application-driven trace source that

supports printf style debugging - Embedded Trace Macrocell (ETM) for instruction trace. The processor is

supported in versions with and without the ETM. - AHB-AP

- AHB-AP 是 Cortex-M3 系统的调试访问端口,提供对系统中所有内存和寄存器的访问,包括通过 NVIC 访问的处理器寄存器。系统访问与处理器状态无关。 SW-DP 或 SWJ-DP 访问 AHB-AP。

- AHB-AP 是总线矩阵的主控。 事务是使用 AHB-AP 程序员模型进行的,该模型将 AHB-Lite 事务生成到总线矩阵中。 请参阅 AHB-AP 寄存器的摘要和说明。

AHB-AP

AHB-AP 和 MEM-AP 的联系

The AHB-AP is a Memory Access Port (MEM-AP) as defined in the ARM Debug Interface v5 Architecture Specification. The AHB-AP is an optional debug access port into the Cortex-M3 system, and provides access to all memory and registers in the system, including processor registers through the SCS. System access is independent of the processor status. Either SW-DP or SWJ-DP is used to access the AHB-AP.

AHB-AP是ARM调试接口V5体系结构规范中定义的内存访问端口(MEM-AP)。AHB-AP是进入Cortex-M3系统的可选调试访问端口,并提供对系统中所有内存和寄存器的访问,包括通过SCS的处理器寄存器。系统访问独立于处理器状态。SW-DP或SWJ-DP用于访问AHB-AP。

The AHB-AP is a master into the Bus Matrix. Transactions are made using the AHB-AP programmers model, which generates AHB-Lite transactions into the Bus Matrix.

AHB-AP是 Bus Matrix 的主机。交换是使用 AHB-AP 编程模型进行的,该模型将 AHB-LITE 转换生成BUS Matrix。

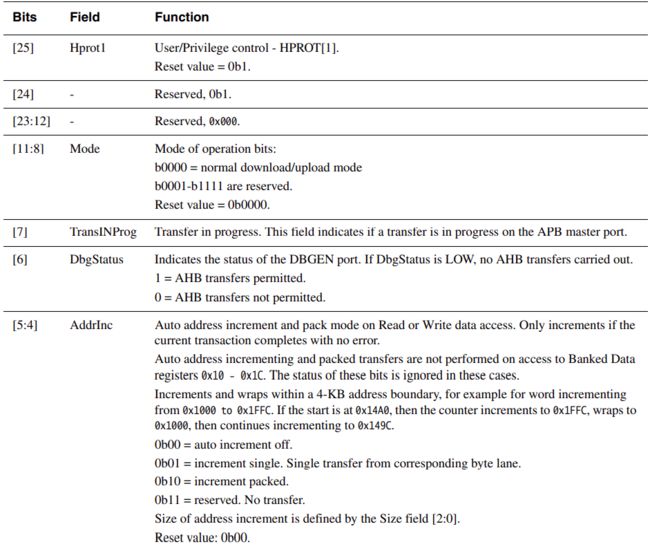

CSW 0x00

0x2300_0012:

[29]=0b1: Debug is master.

[25]=0b1: Resetvalue = 1. User/Privilege

[24] Reserved = 1

[5:4]=0b01: Increment Single, 一次传输

[2:0]=0b010: 32bit

0x2300_0002:

change [5:4]=0b00, 自动增量关闭

- DbgSwEnable, bit[31]

Debug software access enable.调试软件访问使能 - Prot, bits[30:24]

与type类型字段一起使用,以定义总线访问保护控制。调试器可以使用这些字段来指定用于调试访问的标志。 - SDeviceEn, bit[23]

Secure Debug Enabled. 安全调试启用:

0b0 Secure access 禁用.

0b1 Secure access 使能 - ERRSTOP, bit[17]

Errors prevent future memory accesses. This field has one of the following values:

0b0 Memory access errors do not prevent future memory accesses.

0b1 Memory access errors prevent future memory accesses. - ERRNPASS, bit[16]

Errors are not passed upstream. This field has one of the following values:

0b0 Errors are passed upstream.

0b1 Errors are not passed upstream. - Type, bits[15:12]

Used with the Prot field to define the bus access protection control. - Mode, bits[11:8]

Mode of operation of the MEM-AP. This field has one of the following values:

0b0000 Basic mode.

0b0001 Barrier support enabled. - TrInProg, bit[7]

Transfer in progress. This field has one of the following values:

0b0 The connection to the memory system is idle.

0b1 A transfer is in progress on the connection to the memory system - DeviceEn, bit[6]

Device enabled.

This field has one of the following values:

0b0 The MEM-AP is not enabled.

0b1 Transactions can be issued through the MEM-AP. - AddrInc, bits[5:4]

Address auto-increment and packing mode. This field controls whether the access address

increments automatically on read and write data accesses through the DRW register. - Size, bits[2:0]

The size of the data type that is used to access the MEM-AP,

TAR 0x04~08

如果实现包括大物理地址扩展,则偏移量 0xD04 处的字表示传输地址的最低有效字,偏移量 0xD08 处的字表示最高有效字。

如果实现不包括大物理地址扩展,偏移量 0xD04 处的字表示传输地址,偏移量 0x08 处的字为 RES0

Tranfer Address:

- [31:0]. ADDRESS.Reset value = 0x00000000.

- Current transfer address.

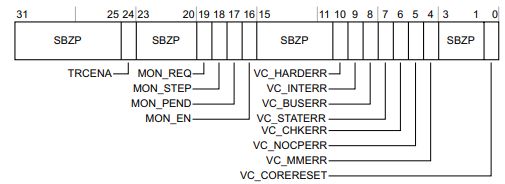

DRW 0x0C

Data Read/Write

- [31:0]. Reset value = 0x00000000

- DATA Write mode:

- data value to write for the current transfer

- DATA Read mode:

- data value to read for the current transfer

- DATA Write mode:

Bandked Data 4 0x10-0x1C

- [31:0] 数据 BD0-BD3。 复位值:0x00000000。

- 提供一种通过 DAP 访问直接映射到 AHB 传输的机制,而无需在四个位置边界内重写 TAR,例如 BD0 从 TAR 读取/写入,BD1 从 TAR+4 读取/写入。

- 如果 DAPADDR[7:4] == 0x0001,因此访问 0x10-0x1C 范围内的 AHB-AP 寄存器,则派生的 HADDR[31:0] 如下:

- 读取模式:从外部地址 TAR[31:4] + DAPADDR[3:0] 读取当前传输的数据值。 对 BD0-BD3 的 DAP 访问不执行自动地址递增。

- 写入模式:将当前传输的数据值写入外部地址 TAR[31:4] + DAPADDR[3:0]。

- BANK 传输仅支持 word。 当前忽略非word传输大小,假设 word 访问。

Debug ROM Address 0xF8

- [31:0] Debug ROM address

- Base address of debug interface

IDR 0xFC

- [31:28] Revision

- This field is zero for the first implementation of an AP design, and is updated

for each major revision of the design.

- This field is zero for the first implementation of an AP design, and is updated

- [27:24] JEP-106 continuation code

- For an ARM-designed AP, this field has value 0b0100, 0x4.

- [23:17] JEP-106 identity code

- For an ARM-designed AP, this field has value 0b0111011, 0x3B.

- [16] Class

- 0b1: This AP is a Memory Access Port

- [15:8] -

- Reserved. SBZ.

- [7:4] AP Variant

- 0x1: Cortex-M3 variant

- [3:0] AP Type

- 0x1: AMBA AHB Bus

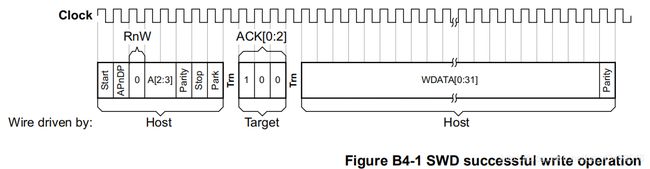

SWD 时序

- 写 OK 时序

烧录器往 DP 或 MEM-AP 寄存器的写操作:

- 读 OK 时序

指烧录器读取 DP 或 MEM-AP 寄存器的数据:

- Wait 时序

DAP没准备好,响应WAIT给HOST,此次通讯结束。

- Fault 时序

DAP出错,响应FAULT给HOST,此次通讯结束。

NOTE

1. 请求

主机 HOST 发出的请求由 8bit 组成:

| bit | name | note |

|---|---|---|

| Bit0 | Start | 固定为 1。 |

| Bit1 | APnDP | 0表示访问 DP 寄存器,1 表示访问 MEM-AP 寄存器。 |

| Bit2 | RnW | 0表示写请求,1表示读请求。 |

| Bit[4:3] | A[3:2] | 地址值,存放 DP/AP 寄存器的地址。 |

| Bit5 | Parity | 用于表示由{APnDP,RnW, A[2:3]}组成这四位数的奇偶总个数。 |

| Bit6 | Stop | 固定为0。 |

| Bit7 | Park | 固定为1。 |

A2/A3两位,给出 DP 或 AP 寄存器地址的 A[3:2] 地址字段:

- 对于 DPACC 访问,被寻址的寄存器取决于 A[3:2] 的值,如果 A[3:2]==0b01,则取决于 SELECT 中保存的值。 DPBANKSEL。 有关详细信息,请参阅第 B2-51 页的 DP 架构版本 3 (DPv3) 地址映射。

- 对于 APACC 访问,被寻址的寄存器取决于 A[3:2] 值和 SELECT.{APSEL,APBANKSEL} 中保存的值。 有关寻址的详细信息,请参见:

- C2-192 页的 MEM-AP 程序员模型,用于访问 MEM-AP 寄存器

- JTAG-AP 程序员模型在 C3-245 页上,用于访问 JTAG-AP 寄存器。

比如 DP_Select 的寄存器地址为 0x08(即 0b1000),显然A[2:3]就为 01。

2. 响应

Target返回的ACK值由3bit组成:

| ACK | note |

|---|---|

| ACK[0:2]==001 | FAULT |

| ACK[0:2]==010 | WAIT |

| ACK[0:2]==100 | OK response |

3. 数据

由32bit有效数据 + 1bit数据的奇偶校验位组成

MCU连接过程

1. SWD初始化

- a. 初始化IO口,SWCLK和SWIO设置为输出模式,保持SWDIO=1,保证Host连续发送至少50个“1”,使得Target进行Line Reset。

- b. 发送JTAG to SWD命令,0x79、0xE7两个byte(在ARM-Debug_Interface官方文档中可以查到),随后再发送一次line reset操作。

- c. 至少发送两个Idle信号,保持 SWDIO=0。

- d. 读取Chip ID,从而完成SWD初始化操作。

注意:此时只能访问DP寄存器组,AP寄存器组还无法访问。

2. 解锁 AP

- a. 写入

DP_CTRL/STAT寄存器(addr=0x04)数据为0x50000000(第28位CDBGPWRUPREG和第30位CSYSPERUPREQ),开启Debug Port及其时钟. - b. 写入

DP_SELECT寄存器(addr=0x08)数据为0x000000F0,AP_bank:0xF - c. 读取

AP_IDR寄存器(addr = 0xFC)识别数据并验证。读取IDR寄存器的数值时,需要两次,第一次是dummy read,第二次读取到的才是正确的数据。(第二次也可以读RDBUFF寄存器) - d. 写入

DP_SELECT寄存器数据为0x00000000,bank:0x0 - e. 写入

AP_CSW寄存器数据为0x00000002,data_size:32bit

Size:访问MEM-AP的数据类型的大小

其中:寄存器的数据是32bit0b010,编程写入Flash的数据是16bit0b001。

MCU 读写操作

如果想要 写入/读出 MCU内部Flash的数值,需要用到两个AP寄存器

- TAR (The Transfer Address Register)

- DRW (The Data Read/Write Register)

-

写操作

1)在TAR_W寄存器中写入要访问的内存地址数值 (addr = 0x08000000)

2)在DRW_W寄存器中写入要往内存中写入的数据 (data = 0x12345678) -

读操作

1)在TAR_W寄存器中写入要访问的内存地址数值 (addr = 0x08000000)

2)从DRW_R寄存器中读取要访问的内存中存放的数据

3)从DP_RDBUFF寄存器中读取数据 or 从AP_DRW_R寄存器中读取数据

注意

由于读取AP寄存器的特殊性,当读取AP寄存器时,返回的数据是上一次传输的值。也就是说,有两种方式可以得到正确的 AP 寄存器的值。

- 发送两次读

AP_DRW寄存器的操作 - 发送一次读

AP_DRW寄存器的操作(读取上一周期的数据),再发送一次读DP_RDBUFF寄存器的操作(读取自己需要的数据)

总的来说,读写DP寄存器没有迟滞,不需要读写两次。读取AP寄存器,有迟滞,第一次读AP,是上一周期的值,第二次读AP才是想要的值。写AP寄存器,没有迟滞,如TAR,DRW只需要写一次即可写进去。

原文链接

MM32-LINK 测试(MT304)

ARM cortex -M0

理论值 - 0x0BB1_1477

| Name | CPUID |

|---|---|

| MT304 | 0x412F_C231 |

| MM0020 | 0x410C_C200 |

1. SWD Connect: read DP_IDCODE

- LineReset(30+30)

- JTAG2SWD

- LineReset(30+30)

- 16b1110_1110_1110_1110(0xEEEE LSB)

- LineReset(30+30)

- R DP_IDCode(DP0)

- OK + 0x2ba01477

- delay 200us

2. Set DP_CTRL/STAT PWR UP

- R DP_CTRL/STAT(DP4)

- OK+0xF000_0040

- W DP_ABORT(DP0)

- OK+0x0000_001e

- W DP_CTRL/STAT(DP4)

- OK+0x5000_0000

- W DP_SELECT(DP8)

- OK+0x0000_0000

- W DP_ABORT(DP0)

- OK+0x0000_001e

3. Read CPUID(0xE000_ED00)

- W DP_SELECT

- OK+0x0000_0000

- W AP_TAR(AP4)

- OK+0xE000_ED00(NVIC_CPUID)

- W AP_CSW(AP0)

- OK+0x2300_0012

- R AP_DRW(APc)

- Wait

- R AP_DRW(APc)

- OK+0xFFFF_FFFF

- R DP_RDBUFF(DPc)

- OK+0x412F_C231

- delay 120us

4. Unknow: Read from 0xE000_1028/38/48/58

- W DP_ABORT(DP0)

- OK+0x0000_001E

- W DP_SELECT(DP8)

- OK+0x0000_0000

- W AP_TAR(AP4)

- OK+0xE000_1028 / 0xE000_1038 / 0xE000_1048 / 0xE000_1058

- W AP_CSW(AP0)

- OK+0x2300_0012

- W AP_DRW(APc)

- OK+0x0000_0000

- R DP_RDBUFF(DPc)

- OK+0x412F_C231(Last Time) ??ERROR

- W DP_ABORT(DP0)

- OK+0x0000_001E

5. DBG_HCSR(0xE000_EDF0) = 0xA05F_0003, Halt CPU, DBG_EN

- W DP_SELECT(DP8)

- OK+0x0000_0000

- W AP_TAR(AP4)

- OK+0xE000_EDF0

- W AP_CSW(AP0)

- OK+0x2300_0002

- W AP_DRW(APc)

- OK+`0xA05F_0003`

- R AP_DRW(APc)

- WAIT

- R AP_DRW(APc)

- OK+0x412F_C231(last time)

- R AP_DRW(APc)

- OK+0x0103_0003

- W DP_ABORT(DP0)

- OK+0x0000_001E

- W DP_SELECT(DP8)

- OK+0x0000_0000

- W AP_TAR(AP4)

- OK+0xE000_EDF0

- W AP_CSW(AP0)

- OK+0x2300_0012 // something change:

- R AP_DRW(APc)

- Wait

- R AP_DRW(APc)

- OK+0x0003_0003

- R DP_RDBUFF(DPc)

- OK+0x0003_0003

- W DP_ABORT(DP0)

- OK+0x0000_001E

- W DP_SELECT(DP8)

- OK+0x0000_0000

7. DBG_EMCR(0xE000_EDFC) = 0x0100_0001, Catch Reset & Trace

- W AP_TAR(AP4)

- OK+`0xE000_EDFC`

- W AP_CSW(AP0)

- OK+`0x2300_0012`

- W AP_DRW(APc)

- OK+`0x0100_0001`

- send 0x0000( 8 clock no used)

- R DP_RDBUFF(DPc)

- OK+0x0003_0003

- send ack(3clk) + send 8clk(0x0000) + send 8clk(0x0000)

- W DP_ABORT(DP0)

- OK+0x0000_001E

8. DBG_AIRCR(0xE000_ED0C) = 0x05FA_0004, SYS_RST_REQ

- W DP_ABORT(DP0)

- OK+0x0000_001E

- W DP_SELECT(DP8)

- OK+0x0000_0000

- W AP_TAR(AP4)

- OK+0xE000_ED0C

- W AP_CSW(AP0)

- OK+0x2300_0012

- W AP_DRW(APc)

- OK+`0x05FA_0004`

- later send 0x0000

9. nRST = 0. dalay xxms

- 418 us later.

- R AP_DRW(APc)

- OK+0x0003_0003

- send 3 ack clock, but not used

- **18 ms later.**

10. nRST = 1. delay 20ms

11. read DBG_HCSR(0xE000_EDF0) 3times

- W DP_ABORT(DP0)

- OK+0x0000_001E

- W DP_SELECT(DP8)

- OK+0x0000_0000

- W AP_TAR(AP4)

- OK+0xE000_EDF0

- W AP_CSW(AP0)

- OK+0x2300_0012

- R AP_DRW(APc)

- WAIT

- R AP_DRW(APc)

- OK+0x0003_0003 - second time: 0x0203_0003 - third time: 0x0003_0003

- R DP_RDBUFF(DPc)

- OK+0x0203_0003 - second time: 0x0003_0003 - third time: 0x0003_0003

12. DBG_EMCR(0xE000_EDFC) = 0x0100_0000, Trace(3 times)

- W DP_ABORT(DP0)

- OK+0x0000_001E

- W DP_SELECT(DP8)

- OK+0x0000_0000

- W AP_TAR(AP4)

- OK+0xE000_EDFC

- W AP_CSW(AP0)

- OK+0x2300_0012

- W AP_DRW(APc)

- OK+0100_0000

- send 8clk(0x0000) / R AP_DRW(APc)

- WAIT / OK+0x0100_0000

- R DP_RDBUFF(DPc)

- OK+0x0003_0003