【FPGA实验】基于DE2-115平台的数码管实验1

文章目录

-

- 一.实验任务

- 二.闪烁数码管

-

- ①设计1s计时器模块

- ②设计数码管模块

- ③设计顶层模块

- ④查看RTL门级电路

- ⑤硬件测试

- 三.循环显示的“HELLO”

-

- ①设计计数器模块

- ②设计数码管显示模块

- ③设计顶层模块

- ④查看RTL门级电路

- ⑤硬件测试

一.实验任务

1.闪烁数码管

在HEX0上连续循环地显示数字0~9,每秒刷新一次显 示。使用计数器产生1 s的时间间隔,这个计数器的时钟由 DE2-115平台上的50

MHz时钟提供。注意:这个设计中只允 许使用DE2-115平台上的50 MHz时钟,而不允许使用其他时

钟,并保证所有的触发器都直接使用这个50 MHz时钟。

2.循环显示的“HELLO”

设计一个电路实现在HEX7~HEX0上循环显示 “HELLO”,使所有字母从右向左移动,每秒移动一次, 移动模式如表6.5所示。

二.闪烁数码管

该实验使用了1个数码管HEX0,每一秒更换数字显示0~9,采用平台的50MHZ时钟。

①设计1s计时器模块

time_count.v

module time_count(

input wire clk, //时钟,50MHZ

input wire rst_n, //复位信号,下降沿有效,negative

output wire sec_1//1s输出一个脉冲信号

);

parameter MAX_NUM = 26'd49_999_999;//记最大数1s,50_000_000次

reg [25:0] cnt_1;//计数寄存器

reg sec_1_r;

//1s计时器

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_1 <= 26'd0;

end

else if(cnt_1 == MAX_NUM)begin

cnt_1 <= 26'd0;

end

else begin

cnt_1 <= cnt_1 + 1'd1;

end

end

//1s脉冲信号

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

sec_1_r <= 1'b0;

end

else if(cnt_1 == MAX_NUM)begin

sec_1_r <= 1'b1;

end

else begin

sec_1_r <= 1'b0;

end

end

assign sec_1 = sec_1_r;//当右边改变,立马赋值给左边 assign和always并行

endmodule

②设计数码管模块

查看平台手册:

该平台不同于前面使用的EP4CE6F17C8芯片,这里不涉及位选信号,每个段选信号都有一个单独的引脚。

设计代码如下:

seg_led_static.v

module seg_led_static(

input wire clk,//时钟

input wire rst_n,//复位

input wire sec_1,//1s脉冲信号

output wire [6:0] seg//7位数码管段选信号

);

reg [3:0] value;

reg [6:0] seg_r;

//0~9计数功能

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

value <= 4'd0;

end

else if(sec_1)begin

if(value < 4'd9)begin

value <= value + 1'd1;

end

else begin

value <= 4'd0;

end

end

else begin

value <= value;

end

end

//数码管译码功能,组合逻辑

always@(*)begin

case(value)

4'd0 : seg_r = 7'b100_0000;

4'd1 : seg_r = 7'b111_1001;

4'd2 : seg_r = 7'b010_0100;

4'd3 : seg_r = 7'b011_0000;

4'd4 : seg_r = 7'b001_1001;

4'd5 : seg_r = 7'b001_0010;

4'd6 : seg_r = 7'b000_0010;

4'd7 : seg_r = 7'b111_1000;

4'd8 : seg_r = 7'b000_0000;

4'd9 : seg_r = 7'b001_0000;

default: seg_r = 7'b100_0000;

endcase

end

assign seg = seg_r;

endmodule

③设计顶层模块

top_seg_led.v

module top_seg_led(

input wire clk,

input wire rst_n,

output wire [6:0] seg

);

wire sec_1;//将两个模块的信号连接起来

//推荐变量名传值,还有位置传值

time_count inst_time_count(

.clk (clk ),//时钟,50MHZ

.rst_n (rst_n ),//复位信号,下降沿有效,negative

.sec_1 (sec_1 ) //1s输出一个脉冲信号

);

seg_led_static inst_seg_led_static(

.clk (clk ),//时钟

.rst_n (rst_n ),//复位

.sec_1 (sec_1 ),//1s脉冲信号

.seg (seg ) //7位数码管段选信号

);

endmodule

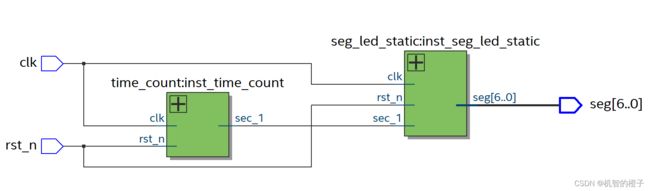

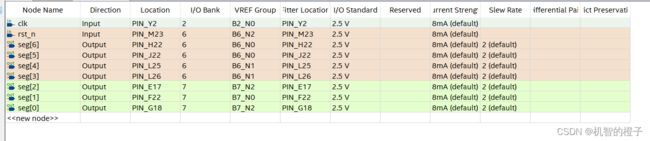

④查看RTL门级电路

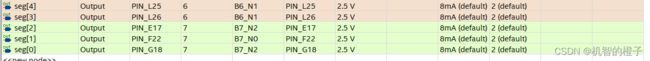

⑤硬件测试

三.循环显示的“HELLO”

思路,定义一个56位的寄存器,将8个数码管按照1~5显示OLLEH,6到8不显示保存在寄存器中,利用移位实现HELLO的移动

①设计计数器模块

同上

②设计数码管显示模块

seg_led_static.v

module seg_led_static(

input wire clk,//时钟

input wire rst_n,//复位

input wire sec_1,//1s脉冲信号

output wire [55:0] seg//56位数码管段选信号

);

reg [55:0] seg_r;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

seg_r <= 56'd72057562107864000;

end

else if(sec_1)begin

seg_r <= {seg_r[48:0],seg_r[55:49]};

end

else begin

seg_r <= seg_r;

end

end

assign seg = seg_r;

endmodule

③设计顶层模块

top_seg_led.v

module top_seg_led(

input wire clk,

input wire rst_n,

output wire [55:0] seg

);

wire sec_1;//将两个模块的信号连接起来

//推荐变量名传值,还有位置传值

time_count inst_time_count(

.clk (clk ),//时钟,50MHZ

.rst_n (rst_n ),//复位信号,下降沿有效,negative

.sec_1 (sec_1 ) //1s输出一个脉冲信号

);

seg_led_static inst_seg_led_static(

.clk (clk ),//时钟

.rst_n (rst_n ),//复位

.sec_1 (sec_1 ),//1s脉冲信号

.seg (seg ) //7位数码管段选信号

);

endmodule

④查看RTL门级电路

⑤硬件测试

下载测试: