低功耗IC后端培训 | 盘点Power Switch Cell在实际项目中应用注意事项

下面直接进入今天的技术干货分享——全面盘点power gating cell在数字IC后端实现中的各种注意事项。

什么是Power Gating?

随着工艺制程越做越小和芯片规模越来越大,芯片的leakage的比重越来越高,数字后端实现时就得考虑leakage的优化。而leakage优化很重要的一个手段就是power gating。

Power Gating字面意思就是对电源Power进行控制,即通过切断电源网络的方式来节省leakage。

之所以能这么干,是因为芯片中有的模块并不需要一直处于工作的状态。所以我们仅仅需要在模块需要工作的时候给它供上电即可。这个可以通过我们预先设置的控制信号来做控制。

Power Gating Cell的类型

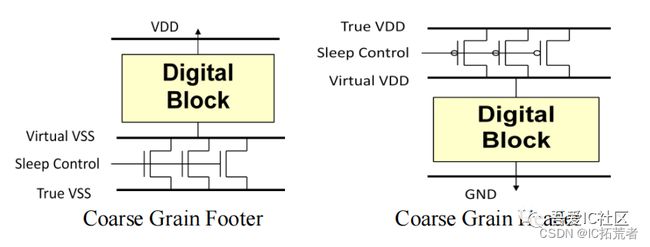

Foundary工艺库中提供了两种类型的Power gating cell。一种是Coarse Grain Footer(Footer类型),另外一种是Coarse Grain Header(Header类型)。Footer类型是通过开关VSS来实现电源网络VSS到Virtual VSS的开启与关闭。而Header类型则是通过开关VDD来实现电源网络VDD到Virtual VDD的开启与关闭。

实际项目中大都是采用Header类型的Power Gating Cell。

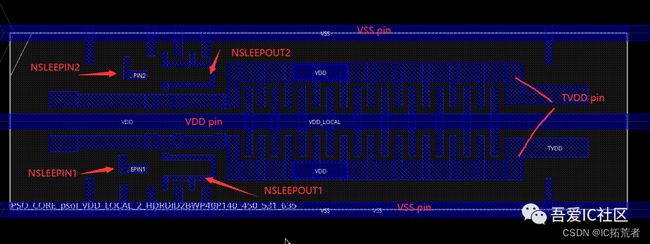

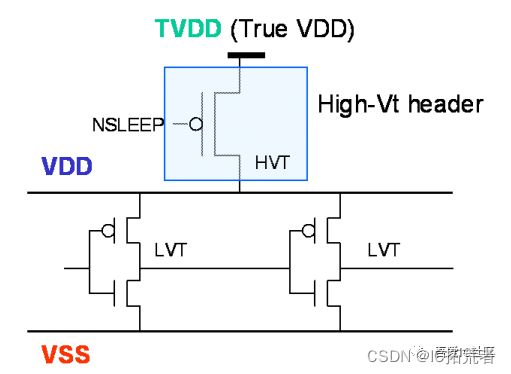

下图为咱们社区IC训练营项目Cortexa7core中使用的Power gating cell(MTCMOS)。显然它是一个Header类型的Power Switch Cell。当系统判断需要开启这个模块时,就会把TVDD到VDD这个电源网络接通,否则就会关闭。

何时加Power Gating Cell?

如果当前模块需要做Power gating,我们通常说这个模块是一个Power Domain(简称PD)。对于大型SOC芯片来说,可能会包含几百个PD。

当项目告诉你这个设计需要做Power Domain时,我们后端实现时就需要在这个设计的floorplan阶段加入MTCMOS。

Power Gating Cell的数量

通常我们在加power gating cell之前需要估算下当前设计能接受的IR drop百分比,然后计算出所需要的数量(典型的欧姆定律,power gating cell的电阻已知)。具体计算过程之前分享过好几次了,这里就不再详细说明。如果还有不懂,可以移步小编知识星球上查阅。

我们为了得到一个更好的IR drop结果,是不是可以通过多加power gating cell来实现呢?理论上肯定是可以的。但是实际项目中并非越多越好,主要原因有以下几点。

- 每个power gating cell的面积较大

加的power gating cell越多就会占用更多的有效面积,留给标准单元的面积就会更少(固定模块面积的情况下)。

- 每个power gating cell都有leakage

因为即便MTCMOS是处于关断状态,它还存在一定的leakage。咱们训练营项目所用的Header类型MTCMOS的结构如上图所示。所以这个leakage来源是上面那个High-VT的PMOS管。- 每个power gating cell都需要有TVDD的电源网络(占用更多绕线资源)

- 带power gating cell的设计,ir drop会更大

Power Gating Cell加入的pattern

目前主流有两种加法,分别是Column(line)和Stagger样式,具体如下图所示。这两种所加的Power switch cell数量是一样的,区别在于前者是按照固定的pitch来均匀摆放,而后者是按交错的方式来摆放。

下图为咱们社区训练营项目的Power switch cell的加法。对于设计中带Macro的模块,我们需要如何来给macro加power switch cell呢?

控制信号串链方式

T28工艺库中提供了单链和双链两种类型的Power switch cell。目前大家都是使用双链类型的,即这个Power switch cell的开关控制信号有Nsleep1in,Nsleep1out,Nsleep2in和Nsleep2out这四个控制信号。

官方也是强烈建议使用双链结构的MTCMOS。为了防止开启MTCMOS时产生较大的power glitch,foundary建议上电时先开启Nsleep2这条链,即先开启小管子再开大管子。

将整个设计中所有Power switch cell控制信号按照上面的要求串好链之后的效果如下图所示。

但实际项目中为了防止上电时有较大的rush current,我们一般还会使用多条nsleep chain来串完所有的power switch cell。

【思考题】串链后Power Switch Cell Nsleep chain存在max transition violation,能否通过插普通buffer来解决?

好了,今天的内容分享就到这里。另外,因为公众号更改推送规则,小编分享的每篇干货不一定能及时推送给各位。为了避免错过精彩内容,请关注星标公众号,点击“在看”,点赞并分享到朋友圈,让推送算法知道你是社区的老铁,这样就不会错过任何精彩内容了。

如果你想和小编有更进一步的沟通交流的机会,欢迎加入小编知识星球,让我们一起学习成长,共同进步。相信在这里能让你成就一个更完美的自己。

微信号:ic-backend2018