三、4【Verilog HDL】基础知识之模块和端口

参考书籍:《Verilog HDL 数字设计与综合》第二版,本文档为第四章的学习笔记。

目录

学习目标

4.1 模块

4.2 端口

4.2.1 端口列表

4.2.2 端口声明

4.2.3 端口连接规则

4.2.4 端口与外部信号的连接

1、顺序端口连接

2、命名端口连接

4.3 层次命名

学习目标

- 清楚模块中的组成部分

- 模块的端口列表声明

- 模块实例化及其端口信号连接

- 标识符层次

4.1 模块

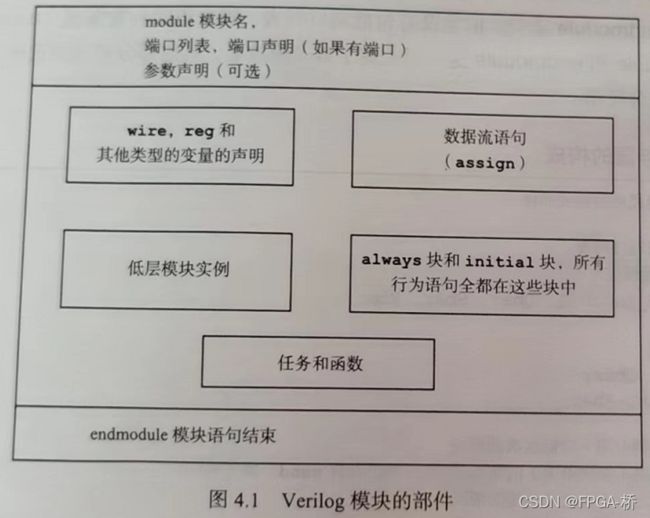

module开始,endmodule结束。模块内部5个组成部分:变量声明、数据流语句、低层模块实例、行为语句、任务和函数。

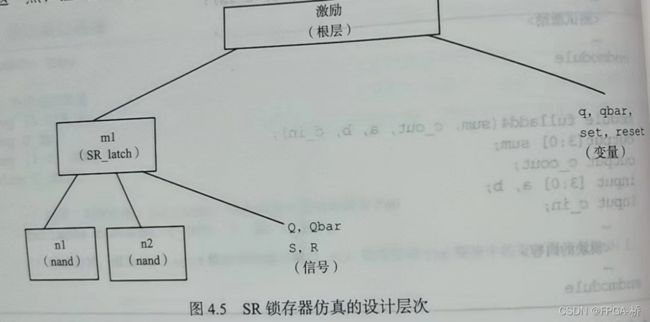

例子说明:通过模块实现SR锁存器

输入输出真值表:

| 端口信号信息 | |||

| 信号 | 位宽 | 类型 | 功能描述 |

| Sbar | 1bit | input | 输入信号1 |

| Rbar | 1bit | input | 输入信号2 |

| Q | 1bit | output | 输出信号1 |

| Qbar | 1bit | output | 输出信号2 |

| 端口真值表 | |||

| 输入(input) | 输出(output) | ||

| Sbar | Rbar | Q(n) | Qbar(n) |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | Q(n-1) | Qbar(n-1) |

数据流(assign)语句和行为语句(always和initial)

module SR_latch(Q, Qbar, Sbar, Rbar);

//端口说明

input Sbar, Rbar;

output Q, Qbar;

nand n1(Q, Sbar, Qbar);

nand n2(Qbar, Rbar, Q);

endmodule

///*************激励块

module tb_SR_latch();

reg set, reset;

wire q, qbar;

always #10 set <= {$random} % 2;

always #10 reset <= {$random} % 2;

SR_latch SR1(q, qbar, ~set, ~reset);

initial begin

$timeformat(-12, 0, "ps", 6);

$monitor($time, "set=%b, reset=%b, q=%b\n" , set, reset, q);

end

endmodule

4.2 端口

即模块与外界环境交互的接口,又可以成为终端。

4.2.1 端口列表

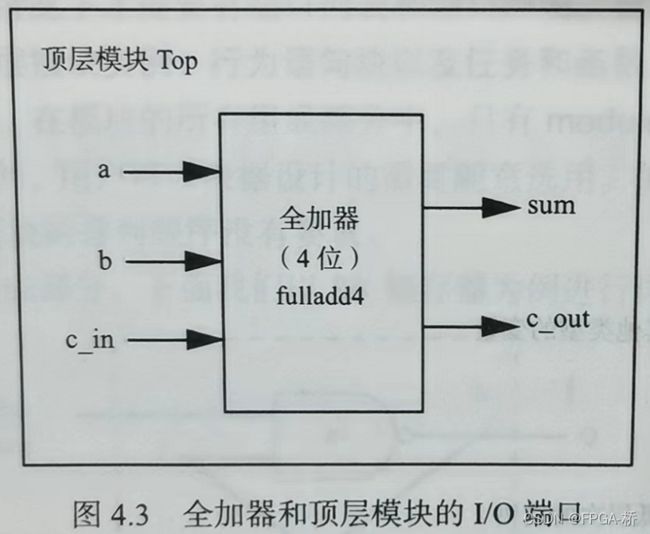

module fulladd4(sum, c_out, a, b, c_in); //()内即模块的端口列表

module Top; //由于Top是激励模块,所以没有端口列表4.2.2 端口声明

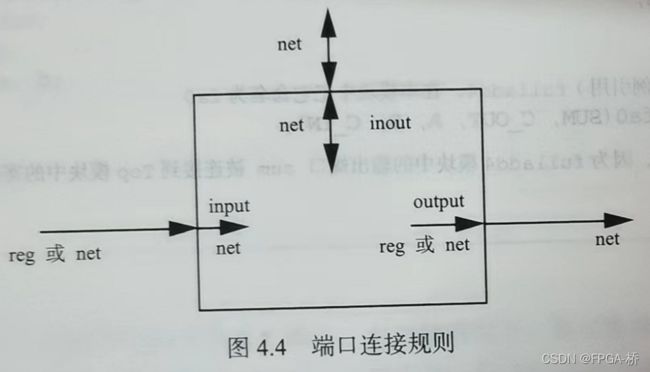

input:输入端口;output:输出端口;inout:输入输出双向端口

module fulladd4(sum, c_out, a, b, c_in);

//端口声明

input [3:0] a,b;

input c_in;

output [3:0] sum;

output c_out;

endmodule

//ANSI C风格的端口声明

module fulladd4(

//端口声明

input wire [3:0] a,b,

input wire c_in,

output reg [3:0] sum,

output reg c_out

);

endmodule4.2.3 端口连接规则

4.2.4 端口与外部信号的连接

1、顺序端口连接

在模块实例化时,对于端口列表,按照顺序一次对应。

module SR_latch(Q, Qbar, Sbar, Rbar);

SR_latch SR1(q, qbar, ~set, ~reset);

2、命名端口连接

SR_latch SR2(.Q(q), .Qbar(qbar), .Sbar(sbar), .Rbar(reset));

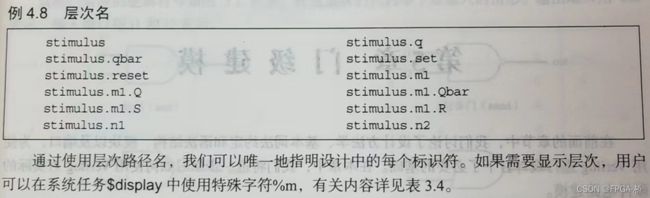

4.3 层次命名

层次名由一连串使用“ . ”分隔的标识符组成,每个标识符代表一个层次,这样可以通过指定层次名对每个标识符进行访问。