【操作系统复习】第5章 存储器管理 2

分页存储管理方式

页号P

◆12-31位:20位

◆地址空间最多允许有1M(2 20)页

位移量W(页内地址)

◆0-11:12位

◆每页大小为4KB (2 12)

对某特定机器,地址结构是一定的。

若给定一个逻辑地址空间中的地址为A,页面的大小为L,则页号P和页内地址d可按下式求得

页表

系统为每个进程建立了 一张页表。记录在该进程的PCB中。

逻辑地址空间内的所有页,依次在页表中有一表项,记录相应页在内存中对应的物理块号。

页表的作用:实现从页号到块号的地址映射。

地址转换

1. 地址转换:实现从逻辑地址到物理地址的转换,将逻辑地址中的页号转换为物理地址中的块号(页内地址和块内物

理地址一一对应)

- 映射表:借助页表完成(页面映射表的作用就是实现从页号到物理块号的变换)

1. 逻辑地址:以十六进制、八进制、二进制的形式给出

2. 页号和页内地址分离:按页的大小分离出页号和页内地址,将位移量直接复制到内存地址寄存器的低位部分

3. 页表查表:以页号查页表,得到对应页装入内存的块号,并将块号,转换成二进制数填入地址寄存器的高位部分,从而形成内存地址(页号+页内地址->块号+页内地址)

页表寄存器:整个系统中设置一个页表寄存器,存放页表在内存的始址和页表的长度。当调度某进程执行时,将PCB中的页表的始址和长度装入页表寄存器中

动态地址变换机构:执行内存访问指令时,逻辑地址至物理地址的地址变换过程由硬件(动态地址变换机构DAT)实现

页表被保存在主存中

页表寄存器(Page-table register,PTR)指向页表的起始地址和长度

在这个机制中,每一次的数据/指令存取需要两次内存访问,一次是访问页表,一次是访问数据/指令

解决两次访问的问题,是采用小但专用且快速的硬件缓冲,这种缓冲称为转换表缓冲器(translation look aside buffer,TLB)或联想寄存器

具有快表的地址变换机构

1. 访问内存性能降低:每执行一条指令,至少要访问内存两次。一次是到内存中访问页表;一次是形成物理地址后,到该内存单元中取指令或数据。这样,存取速度降低一倍,将会影响整个系统的使用效率

2. 快表:存放页表部分内容的快速存储器称为联想寄存器,联想寄存器中存放的部分页表称为“快表”

3. 联想寄存器解决方案:为提高速度,增设联想寄存器(也称快表,可按内容并行查找的快速寄存器,比内存贵,容量小),将作业中最常用的页块号置入高速缓存,提高查表速度,一般说,快表若含有8-16项,就可达到较高命中率

引入快表后的有效访问时间EAT

查找快表需要的时间为 λ

假设访问内存一次需要的时间为tEAT = t + t = 2t (基本分页存储系统中)

命中率—在联想寄存器中找到页号的百分比,比率与联想寄存器的大小有关,假设为a

引入快表的有效访问时间EAT = λ * a + (t + λ)(1 – a) + t

页表结构

对页表所需要的内存空间,采用离散分配方式

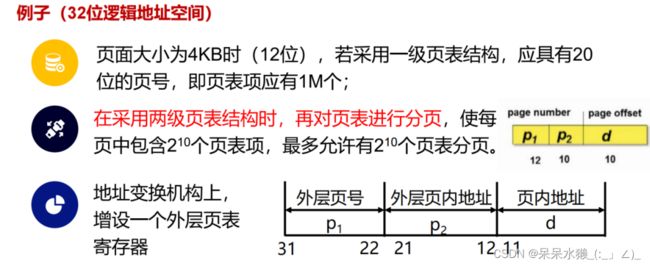

两级页表

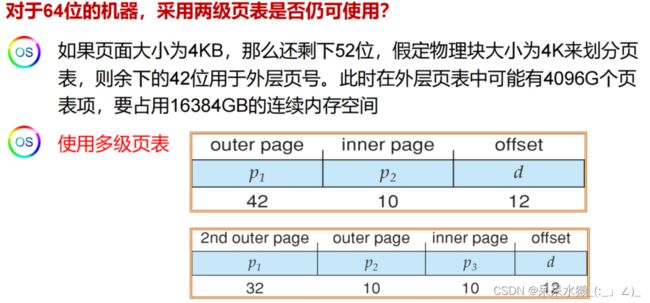

多级页表

反置页表

为减少页表占用的内存空间,引入反置页表,一个系统一张页表对每个内存物理块设置一个条目。

每个条目保存在真正内存位置的页的虚拟地址,以及包括拥有这个页的进程的信息。

减少了需要储存每个页表的内存,但是当访问一个页时,增加了寻找页表需要的时间

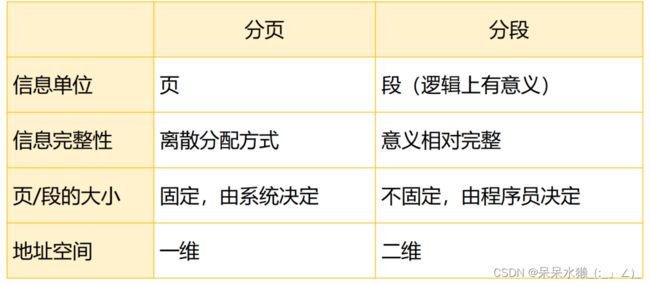

分段存储管理方式

引入目的:为了满足用户(程序员)在编程和使用上多方面的要求

方便编程、信息共享、信息保护、动态链接、动态增长

在分段存储管理方式中,作业的地址空间被划分为若干个段,每个段定义了一组逻辑信息

每个段都有自己的名字,通常用一个段号来代替段名,每个段都从0开始编址,并存储在一段连续的地址空间内

段的长度由相应的逻辑信息组的长度决定,因此各段长度不等

分段的一个突出优点,是易于实现段的共享,即允许若干个进程共享一个或多个分段,且对段的保护也十分简单易行

在分页系统中,虽然也能实现程序和数据的共享,但远不如分段系统来得方便

可重入代码(纯代码):一种允许多个进程同时访问的代码。

段页式存储管理方式

基本原理:

➢ 分段和分页原理的结合,即先将用户程序分成若干段,再把每个段分成若干个页,并为每个段赋予一个段名

优点:

➢ 既有分段系统的便于实现、可共享、易于保护、可动态链接;

➢ 又能像分页系统,很好地解决内存的外部碎片问题。