【设计】】MOS管衬底电位接法|PMOS、NMOS衬底连接-KIA MOS管

参考:请问什么是nwell和P substrate??

请问什么是nwell和P substrate??

请问什么是nwell和P substrate??

在CMOS的IC设计,如NPN三极管中经常看到请问什么是nwell和P substrate的说法,请问倒底指的是什么,能详细介绍一下吗,谢谢

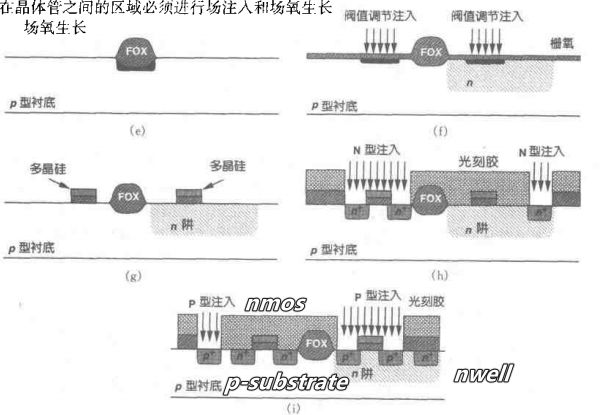

通常,我们都用P型基体晶圆在制作IC。对于普通的CMOS工艺而言,NMOS 管可以直接做在P型衬底的有源区内,而PMOS管则必须做在N Well的有源区内。CMOS工艺还可分类为单阱工艺和双阱工艺,前提都是基于P型衬底。

三极管的实现,也是在阱中通过适当的PN结偏置所形成。

参考:MOS管衬底电位接法|PMOS、NMOS衬底连接-KIA MOS管

NMOS-P-SUB

P-SUB工艺,NMOS 的衬底都是一样的,都是P-SUB,所以不可以将源极和衬底接一块,不然通过衬底短接会影响其他NMOS的特性,因此NMOS的衬底只能接GND(低电位);

P-SUB工艺,PMOS管的N衬底都是单独的,因此可以将源极和衬底接一块来减小衬偏效应;

Deep Nwell,是在PSUB工艺情况下,对NMOS管可以采取的一种隔离方式,底部是deep nwell,周围是nwell形成的一个环,来隔离共衬底引起的噪声干扰。

PMOS-Nwell

N-WLL工艺,PMOS的衬底都是一样的,都是N-WELL,因此不可以将源极和衬底接一块,不然通过衬底短接会影响其他PMOS的特性,因此PMOS的衬底只能接VDD(高电位);

N-WELL工艺,NMOS管的P衬底都是单独的,因此可以将源极和衬底接一块来减小衬偏效应;

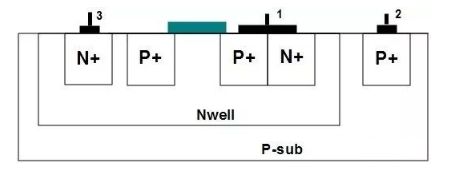

在工艺上表现为器件的衬底接触点如PMOS器件在工艺上的剖面图,如图所示3为PMOS的衬底电位的接触点,CMOS工艺PMOS器件是做在Nwell里,所以PMOS的衬底guard ring使用的是NWring.

接法

在schematic原理图中搭建电路时,所有pmos的衬底需要接VDD,所有nmos的衬底需要接VSS。

在layout版图中,VDD供电时,选择的通孔类型的M1_NW,因为PMOS器件做在N阱中。

相对应,VSS供电选择的通孔类型为M1_SUB。

浮动电源轨里面模块I_bias_gt的demos衬底sub端和isolate都接SW吗。

三、分析:P衬底

为什么现在的CMOS工艺一般都是用P衬底而不是N衬底

参考:为什么现在的CMOS工艺一般都是用P衬底而不是N衬底

为什么CMOS工艺采用P衬底,而不用N衬底?

这主要从两个方面来考虑:

一个是材料和工艺问题;

另一个是电气性能问题。

NMOS管迁移率高,阈值电压绝对值小,要求工作电压低有利于低功耗。

NMOS和PMOS工作原理 P沟道MOS晶体管的空穴迁移率低,因而在MOS晶体管的几何尺寸和工作电压绝对值相等的情况下,PMOS晶体管的跨导小于N沟道MOS晶体管。 此外,P沟道MOS晶体管阈值电压的绝对值一般偏高,要求有较高的工作电压。

P型半导体是在单晶硅(或锗)中参入微量的三价元素,如:硼、铟、镓或铝等;N型半导体是在单晶硅(或锗)中参入微量的五价元素,如:磷、锑、砷等。P型半导体与N型半导体,在材料成本方面应该差别不是很大,但要把它做成一个电子产品,在生产工艺方面会存在很大的差异。

例如,用本征锗材料制作PNP晶体管相对于用本征锗材料制作NPN晶体管容易很多,因为铟与锗比较容易结合(扩散);同样,用本征硅材料制作NPN晶体管,相对于用本征硅材料制作PNP管要容易很多。某种半导体生产工艺的诞生并不是一天就可以达到尽善尽美的,需要通过大量试验和经验积累。早期生产的场效应管大部分是结型场效应管,这种结型场效应管在结构方面与PNP晶体管很相似,两者的区别主要是基区引出电极的区别(基极与源极和漏极)。晶体管把中间的一层(N区)当成一个电极引出称为基极,其余上下两层(P-P区)分别当发射极和集电极引出;而场效应管则是把基区当成一个导电沟道(N沟道),并在其两端分别引出一个电极,称为源极和漏极,其余上下两层(P-P区)分别当源极和栅极引出。绝缘栅场效应管则是从结型场效应管演变过来的,把结型场效应管中的栅极(P型半导体)换成金属氧化物,就可变成一个绝缘栅场效应管,简称mos管。早期的MOS管大量的都是采用N沟道结构(N沟道结构采用P型半导体做衬底),P沟道结构的场效应管(P沟道结构采用N型半导体做衬底)的诞生,相对要比N沟道结构的场效应管晚。可能是由于工艺上的原因,P沟道场效应管的价格一直比n沟道场效应管的价格高很多,但电性能却比N沟道结构场效应管差很多,因此,P沟道场效应管使用的人很少。P沟道场效应管比N沟道场效应管电性能差的原因,主要是沟道材料的电气性能不一样。在N沟道中参与导电的是电子,而在P沟道中参与导电的是空穴,两者在单位电场强度下的迁移率相差非常大。电子的迁移率远远大于空穴的迁移率,即N沟道的导电性能要比P沟道的导电性能好。因此N沟道场效应管的导通速度或工作频率要远远高于P沟道场效应管。

另外,用于制作场效应管栅极的金属氧化物,其与N型半导体的接点电位差,和与P型半导体接点电位差,不但数值不一样,而且极性也不一样。作为场效应管栅极的金属氧化物,与P型半导体的接点电位差要比N型半导体的接点电位差低(绝对值)。因此,P沟道场效应管和N沟道场效应管的工作电压极性也不一样,两者正好相反,并且输入、输出特性也不完全一样。P沟道场效应管的输入、输出特性与PNP晶体管的输入、输出特性相似;而N沟道场效应管的输入、输出特性与NPN晶体管的输入、输出特性相似。但场效应管属于电压控制特性,而晶体管则属于电流控制特性,两者还是存在本质上的区别。所谓节点电位差,就是两种不同性质的物体互相接触在一起的时候,由于组成物体的物质的外层电子的能级不同,在两物体接触界面处所产生的电位差(一个带正电,另一个带负电)。

MOS管的诞生相对来说还是比较早的,由于早期生产的MOS管相对于晶体管来说,可靠性很差,所以MOS管迟迟没有被大批量使用。直到微型计算机及大量数字电路产品出现以后,特别是CMOS大规模集成电路技术诞生之后, MOS管才被广泛应用。CMOS(Complementary Metal Oxide Semiconductor, 互补金属氧化物半导体)是一种同时采用两种工艺(垂直外延和横向外延)制造MOS管的大规模集成电路新技术(请参看问答1),鉴于N沟道场效应管在生产工艺和电气性能方面均比P沟道场效应管优越的原因,CMOS电路采用P衬底是理所当然的,因为在采用CMOS产生工艺的集成电路中,N沟道场效应管的数量要远远高于P沟道场效应管的数量。

MOSFET规格书参数-图解

参考:MOSFET规格书参数详解(参考AOD444)

Monte Carlo分析是一种器件参数变化分析,使用随机抽样估计来估算数学函数的计算的方法。它需要一个良好的随机数源。这种方法往往包含一些误差,但是随着随机抽取样本数量的增加,结果也会越来越精确。

Monte Carlo 分析和工艺角分析的区别如图1:

蒙特卡洛仿真

参考:蒙特卡洛仿真(Monte Carlo)

d18_v3e_bcd_v0p5_spe包含了工艺角。

矩形框中表示四个不同工艺角的覆盖范围,曲线表示用Monte Carlo分析得到的实际电路工艺偏差(一般满足高斯分布)。从图中可以看出,满足工艺角变化的范围不一定能完全满足覆盖实际工艺变化范围,因此要用Monte Carlo分析得到工艺角变化的概率,以得到电路的良率。

// * this file contains 0.18um v3e bcd 1.8v/5v/6v/9v/12v/16v/20v/24v/30v/35v/40v corner model parameters.

// * corners for mosfet: tt, ff, ss, snfp, fnsp are corners for global variation.

// * mc is for monte carlo simulation of global variation.

// * corners for ldmos: ldmos_tt, ldmos_ff, ldmos_ss, ldmos_snfp, ldmos_fnsp are corners for global variation.

// * ldmos_mc is for monte carlo simulation of global variation.

// * corners for bjt: bjt_tt, bjt_ff, bjt_ss are corners for global variation.

// * bjt_mc is for monte carlo simulation of global variation.

// * corner for diode: dio_tt, dio_ff, dio_ss are corners for global variation.

// * corners for resistor: res_tt, res_ff, res_ss are corners for global variation.

// * res_mc is for monte carlo simulation of global variation.

// * corners for varactor: var_tt, var_ff, var_ss are corners for global variation.

// * var_mc is for monte carlo simulation of global variation.

// * corners for mim: mim_tt, mim_ff, mim_ss are corners for global variation.

// * mim_mc is for monte carlo simulation of global variation.

// * corners for mom: mom_tt, mom_ff, mom_ss are corners for global variation.

// * mom_mc is for monte carlo simulation of global variation.

// * this file should be used with the model parameter files ‘d18_v3e_bcd_v0p5_mis.mdl’,

// * ‘d18_v3e_bcd_v0p5_ldmos.mdl’,

// * ‘d18_v3e_bcd_v0p5_res.ckt’,

// * ‘d18_v3e_bcd_v0p5_dio.mdl’,

// * ‘d18_v3e_bcd_v0p5_mim.ckt’,

// * ‘d18_v3e_bcd_v0p5_var.ckt’,

// * ‘d18_v3e_bcd_v0p5_mom.ckt’,

// * no part of this file can be released without the consent of smic.