基于ZYNQ UltraScale+ MPSoC 实现 MIPI数据接收+VDMA传输到DDR+UDP协议发送数据包

参考文档:

pg201-zynq-ultrascale-plus-processing-system

pg232-mipi-csi2-rx

pg020-axi-vdma

其他IP核的产品手册,请自行在DocNav中查阅

基于设备:

FPGA芯片:xazu3eg

开发板:百度EdgeBoard,有MIPI CSI 视频接口,千兆以太网,2GB的DDR

Vivado硬件工程建立:

底层硬件全部由Xilinx官方IP核搭建而成。主要的IP核有1.MIPI CSI-2 Rx Subsystem 2.AXI4-Stream Subset Converter 3.AXI Video Direct Memory Access 4.Zynq UltraScale+ MPSoC。

1.新建Vivado RTL 工程,选取工程名字,工程路径,FPGA型号xazu3eg。

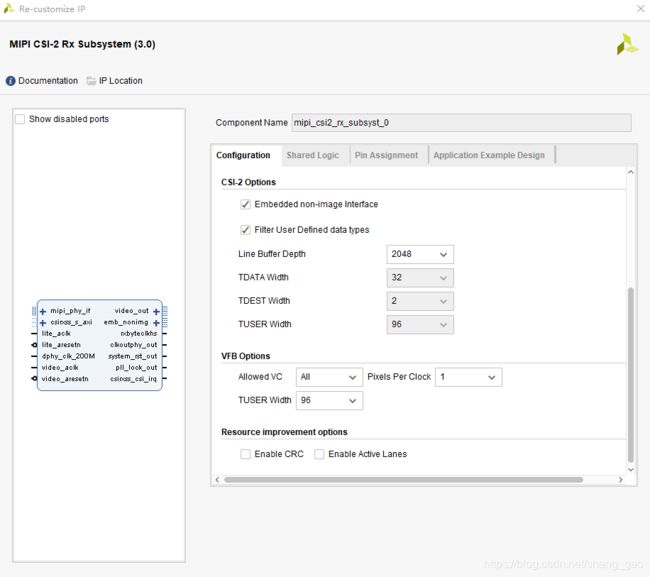

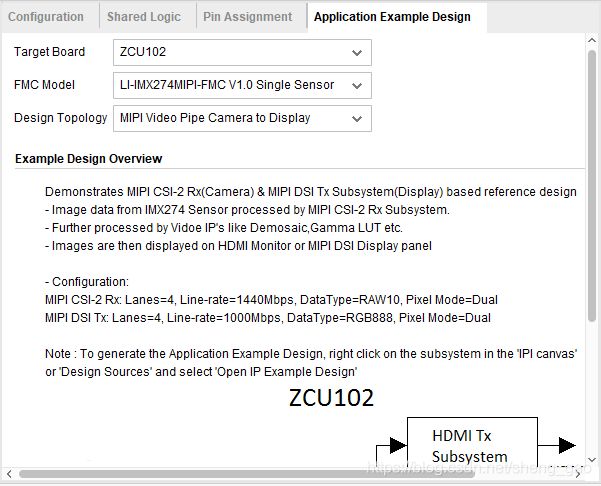

2.左侧菜单栏,点击Create Block Design。添加IP核MIPI CSI-2 Rx Subsystem。该IP核的主要作用是接收图像传感器输出的MIPI CSI ( Mobile Industry Processor Interface Camera Serial Interface ) 4通道数据,进行解协议输出AXI4-Stream格式的视频数据。双击例化的IP核进如参数配置页面。需要配置:Pixel Format:RAW12, Serial Data Lanes:4, Include Video Format Bridge, Line Rate:800Mbps, Embedded non-image Interface, Filter User Defined data types, Line Buffer Depth:2048, TUSER Width:96.

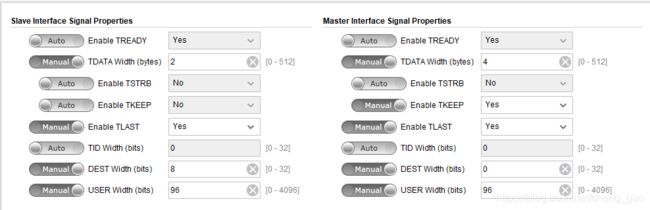

3. MIPI IP核配置好后,我们添加一个AXI4-Stream Subset Converter。主要作用是转换MIPI IP核video_out所输出的视频数据流格式。数据流位宽由16位扩充为32位,便于VDMA搬运。IP核命名为axis_subset_converter_0。具体个别参数的设置需要查询产品手册。

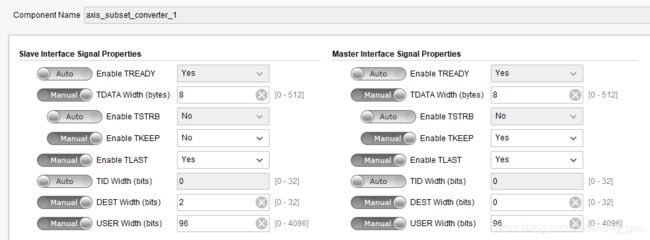

4.我们再添加一个AXI4-Stream Subset Converter。主要作用是转换MIPI IP核emb_nonimg输出的元数据流(元数据在每一帧图像的最后,用于提供该帧图像的部分寄存器配置,帧号,相位号)。IP核命名为axis_subset_converter_1。

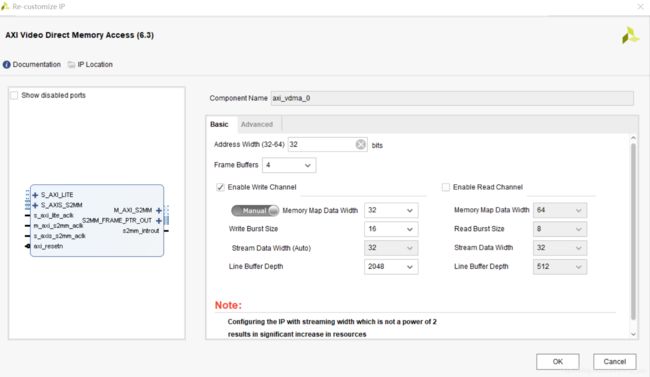

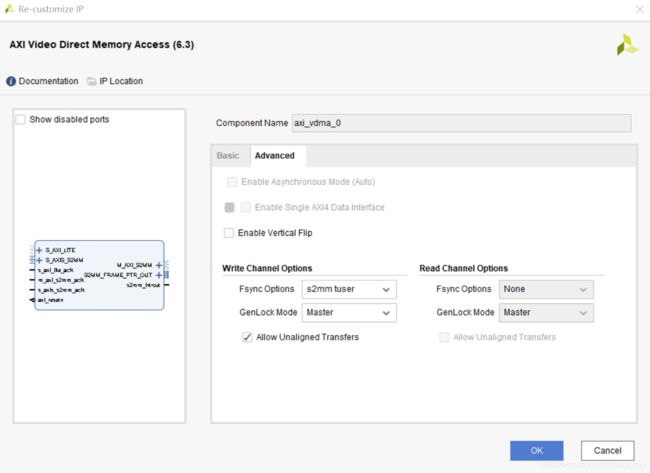

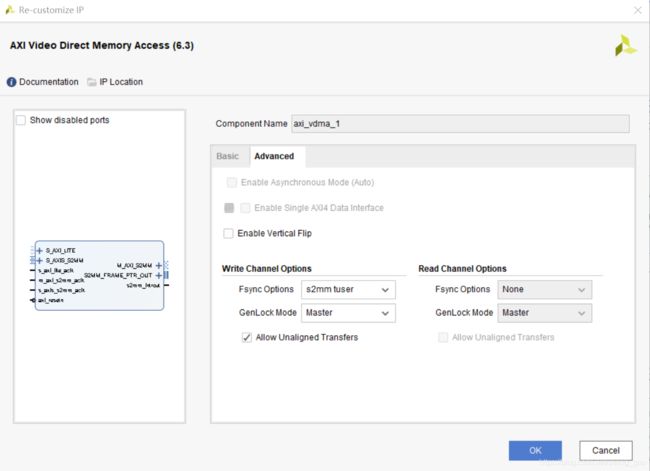

5. 我们添加一个AXI Video Direct Memory Access, 用来搬运AXI4-Stream到DDR Memory。IP核命名为axi_vdma_0, 用来搬运图像数据流。继续添加一个AXI Video Direct Memory Access,命名为axi_vdma_1,用来搬运元数据流。VDMA的主要管脚我这里简单描述下,S_AXI_LITE,是ZYNQ用来配置VDMA IP核,读写寄存器的端口。S_AXIS_S2MM是slave到master memory的数据流传输端口,包含很多具体的信号。s_axi_lite_aclk是S_AXI_LITE的时钟,表示读写寄存器的快慢。axi_resetn是s_axi_lite_aclk所对应的同步复位信号。m_axi_s2mm_aclk和s_axis_s2mm_aclk是视频流数据传输的时钟,代表VDMA搬运数据的快慢。M_AXI_S2MM是VDMA写通道的输出端口。Fsync Options指定了VDMA的帧同步方式,我们使用s2mm tuser信号来进行同步。其他具体参数配置信息请查阅Xilinx官方产品手册,并结合项目实际需求理解选定。

6. 添加两个AXI SmartConnect IP核。用于将axi_vdma的输出连接至ZYNQ的DDR部分。

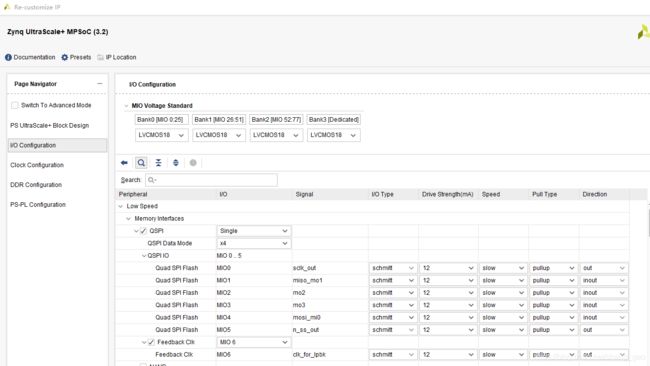

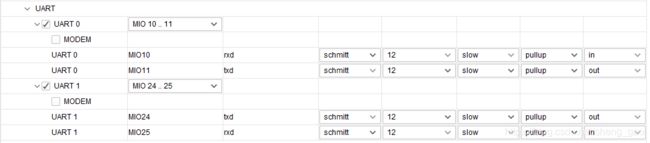

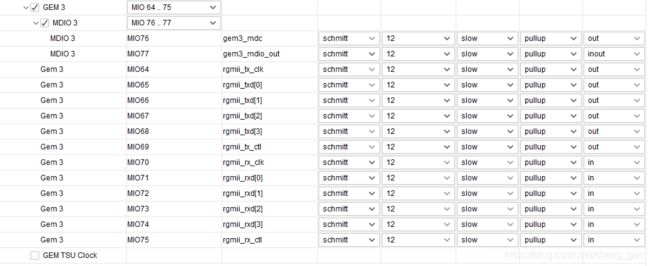

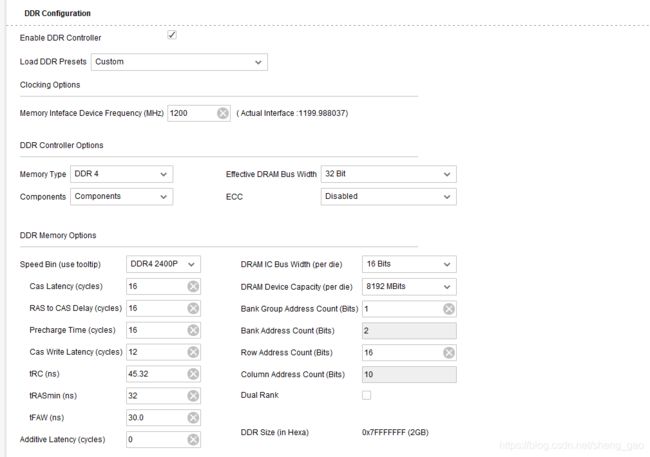

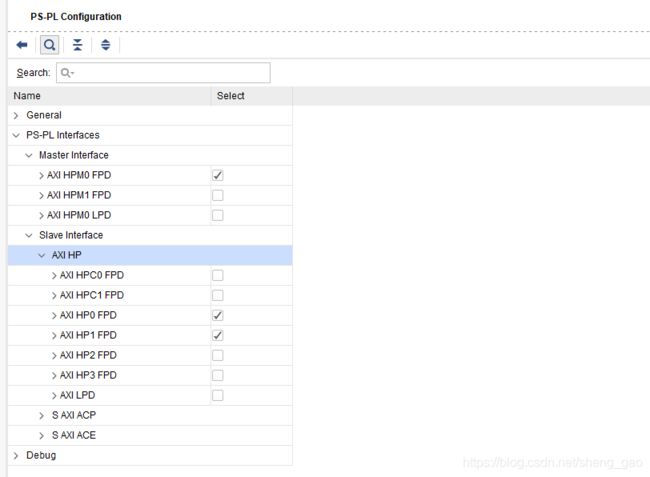

7. 添加Zynq UltraScale+ MPSoC。配置QSPI,用于将程序固化至FLASH。配置UART,用于打印串口信息。TTC计时器。GEM千兆以太网,用于发送UDP数据包。配置DDR,根据开发板上实际DDR的手册配置。配置IP核的寄存器控制端口,两路VDMA与DDR的接口。

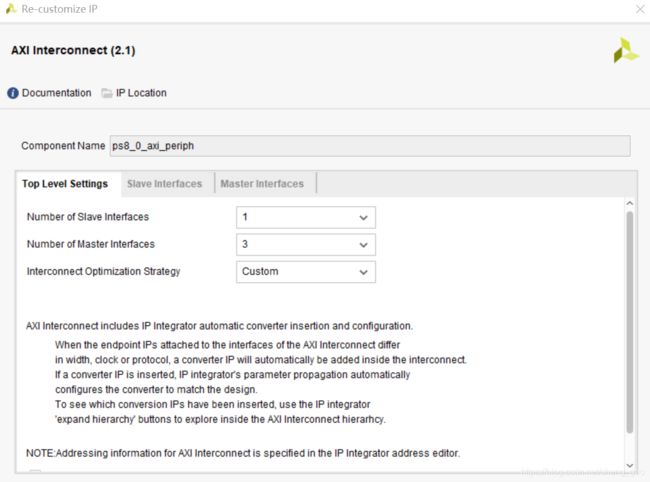

至此,ZYNQ UltraScale+ MPSoC IP核配置完成。接下来我们添加一个AXI Interconnect IP核,用于连接ZYNQ的IP配置输出端口M_AXI_HPM0_FPD,分流为三路信号分别控制MIPI CSI-2 Rx Subsystem的csirxss_s_axi,vdma0和vdma1的S_AXI_LITE。

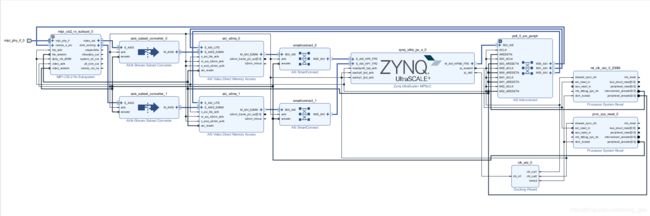

8. 主要的数据流接口都配置好后,我们手动将各个接口连接起来。简化后的电路图连接方式如下所示。

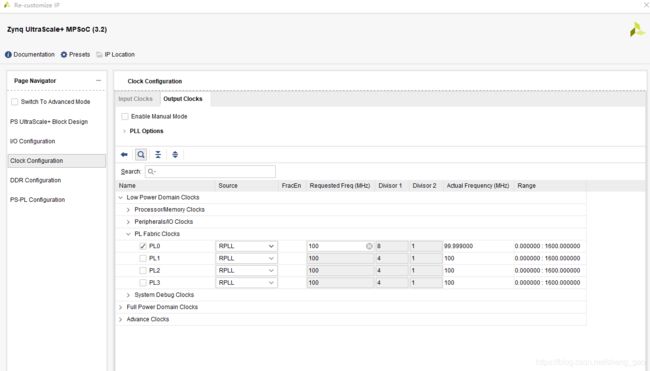

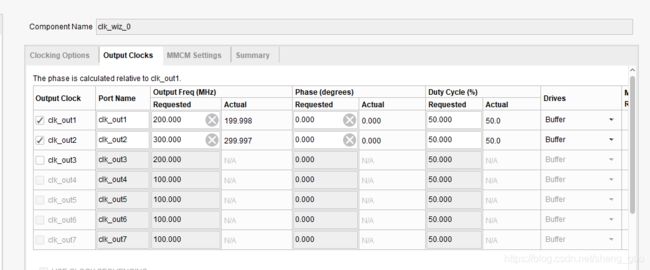

9. 接下来主要是时钟域和复位的设置添加。ZYNQ MPSoC输出pl_clk0为100MHz,我们添加一个CLOCKING WIZARD,经过倍频,输出200MHz和300MHz的两个时钟。200MHz用于ZYNQ读写IP核寄存器的时钟,MIPI CSI-2 所需的lite_aclk,dphy_clk_200M,vdma0和1的s_axi_lite_aclk,ZYNQ的maxihpm0_fpd_aclk,AXI Interconnect的所有时钟输入。300MHz用于视频数据流的传输时钟,因为图像传感器输出的MIPI数据流为高速通路,这里我们设置VDMA的时钟较快一些。300MHz连接至MIPI CSI-2 所需的video_aclk,AXI4-Stream Subset Converter所需的aclk,vdma所需的m_axi_s2mm_aclk, s_axis_s2mm_aclk,AXI SmartConnect所需的aclk,ZYNQ MPSOC所需的saxihp0_fpd_aclk, saxihp1_fpd_aclk。

复位功能我们需要添加两个Processor System Reset IP核。分别用作200M时钟和300M时钟的同步复位信号。手动将IP核的slowest_sync_clk与clk_out连接,peripheral_aresetn与各个IP核的复位端口连接,ext_reset_in与ZYNQ的输出复位信号pl_resetn0连接。最后全部连接完毕的电路图如下所示

10. 点击Validate Design。提示没有Error和Critical warning。在Sources菜单栏右键BLOCK DESIGN文件,点击Create HDL wrapper, 生成硬件代码。然后进行常规步骤,SYNTHESIS, IMPLEMENTATION, GENERATE BITSTREAM。成功后导出硬件文件,选择include bitstream。然后点击Launch SDK。

Xilinx SDK 软件工程建立

1. 点击File->New->Application project, 输入工程名字GS_MIPI_UDP,点击Next,选择IWIP UDP PERF CLIENT。点击FINISH。右键生成的GS_MIPI_UDP_bsp,选择BSP settings, 修改standalone串口打印为uart1,修改Iwip202中temac_adapter_options中phy_link_speed为1000Mbps。点击OK。会重新生成BSP。

2. 软件工程主要实现的功能是,初始化MIPI CSI-2 IP核,VDMA,网口。配置两路VDMA,四个缓冲区的地址设置(因为我们的图像传感器为TOF相机,一次外部触发会有4个相位帧的产生,同时有4个元数据行的产生,因此设置为4个缓冲区)。网口配置,建立UDP连接,FPGA板的MAC地址绑定,电脑的IP地址和端口绑定。VDMA开始搬运图像数据流后,从DDR中分别读取4个相位帧数据和Metadata数据。将数据按每个包1280字节放在数据包缓冲区,开始UDP传输。

3. 主要修改main.c, udp_perf_client.c, udp_perf_client.h。点击Project->Build ALL。会在Debug中生成GS_MIPI_UDP.elf。

在线调试

1. 在线调试是烧写FLASH的前提,先验证代码的功能正确与否。连接JTAG线,电源线,串口线,网线 电脑和FPGA之间。点击Xilinx->program FPGA, 如果有错误,检查FPGA板的BOOT顺序,连接线是否牢固。成功后,右键GS_MIPI_UDP,点击Run as->Launch on hardware,(需要单步调试,点击Debug as->Launch on hardware)。打印信息无误,可以用任务管理器查看网口的数据大小,有稳定的数据,则代表网口已经跑起来了。可以连接图像传感器,用WireShark抓包后,查看数据格式,转存数据,用MATLAB恢复图像。

烧写FLASH

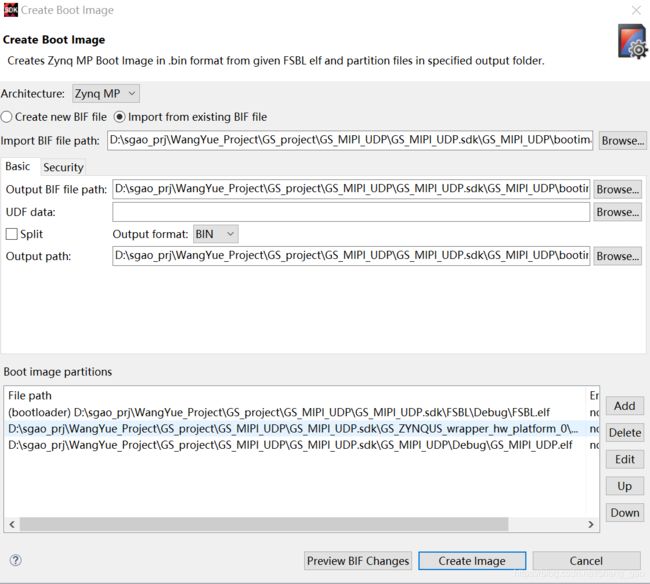

1. 点击File->New->Application project, 输入名字FSBL,点击Next,选择Zynq MP FSBL, 从FLASH运行必需的启动文件。右键GS_MIPI_UDP,选择Create BOOT image,添加所需文件,FSBL.elf, 比特流文件,GS_MIPI_UDP.elf。点击Create image。

由于我的FPGA型号与SDK默认检测到的型号对不上,我的是xazu3eg系列,但SDK检测到的是xczu3eg系列。因此这一步Create image不能成功生成BOOT.bin。于是改用XSCT命令行方式生成BOOT.bin。方法是点击Xilinx->XSCT Console,输入命令,切换文件夹路径为bootimage,声明器件为xazu3eg,成功生成BOOT.BIN。

cd D:/sgao_prj/WangYue_Project/GS_project/GS_MIPI_UDP/GS_MIPI_UDP.sdk/GS_UDP_ZYNQ/bootimage

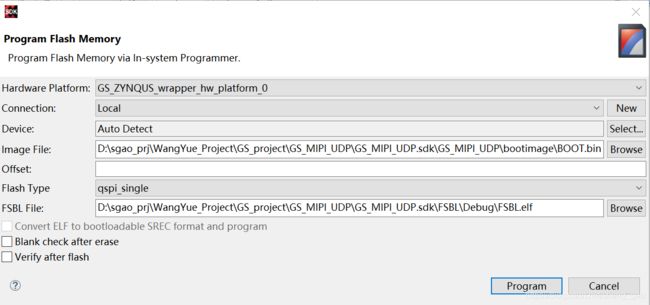

bootgen -image "GS_MIPI_UDP.bif" -arch zynqmp -w -o i "BOOT.bin" -packagename xazu3eg -log trace然后点击Xilinx->Program Flash 等待烧写成功。

整个MIPI数据接收,转网口发送的工程建立完毕。主要需要 各主要IP核的使用方法,IP核之间的连接,对xilinx SDK Iwip perf UDP Client示例代码的理解,添加自己的VDMA配置代码,DDR数据读取与VDMA搬运速度相匹配的转发逻辑代码。对Xilinx ZYNQ UltraScale+ MPSoC这个强大芯片的理解与应用又上了一层。和我上一篇博客的Altera FPGA 相结合起来,加上3D TOF 图像传感器套件就组成完整的硬件应用。Altera FPGA负责上电配置TOF相机,Sensor输出的MIPI数据由ZYNQ MPSOC接收,并转存数据为4个相位帧和4个元数据行,通过千兆以太网以UDP协议发送到PC端。PC端采集数据后,通过MATLAB回复图像、视频流。