【DRAM存储器二】Sense Amplifier

个人主页:highman110

作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

参考书籍:《Memory Systems - Cache, DRAM, Disk》

目录

前言

感应放大器的功能

感应放大器电路框图

感应放大器操作过程

感应放大器操作波形

前言

在读、写、刷新操作中,感应放大器发挥了举足轻重的作用,所以我们再用一节来详细研究一下感应放大器的功能和电路结构。

感应放大器的功能

感应放大器有三个主要功能:

第一个功能是感测,当存取晶体管导通并且存储电容向位线充电,或者位线向存储电容充电时,位线上发生的电压的微小变化。感测放大器将该位线上的电压与另一根单独的位线上提供的参考电压进行比较,并将电压差放大到极限,使得存储值可以被解析为数字1或0,这是读出感应放大器在DRAM中的主要作用。

第二个功能是恢复(或刷新),它在位线上的电压被感测和放大之后,恢复存储单元的值。导通存取晶体管的动作允许存储电容器与位线共享其存储的电荷。在电荷共享过程发生之后,存储单元内的电压大致等于位线上的电压,并且该电压电平不能用于另一读取操作。因此,在感测和放大操作之后,感测放大器还必须将放大的电压值恢复到存储单元。

第三个功能是读出放大器还充当临时数据存储元件。也就是说,在存储单元中包含的数据值被感测和放大之后,感测放大器将继续驱动感测的数据值,直到DRAM阵列被预充电并准备好进行另一次存取。以这种方式,可以从感测放大器访问同一行单元中的数据,而无需对单元本身进行重复的行激活。在这个角色中,感测放大器阵列有效地充当缓存整行数据的行缓冲器。因此,感测放大器的阵列也被称为行缓冲器,并且设计管理策略来控制感测放大器。不同的行缓冲器管理策略规定了读出放大器阵列是将数据保留一段不确定的时间(直到下一次刷新),还是在数据被恢复到存储单元后立即将其放电。

感应放大器电路框图

一个基本感应放大器的电路图:

现代DRAM器件中的感测放大器更复杂,除了包含上图所示的基本元件外,还有用于阵列隔离、感测放大器结构的精细平衡(类似效果就是使放大器的输入失调电压尽量小)和加速的感测能力的附加电路元件。

在上面的基本感测放大器电路图中,右边方框是均衡(EQ)信号线控制的电压均衡电路。该电路的功能是确保位线对上的电压尽可能紧密地匹配(就是使预充电后两根位线电压都是VDD/2)。由于差分感测放大器被设计为放大位线对之间的电压差,所以在行激活之前存在于位线对上的任何电压不平衡都会降低感测放大器的有效性,所以需要有一个位线电压均衡电路。

左边方框是感应放大器的核心,一组四个交叉连接的晶体管,左边NMOS,右边PMOS。感测电路本质上是双稳态电路,他根据SAN和SAP感测信号被激活时(所谓激活,就是SAN=0,SAP=VDD)位线上的相应电压来将位线对驱动到互补电压极值。

最右边的是输出结构,列选择线(CSL)控制输出晶体管的通断,使位线电平可以输出,或者外部输入电平能够作用到相应位线上。

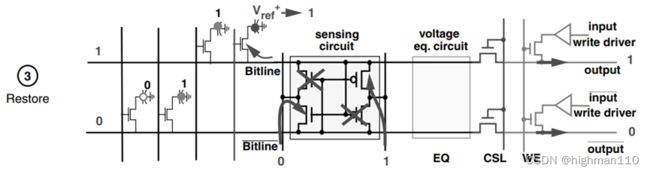

感应放大器操作过程

感应放大器的操作有四个不同阶段,称为预充电precharge、访问access、感测sense、恢复restore,下面一一介绍。

Precharge:预充电阶段感测电路sensing circuit被旁路,电压均衡电路激活,位线被预充电到参考电压Vref,即VDD/2,

Access:这个阶段就是行激活,打开MOS管,让位线可以“访问”到存储电容。由于存储电容存储逻辑为1时,其上电压为VDD,所以这个阶段的字线电压至少应为VDD+Vt(Vt为该MOS管导通的门限电压),如DDR4中VDD=1.2V,字线电压为2.5V。MOS打开之后,如果存储单元为1,电荷就会从存储电容往位线移动,使位线电压从vref上升一点点,反之,电荷就会从位线往存储电容移动,使位线电压下降一点点。

Sense:这个阶段就是要把上一阶段位线上的微小电压差放大到电压轨的极限,如将Vref+的位线驱动到逻辑1,也就是VDD电平,将另一根位线驱动到逻辑0,也就是地电平。如下图,假设是读取红框中的逻辑1,行激活后该位线上的电压增加到Vref+,对应的另一根位线保持Vref不变,此时感应放大电路左边的两个NMOS管都会有不同程度的导通,但由于Vref+略大,下管NMOS的导通程度略大,此时DRAM将SAN信号驱0,这个0电平会通过下管NMOS将下面的位线逐渐拉到0,同时上管NMOS由于栅极电平逐渐降低而逐渐关闭。同样的,SAP信号驱1(VDD),在下面的位线慢慢变0的过程中,上管PMOS逐渐导通,SAP通过上管PMOS逐渐将上面的位线驱动到逻辑1(VDD)。因此,SAN和SAP控制信号共同迫使双稳态读出放大器电路的两根位线被驱动至各自的最大或最小电压轨。

Restore:这个阶段就是要把之前从存储电容放出的电荷再补充回去,或者将存储电容中多余的电荷再放出来。接上一步,位线被驱动到VDD或者0,此时的字线仍然是保持高电平,存储单元MOS管仍是导通的,所以位线就可以对存储电源电容进行充电或放电,原来电容存储逻辑1的,就充电到VDD,原来电容存储逻辑0的,就放电到0,称为恢复或者刷新过程。在这个过程中位线电平是维持不变的,因为它是SAN和SAP强驱的,所以说感应放大电路起到了输出缓冲作用,在恢复操作的同时,可以将位线电平进行输出,即便字线被关闭了,也不影响位线的输出,所以想要再读这一行,就不用行激活操作了,这就是“行缓冲器”的作用。

再多提一句,上面阐述的是DRAM的读过程,总体原理为存储电容的充电或放电引起位线电平发生微小变化,然后感应放大电路将两根位线驱动到上下两个电源轨并维持稳态,然后输出或者刷新。写入原理基本一样,就是把改变位线电平的源头从存储电容变成了外部写驱动,就是上面图里的CSL和WE都使能之后,外部input write driver就能输入了,它写0或者写1就会引起位线电平变化,然后感应放大器就放大这个变化并维持稳态,要是行激活了,就可以往存储单元电源充电或者放电了。

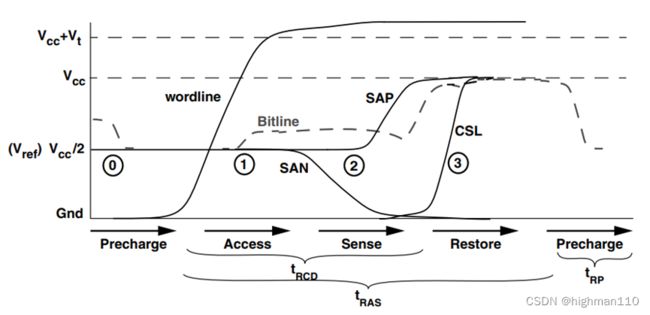

感应放大器操作波形

如上图是一个原存储单元存1的读取操作波形。0~3分别为上一节说的precharge、access、sense、restore四个阶段。可以看到,在预充电阶段,位线电压被预充电到Vref,在行选通阶段,存储单元向位线充电,所以位线电压慢慢提升到Vref+,随后在感应放大阶段,SAN和SAP先后置0和1把位线驱动到VCC电平,在恢复阶段,在感应放大电路的驱动作用下维持位线电平给存储单元充电,同时这个阶段打开列选通进行输出。

上图中还标明了几个重要的DRAM时序参数,tRCD:RAS to CAS delay,行选通到列选通的延时,就是行选通后,要等存储单元完成向位线充电(或者位线向存储单元充电),以及感应放大电路将位线电平驱动到VCC(或0)之后,才能进行列选通操作。tRAS:行选通周期,就是在行选通后,一定要等选通的存储单元完成恢复(或刷新)才能关闭此行。tRP:预充电周期,一定要将位线预充电到Vref才能做行选通操作,否则感应放大电路将无法正确驱动位线电平。