PHY芯片的使用(一)之基本概念讲解(MII相关)2

今天想和大家交流一下MAC和PHY之间的接口MII。

MII(Media Independent Interface )是介质无关接口。MII接口定义了在MAC层和物理层之间传送数据和控制状态等信息的接口,它是10M和100M兼容的接口,经过扩展后还可以用于1000M的MAC层与物理层的接口(GMII接口)。

1、个人使用心得交流

抛出这个定义后,想和大家聊一下我当时认识这个接口的过程。

首先本人方向是嵌入式软件,像这种常用的PHY芯片,如88e1111、DP83848等在uboot和linux下都有相应的驱动支持,不用开发者去关心。而且都是用基本的网路通讯功能。一些复杂的PHY芯片如XL53XXX,有1588功能的,就需要厂家提供相关的驱动,驱动中包含了一些特殊寄存器的配置和相关api接口。

在软件工程师不关心的前提下是要保证硬件原理设计、pcb设计没问题的前提下。在实际做工程应用中,如果不是迭代产品,像新研制的板卡有较大概率出现问题。在这样的前提下,我也更深入的了解PHY和硬件相关的知识。

MAC与PHY之间用MII接口,在网上搜索MII,出来各种mii详解(mii-gmii-rgmii-rmii-smii-ssmii-tbi-rtbi-rtbi-xgmii-xaui-xlaui等)看了以后头都晕。后面看了一些其他的资料,了解了常用PHY接口,常用的就4种:MII、RMII、GMII、SGMII。

上文提到过:

内部的 MAC 外设会通过相应的接口来连接外部 PHY 芯片, 根据数据传输模式不同,大致可

以分为以下两类:

⚫ MII/RMII 接口: 支持 10Mbit/s 和 100Mbit/s 数据传输模式;

⚫ GMII/RGMII 接口:支持 10Mbit/s、 100Mbit/s 以及 1000Mbit/s 数据传输模式。

在PHY芯片手册中会讲到该芯片支持哪种接口。

下图为88e1111的手册的接口描述:

下图为DP83848的手册的接口描述:

88e1111为千兆PHY,DP83848为百兆PHY。在zynq ps侧MAC只支持RGMII,若使用emio则出来的是GMII接口。若再想换其他接口,可使用IP核转换GMII to XXXX。因此在选用PHY和硬件设计上需要注意。

网上对MII相关的资料比较全,笔者也摘录以下内容完善本文结构。

2、MII 接口

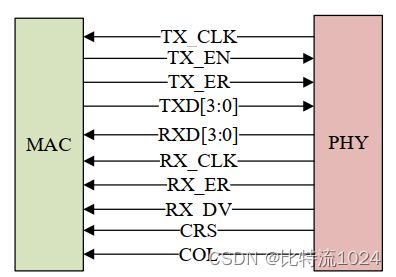

MII 全称是 Media Independent Interface,直译过来就是介质独立接口,它是 IEEE-802.3定义的以太网标准接口,MII 接口用于以太网 MAC 连接 PHY 芯片,连接示意图如下图所示:

MII 接口一共有 16 根信号线,含义如下:

TX_CLK: 发送时钟,如果网速为 100M 的话时钟频率为 25MHz,10M 网速的话时钟频率为2.5MHz,此时钟由 PHY 产生并发送给 MAC。

TX_EN: 发送使能信号。

TX_ER: 发送错误信号,高电平有效,表示 TX_ER 有效期内传输的数据无效。10Mpbs 网速下 TX_ER 不起作用。

TXD[3:0]:发送数据信号线,一共 4 根。

RXD[3:0]: 接收数据信号线,一共 4 根。

RX_CLK: 接收时钟信号,如果网速为 100M 的话时钟频率为 25MHz, 10M 网速的话时钟频率为 2.5MHz, RX_CLK 也是由 PHY 产生的。

RX_ER: 接收错误信号,高电平有效,表示 RX_ER 有效期内传输的数据无效。 10Mpbs 网速下 RX_ER 不起作用。

RX_DV: 接收数据有效,作用类似 TX_EN。

CRS: 载波侦听信号。

COL: 冲突检测信号。

MII 接口的缺点就是所需信号线太多,这还没有算 MDIO和 MDC这两根管理接口的数据线,因此 MII 接口使用已经越来越少了。

3、RMII 接口

RMII全称是 Reduced Media Independent Interface,翻译过来就是精简的介质独立接口,也就是 MII 接口的精简版本。RMII 接口只需要 7 根数据线,相比 MII 直接减少了 9 根,极大的方便了板子布线,RMII接口连接PHY芯片的示意图如下图所示:

TX_EN: 发送使能信号。

TXD[1:0]: 发送数据信号线,一共 2 根。

RXD[1:0]:接收数据信号线,一共 2 根。

CRS_DV: 相当于 MII 接口中的 RX_DV 和 CRS 这两个信号的混合。

REF_CLK: 参考时钟,由外部时钟源提供,频率为 50MHz。这里与 MII 不同, MII 的接收和发送时钟是独立分开的,而且都是由 PHY 芯片提供的。

4、GMII 接口

GMII( Gigabit Media Independant Interface),千兆 MII 接口。 GMII 采用 8 位接口数据,工作时钟 125MHz,因此传输速率可达 1000Mbps; 同时兼容 MII 所规定的 10/100Mbps 工作方式。 GMII 接口数据结构符合 IEEE 以太网标准,该接口定义见 IEEE 802.3-2000。信号定义如下图:

GTX_CLK: 1000M 工作模式下的发送时钟( 125MHz) 。

TX_EN: 发送使能信号。

TX_ER: 发送错误信号,高电平有效,表示 TX_ER 有效期内传输的数据无效。

TXD[7:0]:发送数据信号线,一共 8 根。

RXD[7:0]: 接收数据信号线,一共 8 根。

RX_CLK: 接收时钟信号。

RX_ER: 接收错误信号,高电平有效,表示 RX_ER 有效期内传输的数据无效。

RX_DV: 接收数据有效,作用类似 TX_EN。

CRS: 载波侦听信号。

COL: 冲突检测信号。

与 MII 接口相比, GMII 的数据宽度由 4 位变为 8 位, GMII 接口中的控制信号如 TX_ER、TX_EN、 RX_ER、 RX_DV、 CRS 和 COL 的作用同 MII 接口中的一样,发送参考时钟 GTX_CLK 和接收参考时钟 RX_CLK 的频率均为 125MHz(在 1000Mbps 工作模式下)。在这里有一点需要特别说明下,那就是发送参考时钟 GTX_CLK,它和 MII 接口中的 TX_CLK是不同的, MII 接口中的 TX_CLK 是由 PHY 芯片提供给 MAC 芯片的,而 GMII 接口中的 GTX_CLK是由 MAC 芯片提供给 PHY 芯片的, 两者方向不一样。在实际应用中,绝大多数 GMII 接口都是兼容 MII 接口的,所以,一般的 GMII 接口都有两个发送参考时钟: TX_CLK 和 GTX_CLK(两者的方向是不一样的,前面已经说过了),在用作 MII模式时,使用 TX_CLK 和 8 根数据线中的 4 根。

5、RGMII 接口

RGMII(Reduced Gigabit Media Independant Interface),精简版 GMII 接口。 将接口信号线数量从 24 根减少到 14 根(COL/CRS 端口状态指示信号,这里没有画出),时钟频率仍旧为125MHz, TX/RX 数据宽度从 8 为变为 4 位,为了保持 1000Mbps 的传输速率不变, RGMII 接口在时 钟 的 上 升 沿 和 下 降 沿 都 采 样 数 据 , 在 参 考 时 钟 的 上 升 沿 发 送 GMII 接 口 中 的TXD[3:0]/RXD[3:0],在参考时钟的下降沿发送 GMII 接口中的TXD[7:4]/RXD[7:4]。 RGMII 同时也兼容 100Mbps 和 10Mbps 两种速率,此时参考时钟速率分别为 25MHz 和 2.5MHz。TX_EN 信号线上传送 TX_EN 和 TX_ER 两种信息,在 TX_CLK 的上升沿发送 TX_EN,下降沿发送 TX_ER;同样的, RX_DV 信号线上也传送 RX_DV 和 RX_ER 两种信息,在 RX_CLK 的上升沿发送RX_DV,下降沿发送 RX_ER。RGMII 接口定义如下所示:

如有错误请指正!下次想交流一下MDIO,希望和大家共同进步!