FPGA时序约束--进阶篇(主时钟约束)

在FPGA设计中,时序约束的设置对于电路性能和可靠性都至关重要。在上一篇的文章中,已经详细介绍了FPGA时序约束的基础知识。

本文将重点讲解主时钟约束设置,给出详细的约束命令,并介绍了在Vivado中如何写入主时钟约束。

一、主时钟约束

主时钟是FPGA电路中最基础的时钟,其稳定性和精确性对电路的稳定运行有着至关重要的作用。在时序约束中,我们需要准确地定义主时钟的时钟约束,以确保电路的时序约束得以实现。

在Vivado中,我们可以使用create_clock命令来定义主时钟的时钟约束,其语法如下:

create_clock -name

| 参数 |

含义 |

|---|---|

| -name |

用于给时钟命名 |

| -period |

用于定义时钟周期 |

| -waveform |

波形参数,可以理解为占空比,一个周期时间内,rise_time表示第一个上升沿时刻,fall_time表示第一个下降沿时刻。 |

| get_ports |

指定工程里的模块时钟信号名 |

这里需要注意的是使用create_clock创建的时钟必须是主时钟primary clock。

FPGA中的主时钟通常有两种来源:

-

由外部时钟源(晶振)提供,通过引脚进入。

-

带高速收发器(GT)FPGA芯片型号,有GT时钟RXOUTCLK或TXOUTCLK。

对于Xilinx 7系列FPGA,需要对GT的两个时钟都添加约束,但对于UltraScale以及以上系列FPGA,只需对GT的输入时钟约束即可。

1、外部输入的单端主时钟信号

设定从引脚clk输入外部时钟,时钟周期为12ns,占空比50%,相移为0,则主时钟约束如下所示:

create_clock -period 12 [get_ports clk]

如果存在相移为90,则主时钟约束变为

create_clock -period 12 -waveform {3 9} [get_ports clk]

2、外部输入的差分时钟信号

PGA差分时钟是指通过时钟管脚的P端和N端共同进来的时钟信号。通常应用于高频或精度要求较高的场合,它的作用是消除共模噪声,从而提高系统性能。

只需要约束差分时钟的P端即可,不能同时约束P端和N端,N端可以被软件自动识别到。

比如差分时钟sys_clk_p和sys_clk_n,时钟周期为6.667ns,则约束为:

create_clock -name sys_clk -period 6.667 [get_ports sys_clk_p]

3、高速收发器GT时钟信号

FPGA高速收发器GT时钟信号,是指在FPGA中使用高速收发器GT(Gigabit Transceiver)进行信号收发时,需要使用与其速率相匹配的时钟信号进行同步传输。这样做可以确保信号稳定地传输,避免了数据传输中可能出现的误码情况。

比如时钟源由高速收发器gt0提供,则时序约束为:

create_clock -name rx0_outclk -period 3.333 [get_pins gt0/RXOUTCLK]

create_clock -name tx0_outclk -period 3.333 [get_pins gt0/TXOUTCLK]

二、Vivado添加时序约束

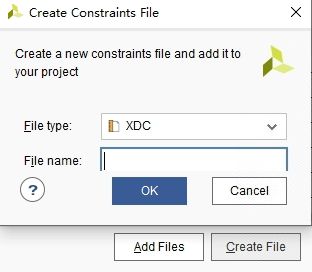

1、新建XDC文件,或添加已有的XDC文件

点击“+”号,选择“add or create constras”,点击下一步。

选择“create file”,填入时序文件名即可。

2、添加时序约束

(1)方法1

直接打开XDC文件,写入时序约束语句即可

(2)方法2

在将工程综合Synthesis完成后,点开“Open Synthesized Design”,等待打开完成后,直接在TCL console窗口中输入时序约束语句,回车即可。

(3)方法3

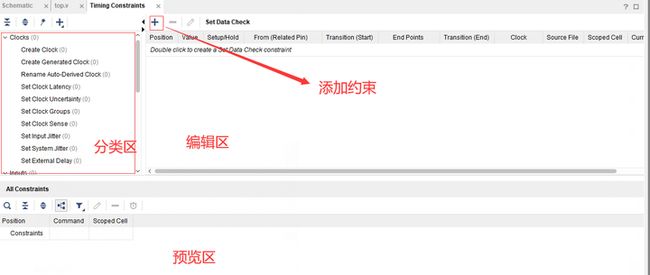

在将工程综合Synthesis完成后,点开“Edit Timing Constraints”,等待打开GUI界面。

在“分类区”选中要创建的约束类型,点击“+”号,创建约束,弹出约束创建界面。

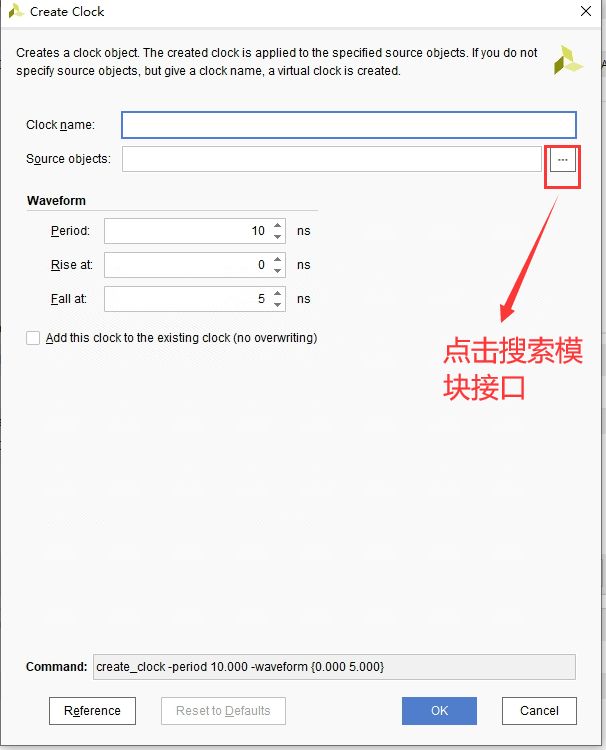

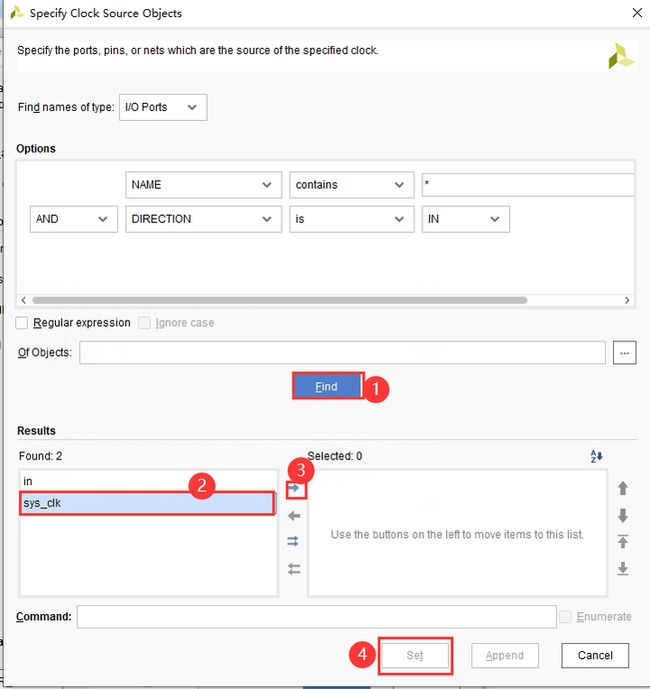

点击source objects右侧的“...”,打开模块接口搜索界面,并点击find按钮,选中“sys_clk”信号,点击“右箭头”,最后点击set即可。

最后输入时钟名,时钟周期,和波形参数即可,点击ok,并“ctrl + S”保存即可。

三、总结

主时钟约束是FPGA中常见的操作,必须掌握,本文已经详细介绍了操作命令和操作示范,希望可以帮助到大家学习并掌握这个知识。

本文将不断定期更新中,码字不易,点⭐️赞,收⭐️藏一下,不走丢哦

本文由FPGA入门到精通原创,有任何问题,都可以在评论区和我交流哦

学习资料分享,github开源代码:“FPGA知识库”

您的支持是我持续创作的最大动力!如果本文对您有帮助,请给一个鼓励,谢谢。