边沿检测电路

目录

边沿检测电路

1、边沿检测电路简介

1.1、上升沿检测电路

1.2、下升沿检测电路

1.3、双沿检测电路

2、实验任务

3、程序设计

3.1、编写代码

3.2、仿真验证

3.2.1、编写 TB 文件

3.2.2、仿真验证

4、本章总结

5、拓展训练

边沿检测电路

边沿检测指的是检测一个信号的上升沿或者下降沿,如果发现上升沿或者下降沿,则给出一个信号指示出来,即产生一个脉冲信号。边沿检测电路是非常常见的一个典型电路,需要完全掌握。边沿检测电路根据检测边沿的类型一般分为上升沿检测电路、下降沿检测电路和双沿检测电路。

1、边沿检测电路简介

边沿检测指的是检测一个信号的上升沿或者下降沿,如果发现上升沿或者下降沿,则给出一个信号指示出来。边沿检测电路一般分为上升沿检测电路、下降沿检测电路和双沿检测电路。

复杂的逻辑设计里面,很多情况都需要检测信号的跳变,如果一个信号发生跳变,则给出一个指示,这个指示用来触发其他的动作。这里就需要有一个边沿检测电路,因此这个电路是非常常见的一个典型电路,其设计思想也是一个很重要的设计思想。

我们根据检测边沿的类型一般可以将边沿检测分为上升沿检测电路、下降沿检测电路和双沿检测电路。

下面我们依次来看下这几个类型。我们先来看下上升沿检测电路,信号检测由 0 变 1 的过程,就是上升沿检测电路(posedge edge),信号检测由 1 变 0 的过程,就是下降沿检测电路(negedge edge)。若上升沿和下降沿都检测,则这个电路就是双沿检测电路(double edge)。

1.1、上升沿检测电路

下面我们来介绍下时序中常用的边沿检测电路,我们先来看下上升沿检测电路。

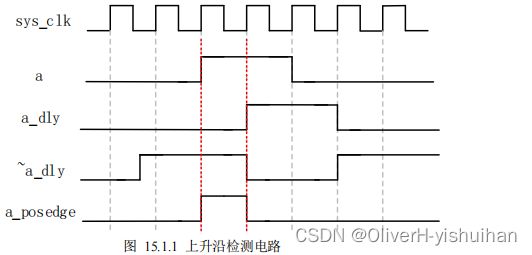

如上图所示,a 信号是一个持续 2 个时钟周期的信号,如果想得到 a 信号的上升沿也就是 a_posedge 信号,大家想下,我们应该怎么做呢?a_posedge 信号是一个持续 1 个时钟周期的脉冲信号,那么如果我们把 a 信号寄存一拍,得到 a_dly 信号。我们再用 a 信号和 a_dly 取反再相与,是不是就可以得到一个持续 1 个时钟周期的脉冲信号呢,这个 a_posedge 信号就是 a 的上升沿指示信号。

1.2、下升沿检测电路

看完上升沿检测电路后,接下来我们再来看一下下降沿检测电路。

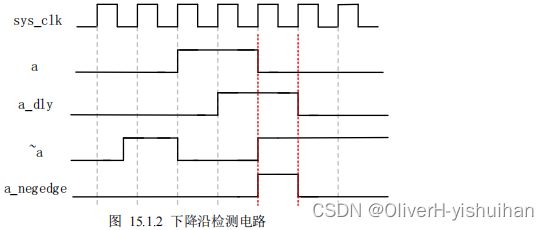

如上图所示,a 信号是一个持续 2 个时钟周期的信号,如果想得到 a 信号的下降沿也就是 a_negedge 信号,大家再想下,我们应该怎么做呢?首先 a_negedge 信号是一个持续 1 个时钟周期的脉冲信号,那么如果我们把 a 信号寄存一拍,得到 a_dly 信号,我们再把 a 信号取反,用 a 取反的信号和 a_dly 相与,是不是就可以得到一个持续 1 个时钟周期的脉冲信号呢,这个 a_negedge 信号就是 a 的下降沿指示信号。

1.3、双沿检测电路

看完下降沿检测电路后,接下我们再来看下双沿检测电路。

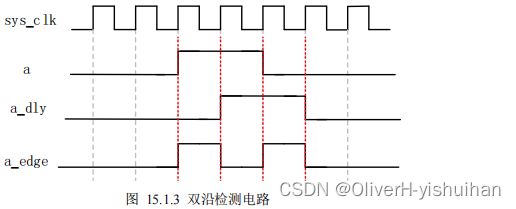

如上图所示,a 信号是一个持续 2 个时钟周期的信号,如果想得到 a 信号的上升沿和下降沿也就是 a_edge 信号,大家想下,我们应该怎么做呢?从图上可以看出,取沿的时机正好符合异或门的逻辑。也就是说 a_edge 信号刚好是 a 和 a_dly 信号不同的地方为高电平,那么 a 和 a_dly 异或的结果就是 a_edge 信号,这个信号在 a 的上升沿持续一个时钟周期,然后在 a 的下降沿后又持续一个时钟周期。

2、实验任务

使用 Verilog 语言设计上升沿、下降沿和双沿检测电路。

3、程序设计

3.1、编写代码

我们可以根据三种边沿检测电路的波形图以及分析,来编写边沿检测电路(edge_test.v),代码编写如下:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/06/19 16:55:33

// Design Name:

// Module Name: edge_test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

//边沿检测指的是检测一个信号的上升沿或者下降沿,如果发现上升沿或者下降沿,

//则给出一个信号指示出来。边沿检测电路是非常常见的一个典型电路。

//边沿检测电路根据检测边沿的类型一般分为上升沿检测电路、下降沿检测电路和双沿检测电路。

//实验任务

//使用 Verilog 语言设计上升沿、下降沿和双沿检测电路。

module edge_test(

input sys_clk, // system clock 50Mhz on board

input sys_rst_n, // system rst, low active

input a,

output a_posedge, // output signal

output a_negedge, // output signal

output a_edge // output signal

);

//define reg

reg a_dly;

//********************************************

//** main code

//********************************************

//输入 a 通过时序逻辑延迟一拍赋值给 a_dly。

always @(posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

a_dly <= 1'b0;

else

a_dly <= a;

end

assign a_posedge = a & ~a_dly; //取上升沿

assign a_negedge = ~a & a_dly; //取下降沿

assign a_edge = a ^ a_dly; //取双沿

endmodule

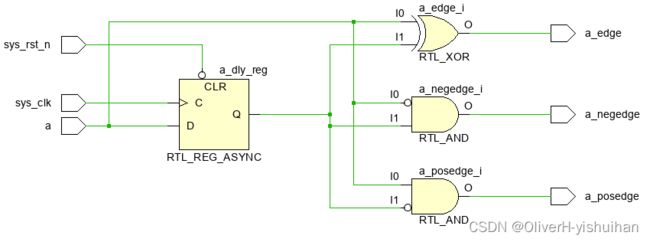

接下来我们使用 Vivado 的 RTL ANALYSIS,来看一下我们编写代码的 RTL 视图。

从上图可以看出,a_dly 是 a 寄存一拍的结果,a_posedge 是上升沿检测输出,a_negedge 是下降沿检测输出,a_edge 是双沿检测输出(异或门)。

3.2、仿真验证

3.2.1、编写 TB 文件

边沿检测 TB 模块(tb_edge_test.v)只需要对时钟以及复位信号进行激励,代码编写如下:

`timescale 1ns / 1ps //仿真单位/仿真精度

//

// Company:

// Engineer:

//

// Create Date: 2023/06/19 17:09:32

// Design Name:

// Module Name: tb_edge_test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

//边沿检测 TB 模块(tb_edge_test.v)只需要对时钟以及复位信号进行激励。

module tb_edge_test();

reg sys_clk;

reg sys_rst_n;

reg a;

wire a_posedge;

wire a_negedge;

wire a_edge;

initial begin

sys_clk = 1'b1;

sys_rst_n <= 1'b0;

a <= 1'b0;

#201

sys_rst_n <= 1'b1;

#20

a <= 1'b1;

#100

a <= 1'b0;

end

always #10 sys_clk <= ~sys_clk;

edge_test u_edge_test(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.a (a ),

.a_posedge (a_posedge ),

.a_negedge (a_negedge ),

.a_edge (a_edge )

);

endmodule

3.2.2、仿真验证

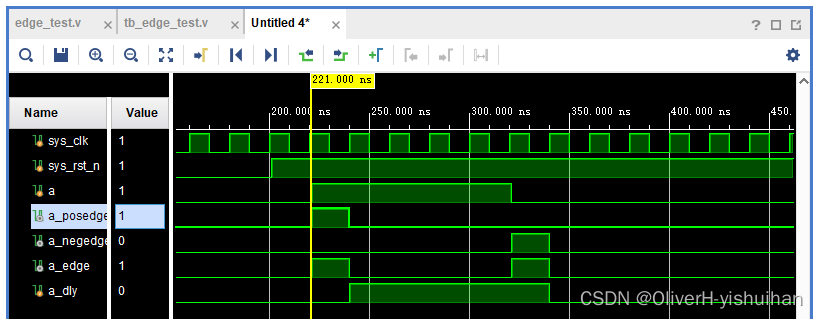

从仿真波形中可以看出,可看到 a_posedge 是检测上升沿脉冲,a_negedge 是检测下降沿脉冲,a_edge 是检测双沿脉冲。

4、本章总结

本章主要讲解了几种常用的沿检测电路,它们分别是上升沿检测电路、下降沿检测电路以及双沿检测电路。通过绘制的波形图向大家详细的讲解了边沿检测电路的原理,并根据边缘检测电路的原理带领大家使用 verilog 代码设计了一个边沿检测电路模块。在我们后续的学习和设计中也会经常的跟边沿检测电路打交道,所以希望大家能够通过本章节的学习掌握边沿电路的使用。

5、拓展训练

本章我们使用组合逻辑电路,实现了一个边沿检测电路的设计。有兴趣的,可以根据我们本章的内容,设计一个时序逻辑电路的边沿检测电路。