ZYNQ——锁相环(PLL)实验

文章目录

- 一、介绍

- 二、添加时钟 IP

- 三、设计源代码

- 四、仿真测试

- 五、添加 ILA IP

- 六、分配引脚

- 七、板上验证

- 八、示波器输出

- 九、问题汇总

一、介绍

ZYNQ开发板上只有一个50MHz的时钟输入,如果要用到其他频率的时钟,就需要通过FPGA芯片内部集成的PLL(Phase Locked Loop,锁相环)来分频或者倍频实现。

一个复杂的系统往往需要多个不同频率、不同相位的时钟信号,所以FPGA芯片中的PLL的数量也是衡量FPGA芯片性能的重要指标。在FPGA的设计中,时钟系统的FPGA高速的设计相当重要,一个低抖动、低延迟的系统时钟会增加FPGA设计的成功率。

本实验通过添加时钟 IP 核实现分频和倍频。

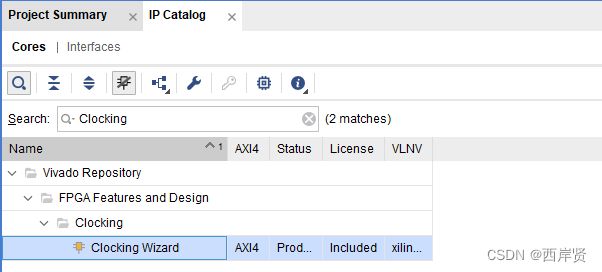

二、添加时钟 IP

打开 IP Catalog,搜索 Clocking 找到 Clocking Wizard 双击打开。

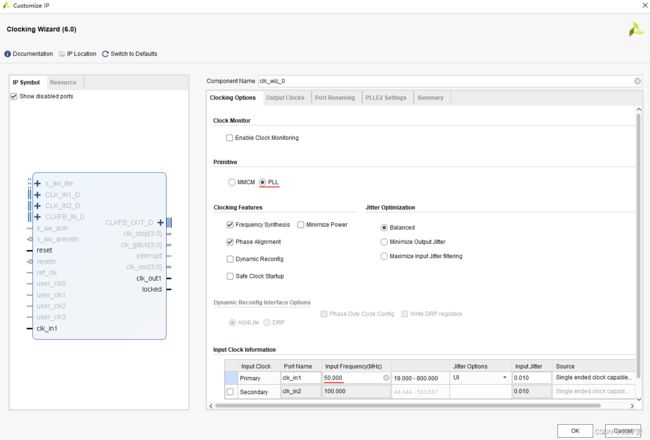

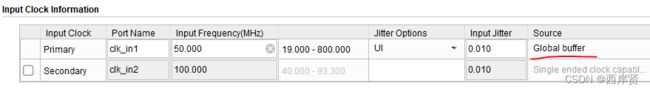

打开后弹出下面对话框,选择PLL,输入时钟设为 50MHz。

MMCM(Mixed Mode Clock Manager)是混合模式时钟管理器,用于在与给定输入时钟有设定的相位和频率关系的情况,以生成不同的时钟信号。

PLL 主要用于频率综合,使用一个PLL可以从一个输入时钟信号生成多个时钟信号。

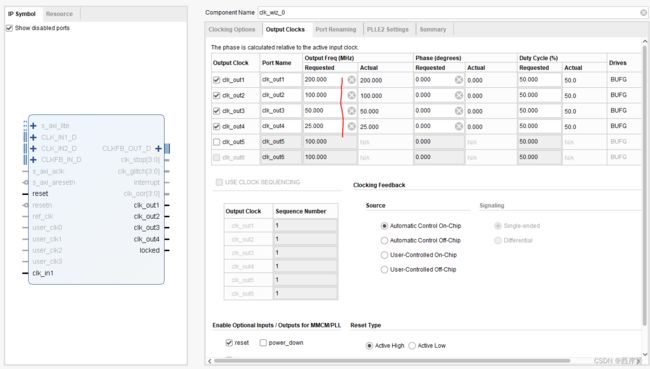

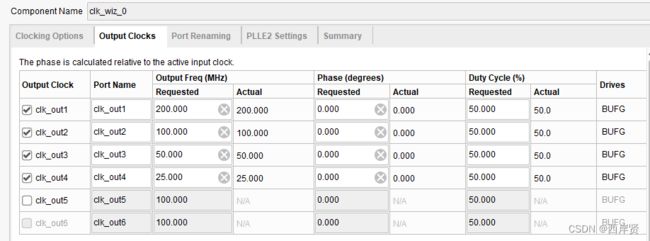

然后在输出时钟子页面下设置四个输出频率。

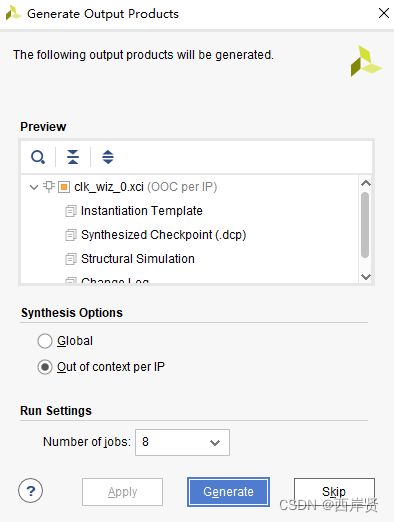

设置完成后点击OK,弹出下面窗口,点击生成即可完成时钟 IP 核的添加。

三、设计源代码

在IP Sources下找到上面添加时钟IP核的.veo文件,双击打开如下图。

将其中的例化代码复制,新建一个设计源文件,粘贴到里面,最终的代码如下。

module pll(

input clk,

input rst,

output clk_out1,

output clk_out2,

output clk_out3,

output clk_out4

);

wire locked;

clk_wiz_0 clk_wiz_0_inst

(

// Clock out ports

.clk_out1(clk_out1), // output 200MHz

.clk_out2(clk_out2), // output 100MHz

.clk_out3(clk_out3), // output 50MHz

.clk_out4(clk_out4), // output 25MHz

// Status and control signals

.reset(~rst), // input reset

.locked(locked), // output locked

// Clock in ports

.clk_in1(clk)); // input 50MHz

endmodule

这里需要注意的是,PLL的复位是高电平有效,如果后续需要在开发板上通过按键来复位,由于按键是低电平有效的,因此上述代码中的复位信号需要反向。

四、仿真测试

本例中的仿真测试源代码如下。

`timescale 1ns / 1ps

module sim_pll();

reg clk;

reg rst;

wire clk_out1;

wire clk_out2;

wire clk_out3;

wire clk_out4;

initial

begin

clk = 0;

rst = 1; //PLL复位高电平有效,代码中有取反,所以这里设置为1

end

always #10 clk = ~clk;

pll uut_pll(

.clk(clk),

.rst(rst),

.clk_out1(clk_out1),

.clk_out2(clk_out2),

.clk_out3(clk_out3),

.clk_out4(clk_out4)

);

endmodule

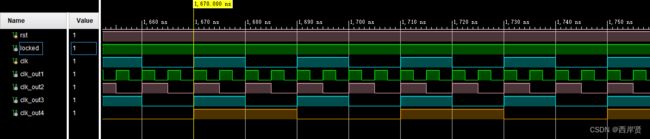

仿真输出结果如下图所示。

代码中的时钟是20ns一个周期,所以频率就是50MHz。通过上面的输出结果可以看到,clk_out1的频率是输入时钟频率的4倍,即200MHz,同理,clk_out2的频率是输入时钟频率的2倍,也就是100MHz,clk_out3与输入同频率,即50MHz,clk_out4的频率是输入时钟频率的0.5倍,即25MHz。

在 PLL 中改变一下时钟3和时钟4的相位,如下图。

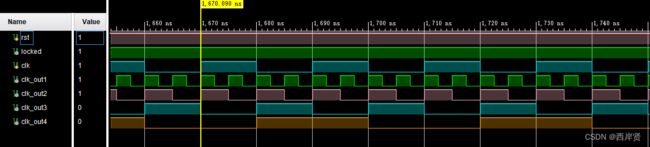

修改相位后的仿真输出结果如下图所示。

再与上面相位未做变化时做比较,可以明显看到时钟3和输入时钟反向,即相移180°,时钟四相较于输入时钟相移90°。

因此,通过上述仿真可以直到,通过PLL可以生成多个不同频率、不同相位的时钟信号。

五、添加 ILA IP

六、分配引脚

用上面的代码在板上验证时需要示波器测量,我这里通过添加ILA分析输出的结果,编写的代码如下。

module pll(

input clk,

input rst,

output clk_out1,

output clk_out2,

output clk_out3,

output clk_out4

);

reg in,out1,out2,out3,out4;

wire locked;

initial

begin

in = 1;

out1 = 1;

out2 = 1;

out3 = 1;

out4 = 1;

end

always@(posedge clk or negedge rst)

begin

if(!rst)

in = 0;

else

in = ~in;

end

clk_wiz_0 clk_wiz_0_inst

(

// Clock out ports

.clk_out1(clk_out1), // output 200MHz

.clk_out2(clk_out2), // output 100MHz

.clk_out3(clk_out3), // output 50MHz

.clk_out4(clk_out4), // output 25MHz

// Status and control signals

.reset(~rst), // input reset

.locked(locked), // output locked

// Clock in ports

.clk_in1(clk)); // input 50MHz

always@(posedge clk_out1)

begin

if(!rst)

out1 = 0;

else

out1 = ~out1;

end

always@(posedge clk_out2)

begin

if(!rst)

out2 = 0;

else

out2 = ~out2;

end

always@(posedge clk_out3)

begin

if(!rst)

out3 = 0;

else

out3 = ~out3;

end

always@(posedge clk_out4)

begin

if(!rst)

out4 = 0;

else

out4 = ~out4;

end

ila_0 ila_inst (

.clk(clk),

.probe0(in),

.probe1(out1),

.probe2(out2),

.probe3(out3),

.probe4(out4)

);

endmodule

七、板上验证

生成比特流并将其下载到ZYNQ开发板上进行验证。

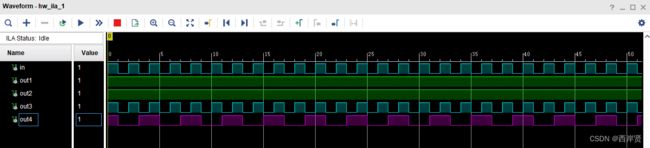

在集成逻辑分析仪窗口查看输出结果如下图。

上面这张图是输入为50MHz的情况,out1(200MHz)和out2(100MHz)没有正确的显示。

根据代码中编写的,in信号代表的是输入时钟(in信号是实际时钟频率的二分频,不过不影响和后续频率的比较,因为输出信号都是在此机制下产生的,因此倍数关系不会变),我改为了200MHz,因为50MHz在板上验证的时候,发现倍频输出的两个频率100MHz和200MHz不能正确的输出,而分频可以正常输出,所以我就改为了200MHz,只看分频的结果。

可以看到,输出out1与输入in信号同频;输出out2是输入in信号的二分频;输出out3是输入in信号的四分频;输出out4是输入in信号的八分频。这与我在PLL中预设的是一致的,但是仔细观察上面的两个图发现,输入为50MHz和200MHz时,in信号的波形是一致的,所以通过ILA这种方式查看输出不太准确。

八、示波器输出

本来想通过ILA验证一下输出结果就行了,但是又出现了一系列的问题,所以还是决定在示波器中测量一下相关引脚的频率。

输入还是设置为50MHz,输出时钟设置如下。

在Vivado中生成比特流文件,将其下载到开发板,然后根据引脚的分配测量相关引脚的频率。

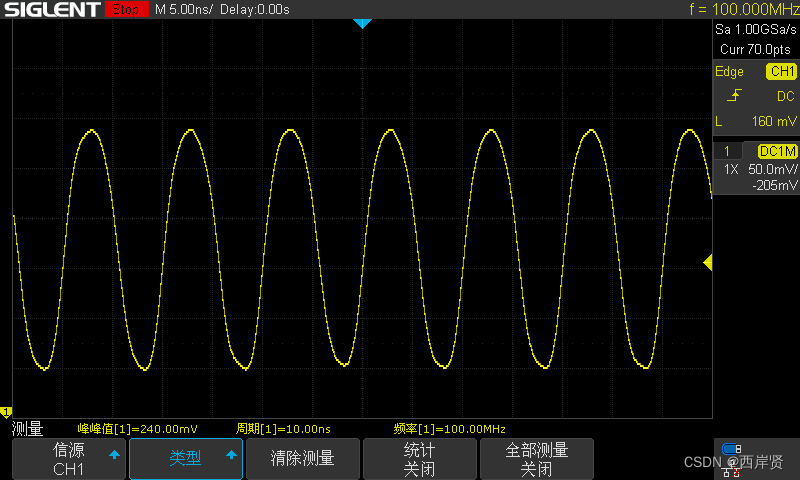

示波器中200MHz引脚的输出如下图所示。

示波器中100MHz引脚的输出如下图所示。

示波器中50MHz引脚的输出如下图所示。

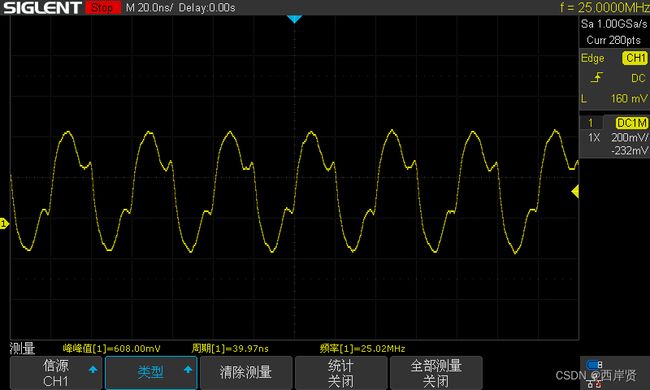

示波器中25MHz引脚的输出如下图所示。

通过上面各图的结果可知,频率能够按照代码中设置的那样进行输出。不过输出的波形不太像方波,反而更像正弦波,这是因为示波器带宽不太够,可以参考文章示波器的带宽,一般示波器带宽是所测信号频率的5倍时,方波就比较明显了,上面的四张图随着频率的减小,波形也越接近正弦波。不过波形不是我们这里关心的重点,频率输出是正确的。

九、问题汇总

这个实验在仿真的过程中很顺利,基本没碰到什么问题,但在板上验证时遇到了一些麻烦,现列出如下。

1、运行时报错了,如下图所示。

报错信息如下。

[DRC REQP-1712] Input clock driver: Unsupported PLLE2_ADV connectivity. The signal clk_wiz_0_inst/inst/clk_in1 on the clk_wiz_0_inst/inst/plle2_adv_inst/CLKIN1 pin of clk_wiz_0_inst/inst/plle2_adv_inst with COMPENSATION mode ZHOLD must be driven by a clock capable IO.

解决办法:回到PLL IP核这里,将Source改为Global buffer。

2、输入时钟频率直接通过探针无法观看,输出是一条线,因此,我在代码里引入了reg变量,通过时钟的上升沿让值反转来表示该频率,实际的频率应当是该种表示方法表示下的二倍,不过这里只是验证一下各输出频率与输入频率的关系,因此,这个差异不影响最终的结果判定。

3、在板上验证时发现倍频的波形输出不正确而分频正确,也不知道是什么原因造成的,我这里直接将输入频率改为最大,只验证了分频的正确性。

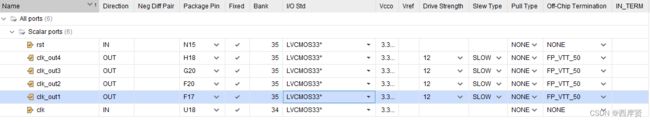

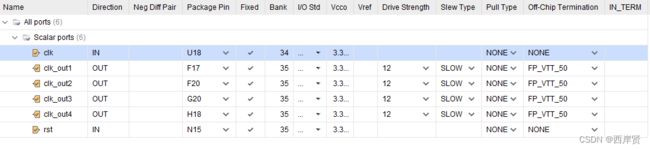

4、还有一个不算是问题吧,就是一个简单的操作,默认的引脚分配窗口打开就是下图所示的这样。

可以看到 Name 这一列是空的,在分配引脚时端口对应代码中的哪个端口虽然可以通过 I/O Ports Properties 得知,但总是觉得哪里不太对劲。是的,确实不太对劲,你用鼠标把 Name 对应的这一列往宽拉一点就发现“新大陆”了!

以上就是ZYNQ——锁相环(PLL)实验的全部内容了,自己总是会在实验中碰到这样那样奇怪的问题,发现问题和寻找解决办法的过程虽然有点痛苦,甚至有点绝望,但是这些都是必经之路!

参考资料:

ZYNQ 开发平台 FPGA 教程 AX7020