Cadence17.2 > OrCAD Capture CIS > 设计规则检查(Design Rule Check)DRC学习记录详解

目录

一、Design Rule Check对话框选项详解

1)Design Rule Options选项详解

2)Electrical Rules(电气规则检查)选项详解

3)Physical Rules(物理规则检查)选项详解

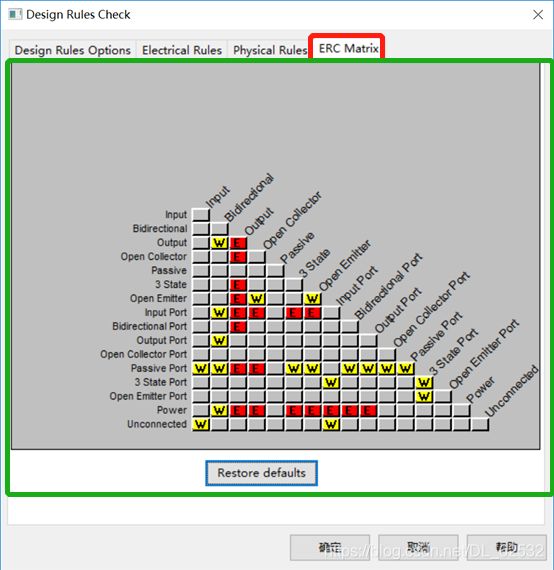

4)ERC Matrix tab(ERC 矩阵选项卡)选项详解

选中设计完成的DSN文件,选择Tool->Design Rule Check,弹出下面对话框,详解如下。

一、Design Rule Check对话框选项详解

| Design Rules Options tab |

Set the scope, mode and type of design rule (electrical and / or physical) test options for the design rules check. |

|

| Electrical Rules tab |

Set the electrical design rule checks and reports to be generated from the check. |

|

| Physical Rules tab |

Set the physical design rule checks and reports to be generated from the check. |

|

| ERC Matrix tab |

Set the matrix rules used during the design rules check. |

|

1)Design Rule Options选项详解

| Scope |

Select the scope of the design rules check. The scope can cover the entire design, or the selected schematic folder. If you run Design Rules Check on a single schematic page, Capture checks all pages in the entire schematic folder, which ensures that all nets on the schematic page are valid. |

|

| Mode |

Specify to check either instances or occurrences. Capture automatically sets this option based on the project type. All designs default to use instances. If a PCB or Schematic design is complex or has occurrence properties, the default shifts to occurrences. Capture recommends the preferred mode, which you can override. |

|

| Action |

Specifies either a design rules check, deletion of existing DRC markers or creating DRC markers for warning. The DRC markers are automatically deleted when you run a subsequent design rules check. Use the Ignore DRC Warnings option to specify any DRC Warnings that you do not want to be checked during the DRC check and netlisting. For example, to ignore the ALG0051 or ALG0016 warnings during netlist, specify these in the Ignore Warnings dialog. You can select the Preserve waived DRC to retain the DRC waiver settings for a design. When you waive a DRC, it is not included in the DRC report. Setting this option ensures that the waived DRCs are not shown when you run DRC on the design. |

|

| Design Rules |

Select the type of rules to run, electrical and / or physical. |

|

| Report file |

Specify the path and file name for the report. |

|

| View Output |

Open the design rules check report file in a text editor. |

|

| Browse |

Displays a standard Windows dialog box for selecting files. |

|

2)Electrical Rules(电气规则检查)选项详解

| Electrical Rules(电气规则检查) |

||

| Check single node nets |

Check if the design contains any nets with only one connection. |

检查设计是否包含任何只有一个连接的网络。 |

| Check no driving source and Pin type conflicts |

|

|

| Check duplicate net names |

Check if the design contains any duplicate net names. |

|

| Check off-page connector connections |

Verify that off-page connector nets on a schematic page match those on other schematic pages. |

|

| Check hierarchical port connections |

Verify that hierarchical pins in a hierarchical block match hierarchical ports in the child schematic folder or folders. Errors are generated if the number of hierarchical ports and hierarchical pins differ between the parent and child schematic folders. Also generates errors if the types of hierarchical ports are not identical between the parent and child schematic folders. |

|

| Check unconnected bus nets |

Check for and reports all unconnected bus nets. This check will run for all unconnected bus nets across schematics in a design. |

|

| Check unconnected pins |

Check for any pins on the design that are unconnected or do not have no-connect attached. |

|

| Check SDT compatibility |

Check for SDT compatibility. |

|

| Custom DRC |

||

| Run custom DRC |

Select to run custom DRCs. |

选择运行自定义 DRC。 |

| Configure Custom DRC |

Click to launch the Custom Design Rule Checker to select custom TCL DRCs that you want to run. |

单击以启动自定义设计规则检查器以选择要运行的自定义 TCL DRC。 |

| Reports |

||

| Report all net names |

List the names of all nets in the report file. |

|

| Report off-grid objects |

List all objects that are on Fine grid in the report file. |

|

| Report hierarchical ports and off-page connectors |

List all hierarchical ports and off-page connectors in the report file. |

|

| Report misleading tap connections |

Checks for and reports those signals that are wrongly connected through a Bus Tap to a bus. Also checks for missing bus taps. |

|

3)Physical Rules(物理规则检查)选项详解

| Physical Rules |

||

| Check power pin visibility |

Check if the visibility property of a power pin on one section of multi-section part is different from the corresponding power pin on another section of the part. |

|

| Check missing/illegal PCB Footprint property |

Check if the PCB footprint property on a part is missing or the property defined is illegal. |

|

| Check Normal Convert view sync |

Check if the pin numbers on the normal view of a part are different from the pin numbers on the convert view. |

|

| Check incorrect Pin_Group assignment |

Check if all pins in same pin group in a part are of the same type. |

|

| Check high speed props syntax |

Check the syntax of the high speed properties of the nets in the design. |

|

| Check missing pin numbers |

Check if any part on the design has missing pin numbers. |

|

| Check device with zero pins |

Check if any part on the design has no pin on the part. |

|

| Check power ground short |

Check if the type of power pin name inside a part is connected to a net on the schematic with a different name. |

|

| Check Name Prop consistency |

Check if the occurrences of a hierarchical block have the same "Name" property. |

|

| Reports |

||

| Report Visible unconnected power pins |

List the names of all visible unconnected power pins. |

|

| Report unused part packages |

List the names of any unused part packages. |

|

| Report invalid packaging |

List any invalid packaging. |

|

| Report identical part references |

List any identical part references. |

|

4)ERC Matrix tab(ERC 矩阵选项卡)选项详解

| Matrix |

Set the rules used by the Design Rules Check when testing connections between pins, hierarchical blocks, and hierarchical ports. The pins, hierarchical ports, and off-page connectors are listed in columns and rows in the table. A test is represented by the intersection of a row and column. Either the intersection of a row and column is empty, or it contains a "W" or an "E." An empty intersection represents a valid connection, a "W" is a warning, and an "E" represents an error. You can cycle through these three settings by pointing to an intersection and clicking the mouse button until the desired setting displays. You can also type W for warning, E for error, and N for an empty intersection. In addition to these keys, you can use the arrow keys to select other intersections. |

|

| Restore defaults |

Restore the ERC matrix to its default values. |

|

编辑半天时间,祝大家开心,Enjoy:)