Ultrascale selectio 仿真之 IDELAYE3和IDELAYCTRL

TIME模式时,使用IDELAYE3必须配合IDELAYCTRL使用

1 IDELAYCTRL

If the IDELAYE3 (or ODELAYE3) primitives are instantiated, the IDELAYCTRL module must be instantiated, except when the DELAY_FORMAT is set to COUNT or when mixing component and native mode in native mode designs.

只有在DELAY_FORMAT不为COUNT模式或者不为mixing component and native模式时,例化IDELAYE3或者ODELAYE3原语被例化时,IDELAYCTRL模块必须被例化。

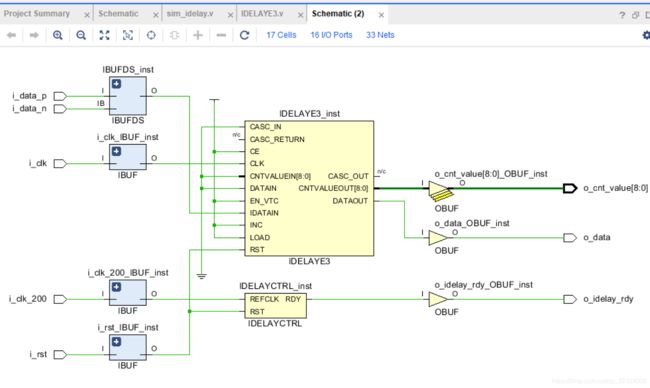

IDELAYCTRL block图

IDELAYCTRL端口说明

| Port |

I/O |

Type |

Description |

| REFCLK |

Input |

Clock |

Reference clock for delay calibration. |

| RST |

Input |

Reset |

Active-High asynchronous reset for IDELAYCTRL. |

| RDY |

Output |

Data |

The ready signal goes High to signal that controlled IDELAYE3 and ODELAYE3 primitives are calibrated. |

2 IDELAYE3

除时钟外的任何输入信号都能使用IDELAYE3原语做延时,然后直接转发到设备逻辑,或者使用SDR/DDR时钟,通过一个简单的触发器,IDDR或者ISERDESE3寄存。

IDELAYE3有512个tap,DELAY_FORMAT工作模式有两种:

COUNT模式不需要IDELAYCTRL,无校准,只是记数tap的个数(最多512个taps),参考时钟REF_FREQUENCY默认为300MHz;

TIME模式需要IDELAYCTRL,有校准,记数ps的个数,参考时钟REF_FREQUENCY需要和IDELAYCTRL的参考时钟一致。

IDELAYE3 block图:

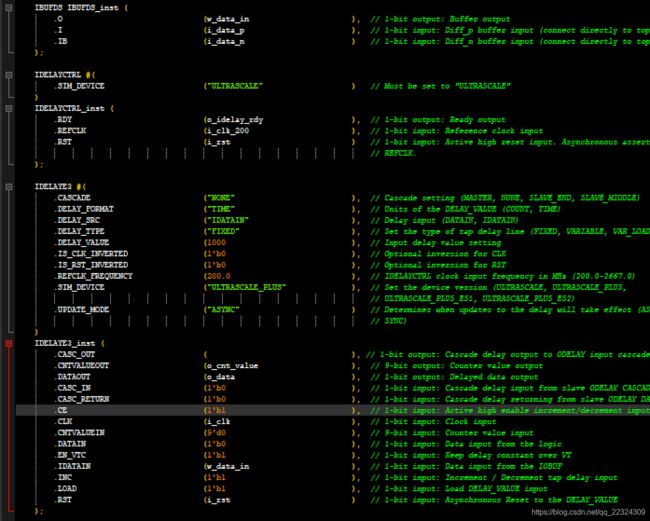

TIME模式下:

(1)DELAY_TYPE为FIXED时,数据延时取决于DELAY_VALUE的值,且延迟固定,不可更改。该模式下

(2)DELAY_TYPE为VARIABLE时,当LOAD有效(低电平),自动加载DELAY_VALUE的值作为延时初始值;当CE和INC高脉冲有效时,延时自动在初始值的基础上增加1个Tap。

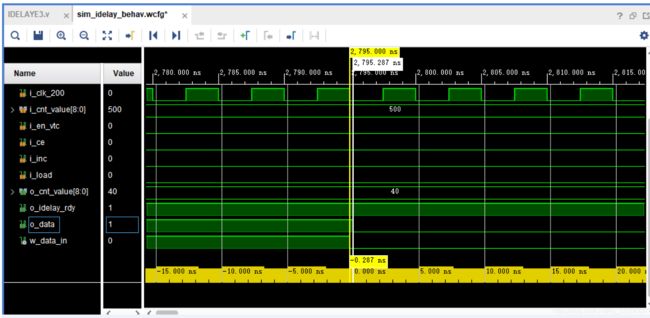

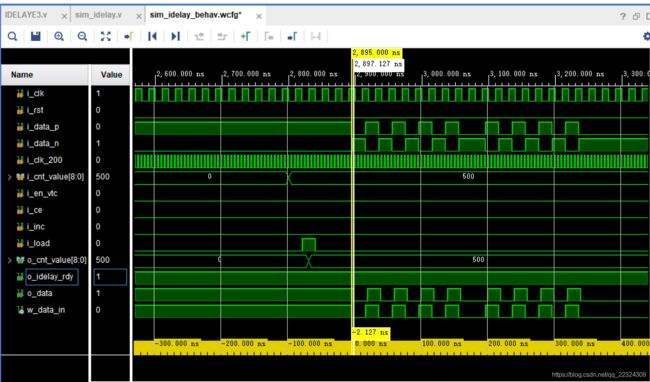

设置DELAY_VALUE=200(单位ps),初始的CNTVALUEOUT为40(单位Tap),可以计算出1个Tap值为5ps。

CNTVALUEOUT为41时,延时差值291ps。

CNTVALUEOUT为42时,延时差值295ps。

CNTVALUEOUT为43时,延时差值299ps。

CNTVALUEOUT为40时,延时差值287ps。

通过操作是的CNTVALUEOUT逐一累加Tap个数,发现每增加一个Tap,延时值只增加了4ps(这个值跟上述计算的5ps有出入,此处有疑问??),总延时是“对齐延时+DELAY_VALUE”。

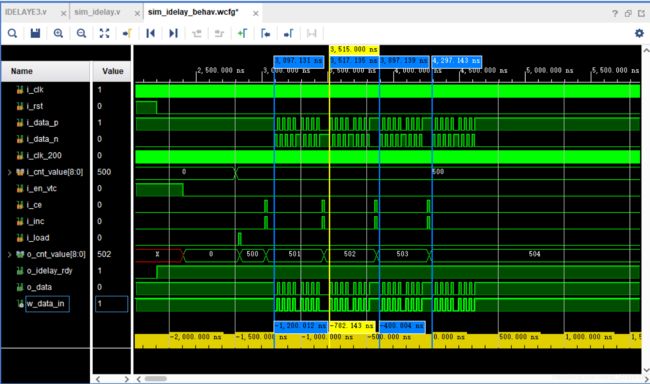

(3)DELAY_TYPE为VAR_LOAD时,当LOAD为高脉冲时载入CNTVALUEIN的值作为延时初始值;当LOAD拉低后,CE和INC高脉冲有效时,延时自动在初始值的基础上增加1个Tap。注:LOAD相当于是CNTVALUEIN的载入开关,体现在CNTVALUEOUT上,因此可将LOAD信号作为脉冲来使用。

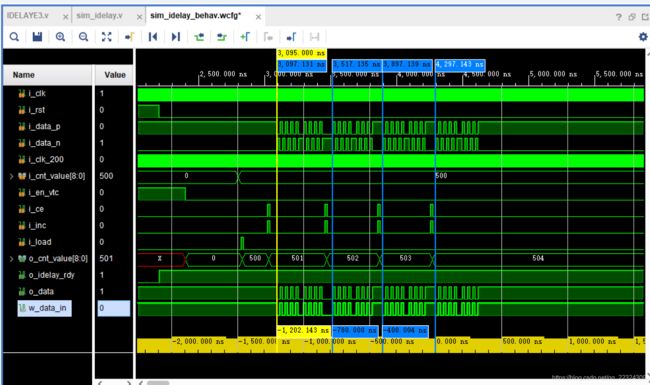

设置CNTVALUEIN=500(单位Tap),初始的CNTVALUEOUT为500(单位Tap)。

CNTVALUEOUT为501时,延时差值2131ps。

CNTVALUEOUT为502时,延时差值2135ps。

CNTVALUEOUT为503时,延时差值2139ps。

CNTVALUEOUT为503时,延时差值2143ps。

CNTVALUEOUT为500时,延时差值2127ps。

通过操作CNTVALUEOUT逐一累加Tap个数,发现每增加一个Tap,延时值增加了4ps。