7A50T 引脚功能详解

本文针对7A50T芯片,详细讲解硬件设计需要注意的技术点,可以作为设计和检查时候的参考文件。问了方便实用,按照Bank顺序排列,包含配置Bank、HR Bank、HP Bank、GTP Bank、供电引脚等。

参考文档包括:

ds181_Artix_7_Data_Sheet

ug470_7Series_Config

ug472_7Series_Clocking

ug480_7Series_XADC

ug482_7Series_GTP_Transceivers

目录

Bank 0(配置Bank,HR)

电源

XADC

JTAG

配置

Bank 14/15/16(HR)

电源

普通IO

配置IO(Bank 14/15)

时钟IO

XADC(Bank 15)

其他IO

Bank 34/35(HR)

电源

普通IO

时钟IO

其他IO

Bank 216(GTP)

校准

时钟

数据

电源

非GTP

GTP

硬件Checklist

Bank 0(配置Bank,HR)

电源

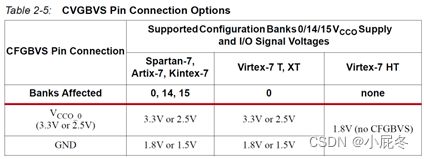

1. VCCO_0:

1V5/1V8/2V5/3V3可选,不支持1V2配置,因此也不支持1V2供电。

- 当VCCO_0=3V3或2V5时,CFGBVS也必须和VCCO_0保持一致;

- 当VCCO_0=1V8或1V5时,CFGBVS需要接GND;

- CFGBVS一般不需要上下拉电阻,直连就可以。

Virtex-7 FPGA比较特殊,非HT(Virtex-7 HT)器件的Bank 0和其他S/A/K系列相同,而Bank 14/15时HP Bank,仅支持1V8以下电平;Virtex-7 HT器件无CFGBVS引脚,仅支持1V8电平。

实际应用中,常用主SPI和主BPI模式来配置FPGA,涉及到Bank 0/14/15,三个Bank的VCCO需要保持一致,并且和外挂FLGASH的供电电压也要保持一致。

2. VCCBATT_0:

FPGA内部加密模块供电,连接到外部电池,保证FPGA掉电时加密模块依然有电;若不使用加密功能,连接GND/VCCAUX;该引脚不受VCCO_0的限制。

DS182中规定电压范围为1V0~1V89,并没有明确规定时1V8/1V5还是1V2;

不使用加密功能时,建议接入VCCAUX(1V8)或GND。

S7的7S6/7S15不支持加密功能,该引脚需要接VCCAUX或GND。

实际应用中,一般直连GND。

XADC

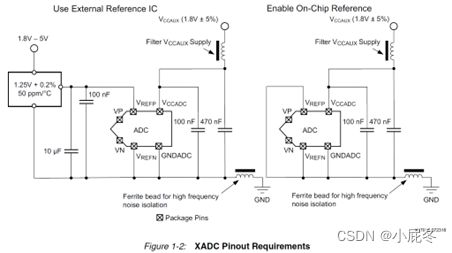

- VCCADC_0:XADC的模拟电源引脚,1V8供电,建议单独供电或通过滤波电路(电感等)连到VCCAUX上,不使用时也需要接VCCAUX;

- GNDADC_0:XADC的模拟接地引脚,可以通过磁珠连接到系统GND,也可以连接到系统的模拟地上(此时不再需要额外的磁珠,系统模拟地应已处理),不使用时也需要接GND;

- VREFP_0:参考电压基准(1.25V),可接外部基准(±0.2%或±9LSB/12-bit),也可采用内部基准(±1%或±41LSB/12-bit),不使用外部基准时连GNDADC_0;

- VREFN_0:参考电压基准地,常连GNDADC_0;

- VP_0vn_0:XADC专用输入引脚(专用时对比其他XADC模拟输入来说,该引脚不能用作普通IO,其他的都可以),不使用时连GNDADC_0;

- DXP_0/DXN_0:内部温度二极管,结合外部温度监控电路可实现对FPGA芯片结温的监控,不用时接GNDADC_0。

JTAG

- TCK_0:测试时钟输入,连外部仿真器,建议加防静电措施(TVS管),含驱动电路时需注意保持默认高电平(输入侧加10kΩ上拉),IPU;

- TMS_0:测试模式输入,连外部仿真器,建议加防静电措施(TVS管),含驱动电路时需注意保持默认高电平(输入侧加10kΩ上拉),IPU;

- TDO_0:测试数据输出,连外部仿真器,建议加防静电措施(TVS管),级联时链接后级TDI_0引脚,IPU;

- TDI_0:测试数据输入,连外部仿真器,建议加防静电措施(TVS管),级联时链接前级TDO_0引脚,IPU。

大多数应用中,不会涉及到多个FPGA,即使涉及到了,也不会级联,而是每个器件都会预留一个JTAG调试口。若涉及到多个FPGA基连的情况,常规的做法是多个FPGA共用TCK/TMS,前级TDO接后级TDI,需要考虑驱动能力、走线等因素。

配置

配置引脚的接法和期间采用的配置模式相关,当前常用的配置模式是主SPI和主BPI模式,主串、主并、从串、从并模式基本上不用,进介绍两种常用模式下的连接方法。

- CCLK_0:从同步模式下连接到外部时钟引脚;主同步模式下,FPGA输出该时钟信号;JTAG模式下,该引脚时高阻态,可以悬空(异步模式也适用)。布局时需要考虑信号完整性(源端匹配+上下拉);

- INIT_B_0:该引脚刚上电时为低电平,直到初始化完成,变为高阻态,需要外接上拉电阻到VCCO_0(≤4.7kΩ),便能为高电平后开始采用M[2:0]引脚,执行后续操作;该引脚上电期间可以由外部强制拉低,以推迟FPGA配置过程(建议预留下拉电容的位置);不建议将该引脚连接到FLASH的/RESET引脚上,因为各厂家的复位时间要求不同;

- PROGRAM_B_0:重配置引脚,低电平触发配置数据清零并重新配置,下降沿启动复位,上升沿启动重配置,通过电阻(≤4.7kΩ)上拉到VCCO_0,建议通过开关连接到GND,以使能手动复位功能。上电时,PROGRAM_B一直拉低不会使器件一直保持复位状态,而应该通过拉低INIT_B来延迟器件配置过程;

- CFGBVS_0:决定以Bank 0/14/15的点评标准,Bank 14/15仅适用于配置期间,连接VCCO_0代表2V5/3V3(Bank 0),连接GND代表1V8/1V5(Bank 0),Bank 14/15的电平需要和Bank 0匹配。Virtex-7 HT器件的Bank 14/15为HP Bank,仅支持1V8以下电平标准,CFGBVS不影响这两个Bank;Virtex-7 HT器件的Bank 0/14/15仅支持1V8电平标准,无CFGBVS引脚;

- DONE_0:该引脚上的高电平代表配置完成,内涵10kΩ上拉电阻,外部可以不接,也可以接330Ω上拉电阻,以兼容之前系列器件;

- M0_0/M1_0/M2_0:决定了FPGA的启动模式,直连VCCO_0/GND或通过上下拉电阻连接(≤1kΩ),主SPI对应001,主BPI对应010,JTAG对应101,建议预留JTAG模式(101),FPGA起不来又连不上仿真器的情况下可以用来恢复。

Bank 14/15/16(HR)

电源

VCCO_14/15/16:可接1V2/1V5/1V8/2V5/3V3等多种电压,根据需要选择。

其中,Bank 14/15比较特殊,若涉及到配置引脚,需要和VCCO_0保持一致。

普通IO

Bank 14共2个普通IO;

Bank 15共5个普通IO;

Bank 16共32个普通IO。

配置IO(Bank 14/15)

仅针对主SPI/主BPI情况说明,其他情况基本上用不到。

- D00_MOSI:主SPI模式下,连接SPI FLASH的数据输入引脚,数据传输完成后为高阻态,PUDC_B决定是否带上拉;主BPI/并行模式下,用作D00(多功能引脚);其他模式下,该引脚为高阻态,可以悬空;

- D01_DIN:主SPI/串行模式下,连接到数据源设备的数据输出引脚;主BPI/并行模式下,用作D01(多功能引脚)了JTAG模式下,被忽略;

- D[00-31]:主SPI模式下,x1/x2模式只用到D00_MOSI和D01_DIN引脚,x4模式用到D00-D03四个引脚,D00连接D10/D/SI/IO0,D01连接DQ1/Q/SO/IO1,DO2连接DQ2/W#WP#IO2且需要外部4.7kΩ上拉VCCO_14,DO3连接DQ3/HOLD#/IO3且需要外部4.7kΩ上拉VCCO_14,其余引脚为高阻态,可以悬空;并行模式下,FPGA首先通过D[00-07]判断配置位宽为x8/x16还是x32,按需求连接对应引脚,x16和x32模式不支持加密模式;主BPI模式下,FPGA首先你通过D[00-07]判断配置位宽为x8还是x16,D[16-31]用作A[00-15](多功能引脚);JTAG模式下,不使用;所有模式下,不用的引脚为高阻态,可以悬空;

- A[15:00]_14:主BPI模式下,用作地址线,A00位LSB,不用的高位地址线在配置期间同样会被驱动且配置完成后可以用作普通IO;并行模式下,用作D[16-31];其他模式下,为高阻态,可以悬空;

- PUDC_B_14:低电平使能配置期间的IPU(所有SelectIO),高电平禁止,需要直连或通过电阻(≤1kΩ)连接VCCO_14/GND,当连接GND时,上拉有效的时刻和商店顺序有关,因为在器件里边,该信号需要经过一级驱动才能传递到上拉电阻使能端,因此在需要立即上拉的场合下,建议引脚和对应Bank电源之间加入外部上拉电阻。配置前和配置期间该引脚禁止悬空;

- EMCCLK_14:主SPI模式下,可选外部时钟输入信号;从模式/JTAG模式下,该引脚被忽略,可以悬空;

- FCS_B_14:主SPI/主BPI模式下,连接FLASH的片选,且需要外接上拉(≤4.7kΩ,官方推荐2.4kΩ)到VCCO_14;其他模式下,为高阻态,可以悬空;

- RDWR_B_14:并行模式下的数据方向控制引脚,高电平时FPGA输出数据到总线上,低电平时外部控制器通过总线写入数据到FPGA;主并模式下,直连或通过电阻(≤1kΩ)连接GND;从并模式下,外部器件控制;其他模式下,该引脚为高阻态,可以悬空;

- CSO_B:主BPI(异步)/并行模式下,若存在下级器件,连接到下级器件的CSI_B上,通过通过330Ω电阻上拉到VCCO_14上,若不存在下级器件或独立器件,则为高阻态;串行模式下,作为DOUT使用(多功能引脚);其他模式下,为高阻态,可以悬空;

- DOUT:主SPI(x1)模式下,连接到下级器件的DIN上,否则高阻态;主BPI/并感性模式下,作为CSO_B使用;其他模式下,为高阻态,可以悬空;

- CSI_B_14:并行模式使能引脚,主并模式下直连或通过电阻(≤1kΩ)连接到GND;从并模式下,由外部控制器控制,并行级联模式下,连到上一级的CSO_B上;其他模式下,该引脚被忽略,可以悬空;

- ADV_B_15:主BPI模式下,针对支持地址有效功能的器件,连接FLASH的地址有效引脚且需要电阻(≤4.7kΩ)上拉VCCO_15,针对不支持地址有效功能器件,不要连接该引脚;其他模式下,为高阻态,可以悬空;

- A[28:16]_15:主BPI模式下,用作地址线,A00为LSB,不用的高位地址线在配置期间同样会被驱动且配置完成后可以作为普通IO;其他模式下,为高阻态,可以悬空;

- FOE_B_15:主BPI模式下,连接FLASH的OE引脚且需要电阻(≤4.7kΩ)上拉VCCO_15,其他模式下,为高阻态,可以悬空;

- FEW_B_15:主BPI模式下,连接FLASH的WE引脚且需要电阻(≤4.7kΩ)上拉VCCO_15,其他模式下,为高阻态,可以悬空;

- RS1_15/RS0_15:当配置回读被使能,FPGA在检测到配置错误时将RS0/RS1输出低电平;当MultiBoot配置被使能,FPGA可根据用户定义,在配置期间输出特定电平;其余情况下,RS0/RS1引脚为高阻态,可以悬空;同场景用在主BPI模式下,主SPI模式不支持。

特别说明下,并行菊花链模式中,第一个器件可配置为主BPI,后级所有器件需要配置为从并模式,首器件通过FCS_B连接外部FLASH(不用CSI_B),将CSO_B连到后级CSI_B中,后级其他器件通过CSI_B和CSO_B组成菊花链。

时钟IO

- SRCC:共2组4根时钟输入,可驱动BUFIO/BUFR/BUFG,不能连接BUFMR,单端时钟只能从_P引脚接入,且此时_N引脚不能再用做另一路单端时钟输入引脚,只能用作普通IO,不使用某个Bank的CC引脚功能时,该引脚可以用作普通IO;

- MRCC:共2组4根时钟输入,可驱动BUFIO/BUFR/BUFMR/BUFG,单端时钟只能从_P引脚接入,且此时_N引脚不能再用做另一路单端时钟输入引脚,只能用作普通IO,不使用某个Bank的CC引脚功能时,该引脚可以用作普通IO。

XADC(Bank 15)

- AD0P/AD0N~AD15P/AD15N:16个模拟输入引脚,Bank有0/1/2/3和8/9/10/11共8个通道。

其他IO

- DQS:DDR专用DQS引脚;

- VREF:DDR专用电压参考引脚。

Bank 34/35(HR)

电源

VCCO_34/35:可接1V2/1V5/1V8/2V5/3V3等多种电压,根据需要选择。

普通IO

Bank 34共32个普通IO;

Bank 35共20个普通IO。

时钟IO

同Bank 12,4个SRCC+4个MRCC。

其他IO

包含DQS/VREF等DDR专用引脚。

Bank 216(GTP)

校准

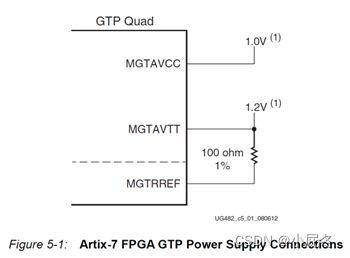

MGTRREF,用于GTP内部校准,MGTRREF通过100Ω电阻连接MGTAVTT。若不用GTP功能,应连接GND。

时钟

含两组差分时钟引脚,MGTREFCLK[n]P/N,接入外部差分时钟(需要电容耦合)。若不用GTP功能,应悬空。

数据

含4组差分收发引脚,MGTPTXP/N[n]、MGTPRXP/N[n],使用时需要电容耦合。若不使用GTP功能,接收端可以选择悬空(供电)或连GND(未供电),发送端应悬空。

电源

非GTP

包含VCCINT/VCCBRAM/VCCAUX/VCCO,VCCO属于Bank电源,此处不在说明。

- VCCINT:内核电源,1V0/0V95(-2LI);

- VCCBRAM:BRAM供电电源,1V0/0V95(-2LI);

- VCCAUX:辅助供电电源,1V8。

要求1:

上电顺序:VCCINT/VCCBRAM先上电,VCCAUX/VCCAUX_IO再上电,VCCO最后上电,若后两种电压相同,可以同时上电;

要求2:

下电顺序:下电顺序和上电顺序相反,大部分情况下都是同时下电。

要求3:

针对Bank 0和3V3 HR BANK的VCCO供电由如下限制:在上下电期间,VCCO和VCCAUX的压差高于2.625VV的事件不能超过TVCCO2VCCAUX(125℃最大典型值300ms)。

GTP

包含MGTAVCC/MGTAVTT。

- MGTAVCC:GTP模拟供电,1V0(≤10.3125GHz)/1V05(>10.3125GHz);

- MGTAVTT:GTP终端电路模拟供电,1V2。

要求:

上电顺序:VCCINT/MGTAVCC先上电,MGTAVTT后上电,VCCINT和MGTAVCC之间没有顺序要求,若不满足上述条件,上下电期间VMGTAVTT电流会变大;

当VMGTAVTT先于VMGTAVCC上电,且VMGTAVTT-VMGTAVCC>150mV,并且VMGTAVCC<0.7V,VMGTAVCC上电期间VMGTAVTT每一路收发器会增加460mA电流消耗,持续时间为0.3*TMGTAVCC(VMGTAVCC从0~90%消耗的时间),下电时也成立;

当VMGTAVTT先于VCCINT上电,且VMGTAVTT-VCCINT>150mV,并且VMGTAVCC<0.7V,VCCINT上电期间VMGTAVTT每一路收发器会增加460mA电流消耗,持续时间为0.3*TVCCINT(VCCINT从0~90%消耗的时间),下电时也成立。

硬件Checklist

| 序号 |

引脚名称 |

检查内容 |

| POWER |

||

| 1 |

VCCINT |

内核电源(1V0) |

| 2 |

VCCBRAM |

BRAM电源(1V0) |

| 3 |

VCCAUX |

辅助电源(1V8) |

| 4 |

VCCO_0/14/15 |

1V5/1V8/2V5/3V3可选,和SPI FLASH/BPI FLASH电源保持一致 |

| 5 |

VCCO_16 |

1V2/1V5/1V8/2V5/3V3可选 |

| 6 |

VCCO_34/35 |

1V2/1V5/1V8/2V5/3V3可选 |

| 7 |

VCCBATT_0 |

加密功能专用(电压:1V0~1V89),不用时接VCCAUX(1V8)或GND |

| XADC |

||

| 1 |

VCCADC_0 |

XADC模拟电源(1V8),串磁珠或接模拟电源,不用时接VCCAUX(1V8) |

| 2 |

GNDADC_0 |

XADC模拟地,串磁珠或接模拟地,不用时接GND |

| 3 |

VREFP_0 |

1V25外部基准(需滤波),或内部基准(GNDADC_0),不用时接GNDADC_0 |

| 4 |

VREFN_0 |

电压基准地,连接GNDADC_0 |

| 5 |

VP_0/VN_0 |

专用模拟输入引脚,不用时接GNDADC_0 |

| 6 |

AD[15:0]P/AD[15:0]N |

可选模拟输入引脚,7A50T有全部16个通道 |

| 7 |

DXP_0/DXN_0 |

内部温度二极管正/负引脚,不用时接GNDADC_0 |

| JTAG |

||

| 1 |

TCK_0 |

测试时钟引脚,连仿真器的TCK引脚,建议加TVS |

| 2 |

TMS_0 |

测试模式引脚,连仿真器的TMS引脚,建议加TVS |

| 3 |

TDO_0 |

测试数据输出引脚,连仿真器的TDO引脚,可级联后级TDI,建议加TVS |

| 4 |

TDI_0 |

测试数据输入,连仿真器的TDI引脚,可级联前级TDO,建议加TVS |

| Configuration |

||

| 1 |

CCLK_0 |

配置时钟引脚,接SPI FLASH的CLK,BPI/JTAG模式悬空 |

| 2 |

INIT_B_0 |

初始化完成引脚,低有效,外接4.7kΩ上拉至VCCO_0 |

| 3 |

PROGRAM_B_0 |

重配置引脚,低有效,外接4.7kΩ上拉至VCCO_0 |

| 4 |

CFGBVS_0 |

配置电平选择引脚,高电平(VCCO_0)对应3V3/2V5,低电平对应1V8/1V5 |

| 5 |

DONE_0 |

启动玩阿城引脚,含IPU(10kΩ),可以不外借330Ω上拉 |

| 6 |

M0_0/M1_0/M2_0 |

启动模式引脚,外接1kΩ上下来电阻,SPI/001,BPI/010,JTAG/101 |

| 7 |

D[15:0]_14 |

配置数据引脚,SPI x1/x2/x4用到D[03:00],D02/D03需外接4.7kΩ上拉;BPI x8/x16用到D[15:00],不用的引脚可以悬空 |

| 8 |

A[15:0]_14 |

配置地址引脚,BPI x8/x16作为地址线使用,A00位LSB |

| 9 |

PUDC_B_14 |

配置期间上拉使能引脚,外接1kΩ上拉,低电平使能上拉 |

| 10 |

EMCCLK_14 |

可选外部时钟输入引脚,作为主SPI模式下的外部时钟 |

| 11 |

FCS_B_14 |

FLASH片选引脚,适用于主SPI/主BPI模式 |

| 12 |

RDWR_B_14 |

并行模式读写控制引脚,主SPI/主BPI不使用,悬空 |

| 13 |

DOUT_B_14 |

FLASH级联引脚,适用于SPI x1模式,连接后级DIN,不用时悬空 |

| 14 |

CSO_B |

FLASH级联引脚,适用于BPI/并行模式,连接后级CSI,不用时悬空 |

| 15 |

CSI_B_14 |

并行模式是能引脚,主SPI/主BPI不使用,悬空 |

| 16 |

ADV_B_15 |

地址有效引脚,仅主BPI且支持ADV功能的FLASH适用,其他模式悬空 |

| 17 |

A[28:16]_15 |

配置地址引脚,用作主BPI模式的高位地址线 |

| 18 |

FOE_B_15 |

FLASH输出有效引脚,仅适用主BPI模式,主SPI模式悬空 |

| 19 |

FWE_B_15 |

FLASH写使能引脚,仅适用主BPI模式,主SPI模式悬空 |

| 20 |

RS0_15/RS1_15 |

版本选择引脚,仅适用主BPI且使能回读配置时,主SPI模式悬空 |

| Clock |

||

| 1 |

SRCC |

时钟输入引脚,不能连接BUFMR,单端时钟连接_P引脚 |

| 2 |

MRCC |

时钟输入引脚,能连接BUFMR,单端时钟连接_P引脚 |

| Memory |

||

| 1 |

DQS |

DDR等存储器的DQS引脚,接DDR的DQS引脚 |

| 2 |

VREF |

输入参考电压引脚,用于含差分输入缓冲器的单端引脚,接参考电源 |

| GTP |

||

| 1 |

MGTRREF |

电阻校准网络的偏置电流供电/校准电阻输入引脚

|

| 2 |

MGTREFCLK[1:0]P/N |

差分时钟输入引脚

|

| 3 |

MGTPTXP/N[3:0] |

差分数据发送引脚

|

| 4 |

MGTPRXP/N[3:0] |

差分数据接受引脚

|

| 5 |

MGTAVCC |

内部模拟电路供电,1V0(>10.3125Gbps时,调整为1V05)

不用该Bank时,该引脚可以悬空接GND。 |

| 6 |

MGTAVTT |

收发器终端电路模拟供电,1V2,要求同MGTAVCC。 |

| Digital IO |

||

| 1 |

IO_LXXY_#/IO_XX_# |

仅用作普通数字IO,无其他复用功能 |