【Verilog HDL】FPGA-testbench基础知识

欢迎来到FPGA专栏~testbench基础知识

- ☆* o(≧▽≦)o *☆嗨~我是小夏与酒

- ✨博客主页:小夏与酒的博客

- 该系列文章专栏:FPGA学习之旅

- 文章作者技术和水平有限,如果文中出现错误,希望大家能指正

- 欢迎大家关注! ❤️

![]()

目录-testbench基础知识

- 一、说明

- 二、testbench简单理解

- 三、testbench文件结构

-

- 3.1 声明仿真的单位和精度

- 3.2 宏定义

- 3.3 定义测试模块名

- 3.4 声明信号

- 3.5 模块实例化

- 3.6 使用initial或always产生激励信号

- 3.7 完整的testbench代码

- 四、补充语法

-

- 4.1 repeat循环

- 4.2 forever循环

- 4.3 仿真控制任务$stop

![]()

一、说明

在开发FPGA的过程中,需要掌握Verilog的核心语法并编写高质量的代码。【Verilog HDL】系列的文章便专注于Verilog语法的讲解和分析。文章参考书籍:《Verilog HDL设计实用教程》。

Verilog文件基本结构的知识学习参考文章:【Verilog HDL】FPGA-Verilog文件的基本结构。

在学习FPGA的过程中,既要学会使用开发工具、软件,会编写Verilog HDL,更要学会编写测试激励文件来对模块进行测试。本编文章讲解testbench文件的基础知识点。

二、testbench简单理解

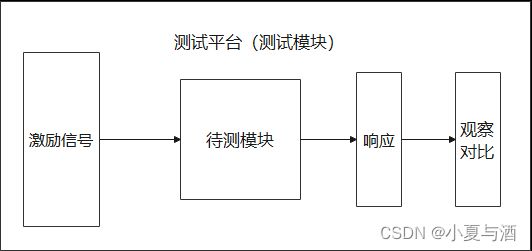

testbench,即测试平台、测试模块,有时也称为测试激励文件。

testbench的功能就是产生一些激励信号,施加到待测试的设计模块上,然后观察在这些激励信号的作用下模块的响应输出结果并分析正确性。(详细地说就是给待验证的设计添加激励,同时观察它的输出响应是否符合设计要求。)

testbench功能实现的大概流程图:

以简单的思维方式理解testbench:

目前的待测模块就是一个黑箱子,你不清楚它的内部结构,这个黑箱子只留出了信号输入端口和信号输出端口,只能在输入端对它施加激励,并在输出端观察输出信号。

而testbench就相当于一张实验室的桌子,桌子上放着信号产生器、程控电源等(激励信号);放着电路黑箱子(待测模块);示波器等观察信号的仪器(观察响应);以及若干杜邦线或者导线等。

我们将信号产生器的信号输出接入黑箱子的信号输入端,将示波器的信号线与黑箱子的输出端相连,打开信号产生器和示波器,改变输入信号,并在示波器上观察结果。

三、testbench文件结构

testbench文件的基本结构如下所示:

待测模块_tb.v:

//------------

//`timescale 仿真单位/仿真精度

`timescale xx/xx

//仿真文件模块名

module xx_tb;

//定义声明信号或变量

...

...

//例化设计模块

...

...

//使用always语句产生激励波形

...

...

//使用initial产生激励波形

initial begin

...

...

...

$stop;

end

endmodule

举个例子详细说明一下:

目前已经编写好了一个led闪烁的模块,我们需要对该模块进行测试,以确保模块设计的正确性,模块代码如下:

led_flash.v:

//------<模块代码>------

module led_flash(

input Clk;

input Rst_n;

output reg led

);

//定义led状态

parameter led_on = 1'b0;

parameter led_off = 1'b1;

//定义计数器寄存器

reg [24:0]cnt;

//定义计数器参数

parameter cnt_max = 24'd24_999_999;

parameter cnt_min = 24'd0;

parameter cnt_add = 1'b1;

//计数器

always@(posedge Clk or negedge Rst_n)begin

if(!Rst_n)

cnt <= cnt_min;

else if(cnt == cnt_max)

cnt <= cnt_min;

else

cnt <= cnt + cnt_add;

end

//led

always@(posedge Clk or negedge Rst_n)begin

if(!Rst_n)

led <= led_off;

else if(cnt == cnt_max)

led <= ~led;

else

led <= led;

end

endmodule

接下来根据上述模块编写测试激励文件。

3.1 声明仿真的单位和精度

`timescale时间刻度指令用来说明模块工作的时间单位和时间精度,基本语句如下:

`timescale 时间单位/时间精度

时间单位和时间精度可以以秒、毫秒、纳秒、皮秒或飞秒作为度量,具体数值可以选择1、10或100,如:

`timescale 10ns/1ns

该语句定义了当前模块中的仿真时间单位是10ns,仿真精度是1ns,语法上要求时间精度必须小于等于时间单位,即前面的数值要大于等于后面的数值。

测试模块中经常使用 #号 延迟来生成信号,例如:

`timescale 10ns/1ns

...

initial

begin

A = 0;B = 0;//初始值

#4 A = 1;//4时间单位后,即40ns

#5 B = 1;//5时间单位后,即50ns

#6 A = 0;//6时间单位后,即60nd

#7 $stop;//7时间单位后,即70ns

end

又如:

`timescale 1ns/1ns

当代码中出现#10时,代表的意思是延时10ns,由于仿真的精度为1ns,所以最低的延时精度只能到1ns,如果想要延时10.001ns,则需要更改仿真的精度(1ns=1000ps),代码如下:

`timescale 1ns/1ps

#10.001 rst_n = 0;

为了测试上述led闪烁模块,定义如下时间单位和时间精度:

`timescale 1ns/1ns

3.2 宏定义

宏定义采用 `define 来进行指定,把某个指定的标识符用来代表一个字符串,整个标识符在整个文件中都表示所指代的字符串,语法如下:

`define 标识符 字符串 //注意句末无分号

对于上述led闪烁模块,需要产生一个时钟信号给它,为了方便进行全文的修改,我们对时钟信号的周期进行宏定义:

`define clock_period 20

如果不想让宏定义生效,可以使用 `undef 指令取消前面定义的宏:

`define WIDTH 16

`undef WIDTH //此条语句之后,WIDTH失效

reg [`WIDTH-1:0] data; //报错,因为宏定义已经取消

3.3 定义测试模块名

定义模块名的关键字为module,同时测试模块以endmodule结束,代码如下:

module led_flash_tb;

...

...

...

endmodule

模块名的命名方式一般在被测模块名后面加上 _tb,或者在被测模块名前面加上tb_,表示为哪个模块提供激励测试文件,通常激励文件不需要定义输入和输出端口。代码中定义的常量有时需要频繁的修改,为了方便修改,可以把常量定义成参数的形式,定义参数的关键字为 parameter。

3.4 声明信号

在testbench中,信号常用的类型为reg类型和wire类型,reg类型表示激励信号,wire类型表示输出信号。

定义led闪烁测试模块中的输入和输出信号:

//时钟信号和复位信号均需要输入给待测模块

reg Clk;

reg Rst_n;

//led信号为待测模块的输出信号

wire led;

3.5 模块实例化

例化的设计模块是指被测模块,例化被测模块的目的是把被测模块和激励模块实例化起来,并且把被测模块的端口与激励模块的端口进行相应的连接,使得激励可以输入到被测模块。

如果被测模块是由多个模块组成的,激励模块中只需要例化多个模块的顶层模块。

将led闪烁模块实例化:

led_flash led_flash0(

.Clk(Clk);

.Rst_n(Rst_n);

.led(led)

);

在实例化模块中,左侧带“.” 的信号为 led 模块定义的端口信号,右侧括号内的信号为激励模块中定义的信号,其信号名可以和被测模块中的信号名一致,也可以不一致,命名一致的好处是便于理解激励模块和被测模块信号之间的对应关系。

3.6 使用initial或always产生激励信号

产生时钟激励信号:

initial Clk = 1;

always#(`clock_period/2) Clk = ~Clk;

产生led闪烁测试模块的其余激励信号:

initial begin

Rst_n = 0;

#200

Rst_n = 1;

#(`clock_period*200)

$stop;

end

3.7 完整的testbench代码

led_flash_tb.v:

//------<测试代码>------

`timescale 1ns/1ns

`define clock_period 20

module led_flash_tb;

reg Clk;

reg Rst_n;

wire led;

led_flash led_flash0(

.Clk(Clk);

.Rst_n(Rst_n);

.led(led)

);

initial Clk = 1;

always#(`clock_period/2) Clk = ~Clk;

initial begin

Rst_n = 0;

#200

Rst_n = 1;

#(`clock_period*200)

$stop;

end

endmodule

四、补充语法

repeat循环和forever循环语句只适用于testbench的编写。

4.1 repeat循环

repeat循环的功能是把循环体语句执行某些次数,基本格式:

repeat(次数)

begin

循环体语句

end

该语句的基本使用案例链接:【FPGA零基础学习之旅#7】BCD计数器设计。

测试代码:

`timescale 1ns/1ns

`define clock_period 20

module BCD_Counter_tb;

reg Clk;

reg Rst_n;

reg Cin;

wire Cout;

wire [3:0]q;

BCD_Counter BCD_Counter0(

.Clk(Clk), //系统时钟信号

.Rst_n(Rst_n), //系统复位信号

.Cin(Cin), //进位输入信号

.Cout(Cout), //进位输出信号

.q(q) //计数器值

);

initial Clk = 1;

always#(`clock_period/2) Clk = ~Clk;

initial begin

Rst_n = 1'b0;

Cin = 1'b0;

#(`clock_period*20);

Rst_n = 1;

#(`clock_period*20);

repeat(30)begin

Cin = 1'b1;

#(`clock_period*1);

Cin = 1'b0;

#(`clock_period*5);

end

#(`clock_period*20);

$stop;

end

endmodule

其中,该部分代码表示执行循环体中的语句30次,且循环体的语句表示生成一个占空比为1:5的脉冲信号:

repeat(30)begin

Cin = 1'b1;

#(`clock_period*1);

Cin = 1'b0;

#(`clock_period*5);

end

脉冲信号是一种离散信号,形状多种多样,与普通模拟信号(如正弦波)相比,波形之间在Y轴不连续(波形与波形之间有明显的间隔),但具有一定的周期性是它的特点。最常见的脉冲波是矩形波(也就是方波)。脉冲信号可以用来表示信息,也可以用来作为载波,比如脉冲调制中的脉冲编码调制(PCM)、脉冲宽度调制(PWM)等等,还可以作为各种数字电路、高性能芯片的时钟信号。

4.2 forever循环

forever循环表示永远循环,直到仿真结束为止,相当于判断条件永远为真。forever循环语句中需要添加时序控制,否则就会陷入死循环。

可以用forever循环语句来编写文章【FPGA零基础学习之旅#9】状态机基础知识中Hello例程的testbench:

reg [7:0]ASCII;

Hello Hello0(

.Clk(Clk),

.Rst_n(Rst_n),

.data(ASCII),

.led(led)

);

initial begin

Rst_n = 0;

ASCII = 0;

#(`clock_period*20);

Rst_n = 1;

#(`clock_period*20 + 1);

forever begin

ASCII = "I";

#(`clock_period);

ASCII = "A";

#(`clock_period);

ASCII = "M";

#(`clock_period);

ASCII = "X";

#(`clock_period);

ASCII = "i";

#(`clock_period);

ASCII = "a";

#(`clock_period);

ASCII = "o";

#(`clock_period);

ASCII = "M";

#(`clock_period);

ASCII = "e";

#(`clock_period);

ASCII = "i";

#(`clock_period);

ASCII = "g";

#(`clock_period);

ASCII = "e";

#(`clock_period);

ASCII = "H";

#(`clock_period);

ASCII = "E";

#(`clock_period);

ASCII = "M";

#(`clock_period);

ASCII = "l";

#(`clock_period);

ASCII = "H";

#(`clock_period);

ASCII = "E";

#(`clock_period);

ASCII = "L";

#(`clock_period);

ASCII = "L";

#(`clock_period);

ASCII = "O";

#(`clock_period);

ASCII = "H";

#(`clock_period);

ASCII = "e";

#(`clock_period);

ASCII = "l";

#(`clock_period);

ASCII = "l";

#(`clock_period);

ASCII = "o";

#(`clock_period);

ASCII = "l";

end

end

比较常见的还有使用forever循环生成时钟信号,如:

//------

initial begin

Clk = 1;

forever #10 Clk = ~Clk;

end

同时,使用always块生成时钟信号的代码:

//------

initial Clk = 1;

always #10 Clk = ~Clk;

上述的两种写法都是生成了周期为20个时间单位的Clk信号,效果是一样的。两种写法均可以在测试模块中使用,并无优劣之分。

4.3 仿真控制任务$stop

$stop的功能是停止当前仿真,注意是停止,而不是退出,仿真器会把仿真到该语句的仿真运行完,然后停止仿真(任务$finish的功能则是停止仿真并退出仿真器),等待下一步命令,此时依然停留在仿真器的仿真界面中,一些仿真窗口(例如波形窗口等)依然保留着,仿真的结果也是保留的。

设计者在自己的计算机上完成仿真而且代码规模较小时,一般都是使用$stop任务作为仿真结束的标志语句,然后根据仿真窗口来查看仿真结果。

需要注意的是,如果使用了forever循环语句产生持续不断的信号时,不需要在仿真中使用$stop,例如上述中Hello例程的完整testbench:

Hello_tb.v.:

`timescale 1ns/1ns

`define clock_period 20

module Hello_tb;

reg Clk;

reg Rst_n;

reg [7:0]ASCII;

wire led;

Hello Hello0(

.Clk(Clk),

.Rst_n(Rst_n),

.data(ASCII),

.led(led)

);

initial Clk = 1;

always#(`clock_period/2)Clk = ~Clk;

initial begin

Rst_n = 0;

ASCII = 0;

#(`clock_period*200);

Rst_n = 1;

#(`clock_period*200 + 1);

forever begin

ASCII = "I";

#(`clock_period);

ASCII = "A";

#(`clock_period);

ASCII = "M";

#(`clock_period);

ASCII = "X";

#(`clock_period);

ASCII = "i";

#(`clock_period);

ASCII = "a";

#(`clock_period);

ASCII = "o";

#(`clock_period);

ASCII = "M";

#(`clock_period);

ASCII = "e";

#(`clock_period);

ASCII = "i";

#(`clock_period);

ASCII = "g";

#(`clock_period);

ASCII = "e";

#(`clock_period);

ASCII = "H";

#(`clock_period);

ASCII = "E";

#(`clock_period);

ASCII = "M";

#(`clock_period);

ASCII = "l";

#(`clock_period);

ASCII = "H";

#(`clock_period);

ASCII = "E";

#(`clock_period);

ASCII = "L";

#(`clock_period);

ASCII = "L";

#(`clock_period);

ASCII = "O";

#(`clock_period);

ASCII = "H";

#(`clock_period);

ASCII = "e";

#(`clock_period);

ASCII = "l";

#(`clock_period);

ASCII = "l";

#(`clock_period);

ASCII = "o";

#(`clock_period);

ASCII = "l";

end

end

endmodule

![]()

结尾

- ❤️ 感谢您的支持和鼓励!

- 您可能感兴趣的内容:

- 【FPGA零基础学习之旅#9】状态机基础知识

- 【FPGA零基础学习之旅#8】阻塞赋值与非阻塞赋值讲解

- 【Arduino TinyGo】【最新】使用Go语言编写Arduino-环境搭建和点亮LED灯

- 【全网首发开源教程】【Labview机器人仿真与控制】Labview与Solidworks多路支配关系-四足爬行机器人仿真与控制