【CPU】关于x86、x86_64/x64、amd64和arm64/aarch64

为什么叫x86和x86_64和AMD64?

为什么大家叫x86为32位系统?

为什么软件版本会注明 for amd64版本,不是intel64呢?

x86是指intel的开发的一种32位指令集,从386开始时代开始的,一直沿用至今,是一种cisc指令集,所有intel早期的cpu,amd早期的cpu都支持这种指令集,intel官方文档里面称为“IA-32”

x84_64是x86 CPU开始迈向64位的时候,有2选择:

1、向下兼容x86。

2、完全重新设计指令集,不兼容x86。

AMD抢跑了,比Intel率先制造出了商用的兼容x86的CPU,AMD称之为AMD64,抢了64位PC的第一桶金,得到了用户的认同。

Intel选择了设计一种不兼容x86的全新64为指令集,称之为IA-64(这玩意似乎就是安腾),但是比amd晚了一步,而且IA-64也挺惨淡的,因为是全新设计的CPU,没有编译器,也不支持windows(微软把intel给忽悠了,承诺了会出安腾版windows server版,但是迟迟拿不出东西)。后来不得不在时机落后的情况下也开始支持AMD64的指令集,但是换了个名字,叫x86_64,表示是x86指令集的64扩展,大概是不愿意承认这玩意是AMD设计出来的。

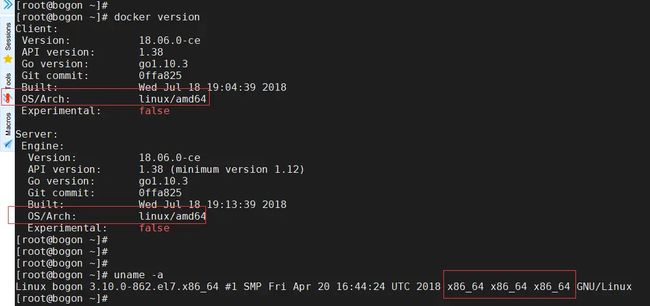

实际上,x86_64,x64,AMD64基本上是同一个东西,我们现在用的intel/amd的桌面级CPU基本上都是x86_64,与之相对的arm,ppc等都不是x86_64。

x86、x86_64主要的区别就是32位和64位的问题,x86中只有8个32位通用寄存器,eax,ebx,ecx,edx, ebp, esp, esi, edi。

x86_64把这8个通用寄存器扩展成了64位的,并且比x86增加了若干个寄存器(好像增加了8个,变成了总共16个通用寄存器)。同样的MMX的寄存器的位数和数量也进行了扩展。此外cpu扩展到64位后也能支持更多的内存了,等等许多好处。

对于普通程序来说,CPU位数的扩展、寄存器数量的增加不会带来明显的性能提升,比如IE浏览器、Office办公这类的软件。特定的程序很能够充分利用64位CPU、更多的寄存器带来的优势,比如MMX除了能提升多媒体程序的性能,对矩阵、多项式、向量计算都能带来提升,更多的MMX寄存器、更大的寄存器字长都有利于SIMD指令的执行,能够提升CPU对数据的吞吐量(RISC指令集的CPU动不动就有数百个寄存器,可以有效的缓存中间计算结果,不需要把中间结果写入内存,从而减少内存访问次数,显著提升性能)

x86

x86架构(The x86 architecture)是微处理器执行的计算机语言指令集,指一个intel通用计算机系列的标准编号缩写,也标识一套通用的计算机指令集合。

1978年6月8日,Intel发布了新款16位微处理器“8086”,也同时开创了一个新时代:x86架构诞生了。

在40年的发展史中,x86家族不断壮大,从桌面转战笔记本、服务器、超级计算机、编写设备,期间还挫败或者限制了很多竞争对手的发展,让不少处理器厂商及其架构技术成为历史名字,即使有些封闭发展的也难以为继,比如苹果就已经放弃PowerPC了。

AMD64/x86-64

x86-64有时会简称为“x64”,是64位微处理器架构及其相应指令集的一种,也是Intel x86架构的延伸产品。

“x86-64”1999由AMD设计,AMD 首次公开 64 位集以扩充给 IA-32,称为 x86-64(后来改名为 AMD64)。 AMD64架构在IA-32上新增了64位寄存器,并兼容早期的16位和32位软件,可使现有以x86为对象的编译器容易转为AMD64版本。

由于AMD64和Intel64基本上一致,很多软硬件产品都使用一种不倾向任何一方的词汇来表明它们对两种架构的同时兼容。出于这个目的,AMD对这种CPU架构的原始称呼 - “x86-64”被不时地使用,还有变体“x86_64”。其他公司如微软和Sun在营销资料中使用“x64”作为对“x86-64”的缩写。

许多操作系统及产品,尤其那些是在Intel进入这块市场之前就引入“x86-64”支持的,使用“AMD64”或“amd64”同时指代AMD64和Intel64。

现在的x86 CPU在位数上有32/64bit之分,在ARCH上有又x86/x86_64/x64/i386/IA32/IA64/amd64

最近又新出来一个x32,还好不是ARCH,只是ABI,没有那么混乱。

先说一下x86的这些arch,不要求很严格的话,基本上可以用下面的公式来表达:

x86=i386=IA32

amd64=x86_64=x64!=IA64

其实这两个等式里很多都是别名,严格说的话,x86的世界里只存在x86/x86_64/IA64三种架构。

当年AMD先于Intel推出向下兼容的amd64 CPU,而Intel推出的不兼容32位系统的IA64惨淡收场(被MS放了鸽子),后来Intel在指令上支持了amd64,不过不愿意叫amd64,改了个名字x86_64。

再说64bit/32bit的兼容性问题:

现在的64bit CPU实际上都做了兼容32bit的特殊设计,所以64bit的CPU上运行32bit的软件(包括kernel/app, driver除外)是没有问题。反过来,32bit的CPU上运行64bit的软件是不可以的。

最后说重点,64bit相比32bit的性能优势:

这里不考虑64bit硬件上运行32bit软件的这种过度方式。

从架构上来说,64bit拥有64bit 的register和64bit的bus,在数据传输效率上比32bit要高不少;另外,64bit地址总线的寻址空间突破了4G的限制。

所以,对于大内存,密集数据运算的应用场景,64bit的优势是非常明显的。网上有一些benchmark,这里不贴了。

但是,对于小内存系统,64bit的CPU在某些状况下可能比32bit CPU的效率更低。

因为64 bit的CPU的地址是64位的,指针是64位的,编译生成的二进制文件更大,运行时占用的内存更多;另一方面,因为64位地址的问题,cache中能存放的指令就更少,所以更容易导致cache的miss。

所以在某些应用场景,64 bitCPU的更大的寻址空间,更快的数据传递,更快的浮点运算的特性, 与其64 bit的地址/指针所导致的cache miss的特性,始终并存。

为了充分利用64的优势,又避免64bit地址导致的cache miss的问题,Intel提出了x32 ABI的概念。

x32不是一个ARCH,是一个ABI。

x32可以充分的使用64 bit硬件的64 bit寄存器,64bit总线,以及64bit新增的指令,从而获得更快的数据处理速度。

同时x32又使用32bit的地址/pointer,32bit的C数据类型,因此cache miss并不会增加。

x32是一个ABI,其设计到的部分包括:kernel的support,toolchain的support,system lib的support。现在kernel(from 3.4)和toolchain的support都已经OK。

ARM,AMD,X86,AArch64的概念

AMD,中文名(超威)超微半导体,是除了英特尔以外最大的x86架构微处理供应商,也是除了英伟达以外仅有的独立图形处理供应商。

x86泛指一系列由英特尔公司开发的处理器的架构,最早为1978年面世的“Intel 8086”CPU。早期的处理器均是以此格式来命名,如Intel 8086,80186,80286,80386,80486,这些架构被统称为x86。由于数字不能被注册成为商标,因此公司每当有新的处理器使用,均会采用可注册的名称,如Pentium。

基于x86的32位架构(常被称为i386,x86),IA-32,而基于x86的64位架构,x86-64常称为AMD64或Intel64。最早是由AMD公司首先根据x86的架构生产出了64位的处理器,但是由于是竞争关系,Intel公司不愿意承认AMD64,近些年才推出了Intel64

ARM(英文为Advanced RISC Machine,或Acorn RISC Machine)也是一个架构,非常适用于移动通信这种低成本,高性能,低耗电的领域。ARM的公司为安谋控股(ARM Holding plc),又称为ARM公司,总部位于剑桥的设计与软件公司,现在已被日本的软银公司收购,后者同时也是国内互联网巨头阿里巴巴的最大股东。

AArch64是ARMv8的一种执行状态。

为了更广泛地向企业领域推进,需要引入 64 位构架,同时也需要在 ARMv8 架构中引入新的 AArch64 执行状态。

AArch64 不是一个单纯的 32 位 ARM 构架扩展,而是 ARMv8 内全新的构架,完全使用全新的 A64 指令集。这些都源自于多年对现代构架设计的深入研究。更重要的是, AArch64 作为一个分离出的执行状态,意味着一些未来的处理器可能不支持旧的 AArch32 执行状态。

虽然最初的 64 位 ARM 处理器将会完全向后兼容,但我们大胆且前瞻性地将 AArch64 作为在 ARMv8 处理器中唯一的执行状态。我们在这些系统中将不支持 32 位执行状态, 这将使许多有益的实现得到权衡,如默认情况下,使用一个较大的 64K 大小的页面,并会使得纯净的 64 位 ARM 服务器系统不受遗留代码的影响。立即进行这种划分是很重要的,因为有可能在未来几年内将出现仅支持 64 位的服务器系统。没有必要在新的 64 位架构中去实现一个完整的 32 位流水线,这将会提高未来 ARM 服务器系统的能效。

这样回想起来, AArch64 作为在 Fedora ARM 项目中被支持的 ARM 构架是一个很自然的过程: armv5tel、armv7hl、aarch64。新的架构被命名为:aarch64,这同 ARM 自己选择的主线命名方式保持一致,同时也考虑到了 ARM 架构名与 ARM 商标分开的期望。

ARMv8-A 将 64 位架构支持引入 ARM 架构中,其中包括:

64 位通用寄存器、SP(堆栈指针)和 PC(程序计数器)

64 位数据处理和扩展的虚拟寻址

两种主要执行状态:

AArch64 - 64 位执行状态,包括该状态的异常模型、内存模型、程序员模型和指令集支持

AArch32 — 32 位执行状态,包括该状态的异常模型、内存模型、程序员模型和指令集支持

这些执行状态支持三个主要指令集:

A32(或 ARM):32 位固定长度指令集,通过不同架构变体增强部分 32 位架构执行环境现在称为 AArch32。

T32 (Thumb) 是以 16 位固定长度指令集的形式引入的,随后在引入 Thumb-2 技术时增强为 16 位和 32 位混合长度指令集。部分 32 位架构执行环境现在称为 AArch32。

A64:提供与 ARM 和 Thumb 指令集类似功能的 32 位固定长度指令集。随 ARMv8-A 一起引入,它是一种 AArch64 指令集。

ARM ISA 不断改进,以满足前沿应用程序开发人员日益增长的要求,同时保留了必要的向后兼容性,以保护软件开发投资。在 ARMv8-A 中,对 A32 和 T32 进行了一些增补,以保持与 A64 指令集一致。