RISC-V常用指令总结(附完整PDF)

在设计CPU的过程中,整理了RISC-V指令集,方便在设计和使用CPU的时候查询。

链接:https://pan.baidu.com/s/1q9ttXjjx2mJsTvg2ZJgjiQ

提取码:72xa

CONTENT

CONTENT

Revision History

1 Register File

1.1 GPR

1.2 FGPR

1.3 Vector Registers

1.3.1 Vector CSRs

1.3.1.1 Vector type register (vtype)

1.3.1.2 Vector Length Register (vl)

1.3.2 Vector General Purpose Registers (VGPR)

1.3.3 Mapping of Vector Elements to Vector Register State

1.3.3.1 Mapping with LMUL=1

1.3.3.2 Mapping with LMUL > 1

1.3.3.3 Mask Register Layout

1.4 PC

1.5 CSRs

2 RISCV32-IMACF Instructions

2.1 RISCV32-I

2.1.1 Load and Store Instructions

2.1.1.1 lb rd, offset(rs1)

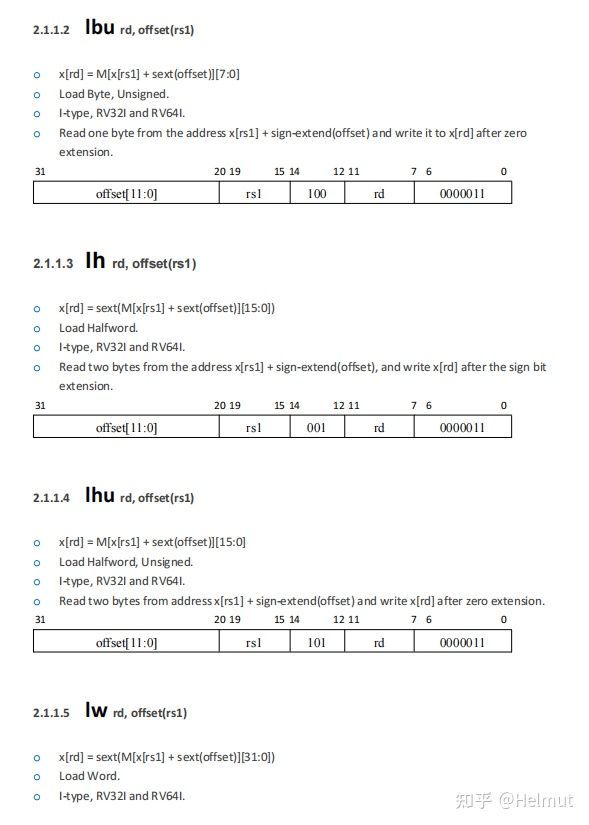

2.1.1.2 lbu rd, offset(rs1)

2.1.1.3 lh rd, offset(rs1)

2.1.1.4 lhu rd, offset(rs1)

2.1.1.5 lw rd, offset(rs1)

2.1.1.6 sb rs2, offset(rs1)

2.1.1.7 sh rs2, offset(rs1)

2.1.1.8 sw rs2, offset(rs1)

2.1.2 Integer Computational Instructions

2.1.2.1 sll rd, rs1, rs2

2.1.2.2 slli rd, rs1, shamt

2.1.2.3 srl rd, rs1, rs2

2.1.2.4 srli rd, rs1, shamt

2.1.2.5 sra rd, rs1, rs2

2.1.2.6 srai rd, rs1, shamt

2.1.2.7 add rd, rs1, rs2

2.1.2.8 addi rd, rs1, immediate

2.1.2.9 sub rd, rs1, rs2

2.1.2.10 lui rd, immediate

2.1.2.11 auipc rd, immediate

2.1.2.12 and rd, rs1, rs2

2.1.2.13 andi rd, rs1, immediate

2.1.2.14 or rd, rs1, rs2

2.1.2.15 ori rd, rs1, immediate

2.1.2.16 xor rd, rs1, rs2

2.1.2.17 xori rd, rs1, immediate

2.1.2.18 slt rd, rs1, rs2

2.1.2.19 sltu rd, rs1, rs2

2.1.2.20 slti rd, rs1, immediate

2.1.2.21 sltiu rd, rs1, immediate

2.1.3 Control Transfer Instructions

2.1.3.1 beq rs1, rs2, offset

2.1.3.2 bne rs1, rs2, offset

2.1.3.3 blt rs1, rs2, offset

2.1.3.4 bge rs1, rs2, offset

2.1.3.5 bltu rs1, rs2, offset

2.1.3.6 bgeu rs1, rs2, offset

2.1.3.7 jal rd, offset

2.1.3.8 jalr rd, offset(rs1)

2.1.4 Misc-mem instructions

2.1.4.1 fence pred, succ

2.1.4.2 fence.i

2.1.4.3 sfence.vma rs1, rs2

2.1.5 Control and Status Register Instructions

2.1.5.1 csrrw rd, csr, zimm[4:0]

2.1.5.2 csrrs rd, csr, rs1

2.1.5.3 csrrc rd, csr, rs1

2.1.5.4 csrrwi rd, csr, zimm[4:0]

2.1.5.5 csrrsi rd, csr, zimm[4:0]

2.1.5.6 csrrci rd, csr, zimm[4:0]

2.1.6 Environment Call and Breakpoints

2.1.6.1 ecall

2.1.6.2 ebreak

2.1.7 Trap-Return Instructions

2.1.7.1 mret

2.1.7.2 sret

2.1.8 Wait for Interrupt

2.1.8.1 wfi

2.2 RISCV32-M

2.2.1 mul rd, rs1, rs2

2.2.2 mulh rd, rs1, rs2

2.2.3 mulhsu rd, rs1, rs2

2.2.4 mulhu rd, rs1, rs2

2.2.5 div rd, rs1, rs2

2.2.6 divu rd, rs1, rs2

2.2.7 rem rd, rs1, rs2

2.2.8 remu rd, rs1, rs2

2.3 RISCV32-C

2.3.1 Load and Store Instructions

2.3.1.1 c.lw rd’, uimm(rs1’)

2.3.1.2 c.sw rs2’, uimm(rs1’)

2.3.1.3 c.lwsp rd, uimm(x2)

2.3.1.4 c.swsp rs2, uimm(x2)

2.3.2 Control Transfer Instructions

2.3.2.1 c.beqz rs1’, offset

2.3.2.2 c.bnez rs1’, offset

2.3.2.3 c.j offset

2.3.2.4 c.jr rs1

2.3.2.5 c.jal offset

2.3.2.6 c.jalr rs1

2.3.2.7 c.ebreak

2.3.3 Integer Computational Instructions

2.3.3.1 c.add rd, rs2

2.3.3.2 c.addi rd, imm

2.3.3.3 c.sub rd’, rs2’

2.3.3.4 c.addi16sp imm

2.3.3.5 c.addi4spn rd’, uimm

2.3.3.6 c.and rd’, rs2’

2.3.3.7 c.andi rd’, imm

2.3.3.8 c.or rd’, rs2’

2.3.3.9 c.xor rd’, rs2’

2.3.3.10 c.slli rd, uimm

2.3.3.11 c.srli rd’, uimm

2.3.3.12 c.srai rd’, uimm

2.3.3.13 c.mv rd, rs2

2.3.3.14 c.li rd, imm

2.3.3.15 c.lui rd, imm

2.3.4 Floating Point Instructructions

2.3.4.1 c.flw rd’, uimm(rs1’)

2.3.4.2 c.flwsp rd, uimm(x2)

2.3.4.3 c.fsw rs2’, uimm(rs1’)

2.3.4.4 c.fswsp rs2, uimm(x2)

2.4 RISCV-F

2.4.1 Single-Precision Floating-Point Load and Store Instructions

2.4.1.1 flw rd, offset(rs1)

2.4.1.2 fsw rs2, offset(rs1)

2.4.2 Single-Precision Floating-Point Computational Instructions

2.4.2.1 fmadd.s rd, rs1, rs2, rs3

2.4.2.2 fmsub.s rd, rs1, rs2, rs3

2.4.2.3 fnmadd.s rd, rs1, rs2, rs3

2.4.2.4 fnmsub.s rd, rs1, rs2, rs3

2.4.2.5 fadd.s rd, rs1, rs2

2.4.2.6 fsub.s rd, rs1, rs2

2.4.2.7 fmul.s rd, rs1, rs2

2.4.2.8 fdiv.s rd, rs1, rs2

2.4.2.9 fsqrt.s rd, rs1, rs2

2.4.2.10 fmin.s rd, rs1, rs2

2.4.2.11 fmax.s rd, rs1, rs2

2.4.3 Single-Precision Floating-Point Conversion and Move Instructions

2.4.3.1 fcvt.w.s rd, rs1, rs2

2.4.3.2 fcvt.wu.s rd, rs1, rs2

2.4.3.3 fcvt.s.w rd, rs1, rs2

2.4.3.4 fcvt.s.wu rd, rs1, rs2

2.4.3.5 fsgnj.s rd, rs1, rs2

2.4.3.6 fsgnjn.s rd, rs1, rs2

2.4.3.7 fsgnjx.s rd, rs1, rs2

2.4.3.8 fmv.x.w rd, rs1, rs2

2.4.3.9 fmv.w.x rd, rs1, rs2

2.4.4 Single-Precision Floating-Point Compare Instructions

2.4.4.1 feq.s rd, rs1, rs2

2.4.4.2 flt.s rd, rs1, rs2

2.4.4.3 fle.s rd, rs1, rs2

2.4.5 Single-Precision Floating-Point Classify Instruction

2.4.5.1 fclass.s rd, rs1

3 RISCV64-IMACD Instructions

3.1 RISCV64-I

3.1.1 lwu rd, offset(rs1)

3.1.2 ld rd, offset(rs1)

3.1.3 sd rs2, offset(rs1)

3.1.4 addw rd, rs1, rs2

3.1.5 addiw rd, rs1, immediate

3.1.6 subw rd, rs1, rs2

3.1.7 sllw rd, rs1, rs2

3.1.8 slliw rd, rs1, shamt

3.1.9 sraw rd, rs1, rs2

3.1.10 sraiw rd, rs1, shamt

3.1.11 srliw rd, rs1, shamt

3.1.12 srlw rd, rs1, rs2

3.2 RISCV64-M

3.2.1 mulw rd, rs1, rs2

3.2.2 divw rd, rs1, rs2

3.2.3 divuw rd, rs1, rs2

3.2.4 remw rd, rs1, rs2

3.2.5 remuw rd, rs1, rs2

3.3 RISCV64-A

3.3.1 lr.d rd, (rs1)

3.3.2 sc.d rd, rs2, (rs1)

3.3.3 amoadd.d rd, rs2, (rs1)

3.3.4 amoand.d rd, rs2, (rs1)

3.3.5 amomax.d rd, rs2, (rs1)

3.3.6 amomaxu.d rd, rs2, (rs1)

3.3.7 amomin.d rd, rs2, (rs1)

3.3.8 amominu.d rd, rs2,(rs1)

3.3.9 amominu.w rd, rs2, (rs1)

3.3.10 amoor.d rd, rs2, (rs1)

3.3.11 amoswap.d rd, rs2, (rs1)

3.3.12 amoxor.d rd, rs2, (rs1)

3.4 RISCV-D

3.4.1 fld rd, offset(rs1)

3.4.2 fsd rs2, offset(rs1)

3.4.3 fmadd.d rd, rs1, rs2, rs3

3.4.4 fmsub.d rd, rs1, rs2, rs3

3.4.5 fnmsub.d rd, rs1, rs2, rs3

3.4.6 fnmadd.d rd, rs1, rs2, rs3

3.4.7 fadd.d rd, rs1, rs2

3.4.8 fsub.d rd, rs1, rs2

3.4.9 fmul.d rd, rs1, rs2

3.4.10 fdiv.d rd, rs1, rs2

3.4.11 fsqrt.d rd, rs1, rs2

3.4.12 fsgnj.d rd, rs1, rs2

3.4.13 fsgnjn.d rd, rs1, rs2

3.4.14 fsgnjx.d rd, rs1, rs2

3.4.15 fmin.d rd, rs1, rs2

3.4.16 fmax.d rd, rs1, rs2

3.4.17 fcvt.s.d rd, rs1, rs2

3.4.18 fcvt.d.s rd, rs1, rs2

3.4.19 fcvt.w.d rd, rs1, rs2

3.4.20 fcvt.wu.d rd, rs1, rs2

3.4.21 fcvt.d.w rd, rs1, rs2

3.4.22 fcvt.d.wu rd, rs1, rs2

3.4.23 feq.d rd, rs1, rs2

3.4.24 flt.d rd, rs1, rs2

3.4.25 fle.d rd, rs1, rs2

3.4.26 fmv.d.x rd, rs1, rs2

3.4.27 fmv.x.d rd, rs1, rs2

3.4.28 fcvt.d.l rd, rs1, rs2

3.4.29 fcvt.d.lu rd, rs1, rs2

3.4.30 fcvt.l.d rd, rs1, rs2

3.4.31 fcvt.l.s rd, rs1, rs2

3.4.32 fcvt.lu.d rd, rs1, rs2

3.4.33 fcvt.lu.s rd, rs1, rs2

3.4.34 fcvt.s.l rd, rs1, rs2

3.4.35 fcvt.s.lu rd, rs1, rs2

3.4.36 fclass.d rd, rs1, rs2

3.5 RISCV64-C

3.5.1 c.ld rd’, uimm(rs1’)

3.5.2 c.ldsp rd, uimm(x2)

3.5.3 c.sd rs2’, uimm(rs1’)

3.5.4 c.sdsp rs2, uimm(x2)

3.5.5 c.addw rd’, rs2’

3.5.6 c.addiw rd, imm

3.5.7 c.subw rd’, rs2’

3.5.8 c.fld rd’, uimm(rs1’)

3.5.9 c.fldsp rd, uimm(x2)

3.5.10 c.fsd rs2’, uimm(rs1’)

3.5.11 c.fsdsp rs2, uimm(x2)

4 RISCV Pseudo-Instructions

4.1.1 nop

4.1.2 neg rd, rs2

4.1.3 negw rd, rs2

4.1.4 snez rd, rs2

4.1.5 sltz rd, rs1

4.1.6 sgtz rd, rs2

4.1.7 beqz rs1, offset

4.1.8 bnez rs1, offset

4.1.9 blez rs2, offset

4.1.10 bgez rs1, offset

4.1.11 bltz rs2, offset

4.1.12 bgtz rs1, offset

4.1.13 j offset

4.1.14 jr rs1

4.1.15 ret

4.1.16 tail symbol

4.1.17 rdcycle rd

4.1.18 rdcycleh rd

4.1.19 rdinstret rd

4.1.20 rdinstreth rd

4.1.21 rdtime rd

4.1.22 rdtimeh rd

4.1.23 csrr rd, csr

4.1.24 csrc csr, rs1

4.1.25 csrci csr, zimm[4:0]

4.1.26 csrs csr, rs1

4.1.27 csrsi csr, zimm[4:0]

4.1.28 csrw csr, rs1

4.1.29 csrwi csr, zimm[4:0]

4.1.30 frcsr rd

4.1.31 fscsr rd, rs1

4.1.32 frrm rd

4.1.33 fsrm rd, rs1

4.1.34 frflags rd

4.1.35 fsflags rd, rs1

4.1.36 lla rd, symbol

4.1.37 la rd, symbol

4.1.38 li rd, immediate

4.1.39 mv rd, rs1

4.1.40 not rd, rs1

4.1.41 sext.w rd, rs1

4.1.42 seqz rd, rs1

4.1.43 fmv.s rd, rs1

4.1.44 fmv.d rd, rs1

4.1.45 fneg.d rd, rs1

4.1.46 fneg.s rd, rs1

4.1.47 fabs.d rd, rs1

4.1.48 fabs.s rd, rs1

4.1.49 bgt rs1, rs2, offset

4.1.50 bgtu rs1, rs2, offset

4.1.51 ble rs1, rs2, offset

4.1.52 bleu rs1, rs2, offset

4.1.53 call rd, symbol

5 RISCV-V Instructions

5.1 Configuration-Setting Instructions

5.1.1 vsetvli rd, rs1, vtypei

5.1.2 vsetvl rd, rs1, rs2

5.2 Vector Loads and Stores Instructions

5.2.1 Unit-stride

5.2.1.1 vlb.v vd, (rs1), vm

5.2.1.2 vlh.v vd, (rs1), vm

5.2.1.3 vlw.v vd, (rs1), vm

5.2.1.4 vlbu.v vd, (rs1), vm

5.2.1.5 vlhu.v vd, (rs1), vm

5.2.1.6 vlwu.v vd, (rs1), vm

5.2.1.7 vle.v vd, (rs1), vm

5.2.1.8 vsb.v vs3, (rs1), vm

5.2.1.9 vsh.v vs3, (rs1), vm

5.2.1.10 vsw.v vs3, (rs1), vm

5.2.1.11 vse.v vs3, (rs1), vm

5.2.2 Strided

5.2.2.1 vlsb.v vd, (rs1), rs2, vm

5.2.2.2 vlsh.v vd, (rs1), rs2, vm

5.2.2.3 vlsw.v vd, (rs1), rs2, vm

5.2.2.4 vlsbu.v vd, (rs1), rs2, vm

5.2.2.5 vlshu.v vd, (rs1), rs2, vm

5.2.2.6 vlswu.v vd, (rs1), rs2, vm

5.2.2.7 vlse.v vd, (rs1), rs2, vm

5.2.2.8 vssb.v vs3, (rs1), rs2, vm

5.2.2.9 vssh.v vs3, (rs1), rs2, vm

5.2.2.10 vssw.v vs3, (rs1), rs2, vm

5.2.2.11 vsse.v vs3, (rs1), rs2, vm

5.2.3 Indexed

5.2.3.1 vlxb.v vd, (rs1), vs2, vm

5.2.3.2 vlxh.v vd, (rs1), vs2, vm

5.2.3.3 vlxw.v vd, (rs1), vs2, vm

5.2.3.4 vlxbu.v vd, (rs1), vs2, vm

5.2.3.5 vlxhu.v vd, (rs1), vs2, vm

5.2.3.6 vlxwu.v vd, (rs1), vs2, vm

5.2.3.7 vlxe.v vd, (rs1), vs2, vm

5.2.3.8 vsxb.v vs3, (rs1), vs2, vm

5.2.3.9 vsxh.v vs3, (rs1), vs2, vm

5.2.3.10 vsxw.v vs3, (rs1), vs2, vm

5.2.3.11 vsxe.v vs3, (rs1), vs2, vm

5.3 Vector Integer Arithmetic Instructions

5.3.1 Single-width integer add and subtract

5.3.1.1 vadd.vv vd, vs2, vs1, vm

5.3.1.2 vadd.vx vd, vs2, rs1, vm

5.3.1.3 vadd.vi vd, vs2, imm, vm

5.3.1.4 vsub.vv vd, vs2, vs1, vm

5.3.1.5 vsub.vx vd, vs2, rs1, vm

5.3.1.6 vrsub.vx vd, vs2, rs1, vm

5.3.1.7 vrsub.vi vd, vs2, imm, vm

5.3.2 Bitwise logical

5.3.2.1 vand.vv vd, vs2, vs1, vm

5.3.2.2 vand.vx vd, vs2, rs1, vm

5.3.2.3 vand.vi vd, vs2, imm, vm

5.3.2.4 vor.vv vd, vs2, vs1, vm

5.3.2.5 vor.vx vd, vs2, rs1, vm

5.3.2.6 vor.vi vd, vs2, imm, vm

5.3.2.7 vxor.vv vd, vs2, vs1, vm

5.3.2.8 vxor.vx vd, vs2, rs1, vm

5.3.2.9 vxor.vi vd, vs2, imm, vm

5.3.3 Single-width bit shift

5.3.3.1 vsll.vv vd, vs2, vs1, vm

5.3.3.2 vsll.vx vd, vs2, rs1, vm

5.3.3.3 vsll.vi vd, vs2, uimm, vm

5.3.3.4 vsrl.vv vd, vs2, vs1, vm

5.3.3.5 vsrl.vx vd, vs2, rs1, vm

5.3.3.6 vsrl.vi vd, vs2, uimm, vm

5.3.3.7 vsra.vv vd, vs2, vs1, vm

5.3.3.8 vsra.vx vd, vs2, rs1, vm

5.3.3.9 vsra.vi vd, vs2, uimm, vm

5.3.4 Integer comparison

5.3.4.1 vmseq.vv vd, vs2, vs1, vm

5.3.4.2 vmseq.vx vd, vs2, rs1, vm

5.3.4.3 vmseq.vi vd, vs2, imm, vm

5.3.4.4 vmsne.vv vd, vs2, vs1, vm

5.3.4.5 vmsne.vx vd, vs2, rs1, vm

5.3.4.6 vmsne.vi vd, vs2, imm, vm

5.3.4.7 vmsltu.vv vd, vs2, vs1, vm

5.3.4.8 vmsltu.vx vd, vs2, rs1, vm

5.3.4.9 vmslt.vv vd, vs2, vs1, vm

5.3.4.10 vmslt.vx vd, vs2, rs1, vm

5.3.4.11 vmsleu.vv vd, vs2, vs1, vm

5.3.4.12 vmsleu.vx vd, vs2, rs1, vm

5.3.4.13 vmsleu.vi vd, vs2, imm, vm

5.3.4.14 vmsle.vv vd, vs2, vs1, vm

5.3.4.15 vmsle.vx vd, vs2, rs1, vm

5.3.4.16 vmsle.vi vd, vs2, imm, vm

5.3.4.17 vmsgtu.vx vd, vs2, rs1, vm

5.3.4.18 vmsgtu.vi vd, vs2, imm, vm

5.3.4.19 vmsgt.vx vd, vs2, rs1, vm

5.3.4.20 vmsgt.vi vd, vs2, imm, vm

5.3.5 Integer min/max

5.3.5.1 vminu.vv vd, vs2, vs1, vm

5.3.5.2 vminu.vx vd, vs2, rs1, vm

5.3.5.3 vmin.vv vd, vs2, vs1, vm

5.3.5.4 vmin.vx vd, vs2, rs1, vm

5.3.5.5 vmaxu.vv vd, vs2, vs1, vm

5.3.5.6 vmaxu.vx vd, vs2, rs1, vm

5.3.5.7 vmax.vv vd, vs2, vs1, vm

5.3.5.8 vmax.vx vd, vs2, rs1, vm

5.3.6 Single-width integer multiply

5.3.6.1 vmul.vv vd, vs2, vs1, vm

5.3.6.2 vmul.vx vd, vs2, rs1, vm

5.3.6.3 vmulh.vv vd, vs2, vs1, vm

5.3.6.4 vmulh.vx vd, vs2, rs1, vm

5.3.6.5 vmulhu.vv vd, vs2, vs1, vm

5.3.6.6 vmulhu.vx vd, vs2, rs1, vm

5.3.6.7 vmulhsu.vv vd, vs2, vs1, vm

5.3.6.8 vmulhsu.vx vd, vs2, rs1, vm

5.3.7 Single-width integer multiply-add

5.3.7.1 vmacc.vv vd, vs1, vs2, vm

5.3.7.2 vmacc.vx vd, rs1, vs2, vm

5.3.7.3 vnmsac.vv vd, vs1, vs2, vm

5.3.7.4 vnmsac.vx vd, rs1, vs2, vm

5.3.7.5 vmadd.vv vd, vs1, vs2, vm

5.3.7.6 vmadd.vx vd, rs1, vs2, vm

5.3.7.7 vnmsub.vv vd, vs1, vs2, vm

5.3.7.8 vnmsub.vx vd, rs1, vs2, vm