时序余量(Negative Slack) 和 理论最大频率(Fmax)

https://www.cnblogs.com/lilto/p/9581143.html

建立时间就是在clk上升沿前必须保持稳定的时间,保持时间就是clk上升沿过后必须保持稳定的时间,这是触发器器件能稳定锁存的条件

所以,不考虑时钟偏移时,即认为前后两级寄存器的clk是完全一样的,

器件延迟 + 线路延迟 + 建立时间 + 建立时序余量 = 一个周期

器件延迟 + 线路延迟 = 保持时间 + 保持时序余量

http://blog.sina.com.cn/s/blog_677db1cb0100phtb.html

https://www.cnblogs.com/winkle/p/3151422.html

https://wenku.baidu.com/view/fffc9adb5022aaea998f0f56.html

一、 建立时间(Setup Time)检查:

遵循的原则是信号从Launch edge开始计时,经过一系列的时序路径,到达后级寄存器的数据输入Pin的速度不能太慢,时间不能太长,否则会侵占后级寄存器数据输入Pin相对于Latch edge的建立时间。刚好满足后级寄存器建立时间的数据到达时间是Data Required Time(相对于Latch edge计算),实际的数据到达时间是Data Arrival Time(相对于Launch edge计算)。显然,在建立时间检查中,Data Arrival Time要小于Data Required Time,否则就会造成建立时间违规。也就是说,Data Required Time是Data Arrival Time的最大值。二者之差就是建立时间的时序余量。

图1

二、 保持时间(Hold Time)检查:

遵循的原则是信号从Launch edge开始计时,经过一系列的时序路径,到达后级寄存器的数据输入Pin的速度不能太快,时间不能太短,否则会侵占后级寄存器数据输入Pin相对于上一个Latch edge的保持时间。刚好满足后级寄存器保持时间的数据到达时间是Data Required Time(相对于Latch edge计算),实际的数据到达时间是Data Arrival Time(相对于Launch edge计算)。显然,在保持时间检查中,Data Arrival Time要大于Data Required Time,否则就会造成保持时间违规。也就是说,Data Required Time是Data Arrival Time的最小值。二者之差就是保持时间的时序余量。

相对于建立时间检查,保持时间检查稍微难懂一些。二者都是同步逻辑设计中对同一个规则的不同解释:当前时钟沿发出的数据要在下一个时钟沿被正确捕获,不能晚,也不能早。晚了,会造成下一个时钟沿的建立时间违规,当前时钟沿发送的数据不能被下一个时钟沿捕获;早了,会造成上一个时钟沿发送的数据保持时间违规,上一个时钟沿发送的数据不能被当前时钟沿正确捕获。

二者在计算公式上的区别在于Slack计算公式中减数与被减数关系

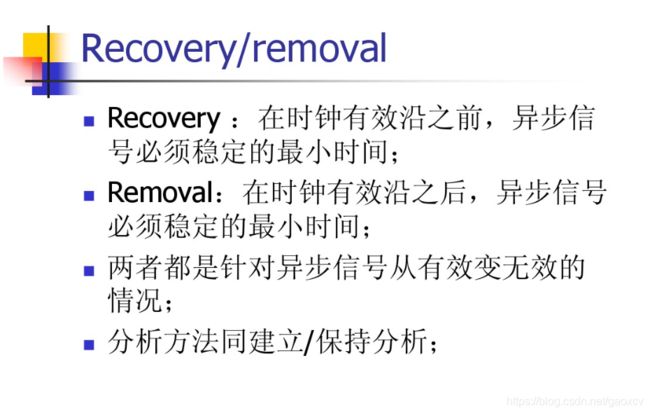

三, recovery/remove time

https://blog.csdn.net/celery1124/article/details/42773355

report timing constraints,这个就是最后时序分析的报告,这里面主要由三项,首先intra-clock paths是单时钟约束,其次inter-clock paths,这个是同步时钟的跨时钟路径,最后就是other path group,这里面的async_default就是异步时钟的跨时钟路径。

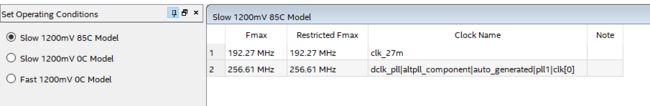

理论最大频率(Fmax)

Fmax = 1 / (set_up_time + clock_delay0 - clock_delay1 - clock_passimism - (-uTh) )

图一中

Fmax = 1 / (5.13 + 2.966 - 2.846 - 0.028 - ( +0.021) )ns = 192.270717 M

与显示值相同

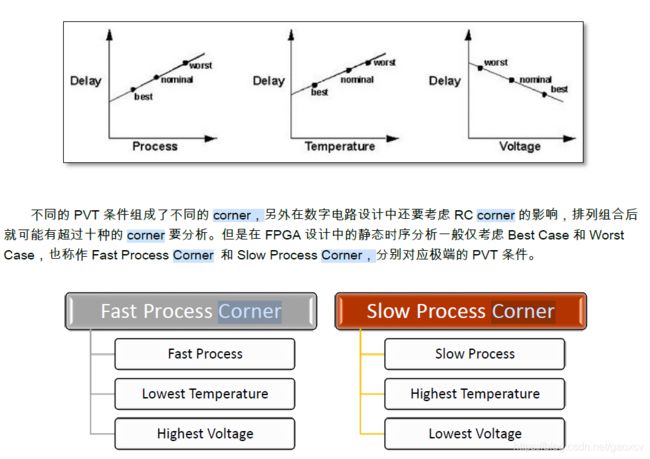

Operating Conditions

xilinx vivado 中有一个 与器件相关的参数 worst pulse width slack(wpws),

参考https://blog.csdn.net/weixin_45825101/article/details/117865471?utm_medium=distribute.pc_relevant.none-task-blog-2%7Edefault%7EBlogCommendFromBaidu%7Edefault-5.control&depth_1-utm_source=distribute.pc_relevant.none-task-blog-2%7Edefault%7EBlogCommendFromBaidu%7Edefault-5.control

https://blog.csdn.net/weixin_45825101/article/details/117865871