【FPGA IP系列】FIFO的通俗理解

FPGA厂商提供了丰富的IP核,基础性IP核都是可以直接免费调用的,比如FIFO、RAM等等。

本文主要介绍FIFO的一些基础知识,帮助大家能够理解FIFO的基础概念。

一、FIFO介绍

FIFO全称是First In First Out,即先进先出。

FIFO是一个数据缓存队列,主要特点就是数据顺序写入,再按照同样的顺序输出数据,即先进去的数据先被取出来。

1、FIFO的通俗理解

FIFO可以类比一个水池。

当写通道打开时,就相当于往水池里加水;而当读通道打开时,就相当于从水池中放水。

如果持续不断地加水和放水,如果加水速度超过了放水速度,那么水池就会满了,这时FIFO就会发生溢出,水会溢出水池。

相反,如果放水速度快于加水速度,那么水池就会变空,FIFO就会出现空的情况。

2、FIFO的分类

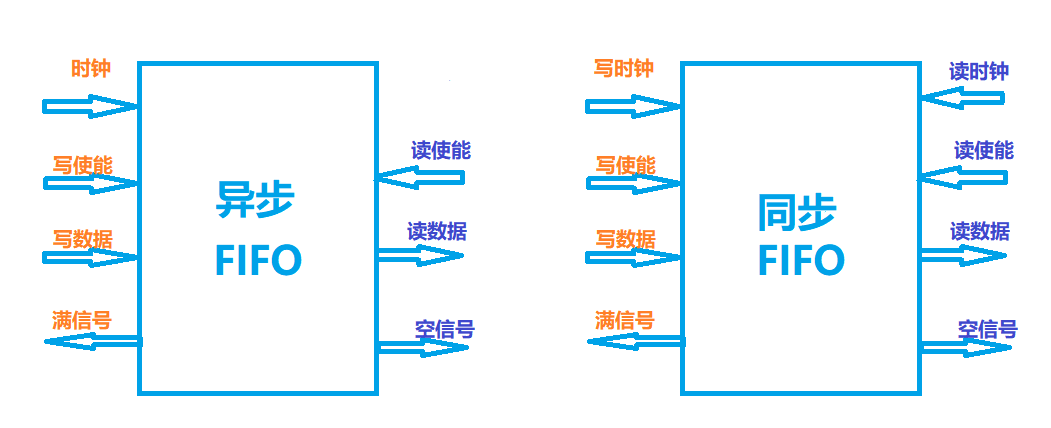

根据FIFO输入时钟的区别,可以分为同步FIFO和异步FIFO。

同步 FIFO 只有一个独立的时钟端口 clock,所有的输入输出信号都同步于 clock 信号。

异步FIFO有两个时钟,写端口和读端口分别有独立的时钟,所有写相关的信号都是属于写时钟,所有与读相关的信号都属于读时钟。

2、FIFO IP

FIFO一般不需要自己去写代码实现,FPGA官方软件都提供了FIFO IP,直接使用即可。

FPGA IP特性:

-

配置选项和控制手段广泛:提供了丰富的配置选项和控制手段,可以根据用户的需求进行灵活配置。

-

灵活的接口和支持多种数据宽度:接口设计灵活,同时支持多种不同数据宽度的操作。

-

支持多种读写模式:支持单写单读、单写多读、多写单读、多写多读等读写模式,可以适应不同的应用场景。

-

多种存储方式:支持异步、同步等不同的存储方式,可以根据需求选择合适的存储方式。

-

可配置的参数:可以配置深度、宽度、读写数据宽度等参数,使得用户可以按需定制FIFO的特性。

二、FIFO的应用

FIFO的应用非常广泛,其中同步fifo主要用于处理数据缓存,异步fifo主要用于处理跨时钟数据传输处理。

常用的应用场景如下:

接口数据/消息缓冲:FIFO可以用于缓存数据或消息,以应对数据流量突发情况,同时降低或消除背压的频率,减小上级模块的复杂度。

接口协议隔离:在模块与复杂的协议进行对接时,FIFO可以作为隔离后的用户接口,降低模块接口协议设计复杂度,并实现协议接口的IP化,提高系统的复用性。

跨时钟域处理:FIFO可以用于处理异步时钟域的数据、消息和总线。通过FIFO,可以实现简单、快速、安全的跨时钟域处理。

数据位宽转换:FIFO可以用于实现数据的位宽转换,例如从512位转换为256位。

三、FIFO的重要概念

1、主要端口

读写时钟:同步FIFO是指读时钟和写时钟为同一个时钟。异步FIFO读写时钟是独立的两个时钟。

读写使能:读写控制的使能

满信号:FIFO里面的缓存数据数量达到了最大深度值

空信号:FIFO里面的缓存全部被读空

深度:FIFO所能容纳的最大数据数量

2、FIFO的存储结构

FIFO通常采用循环存储结构,即存储空间是一个环形的缓冲区。

数据写入时,从第一个写入地址开始,依次向后写入;数据读取时,从第一个读取地址开始,依次向后读取。

当写入数据量达到FIFO的深度时,将不能再写入数据,此时需要停止写入操作,等待读取操作将数据读出,否则将发生溢出。

同样,当读取数据量达到FIFO的深度时,将不能再读取数据,此时需要停止读取操作,等待写入操作将数据写入。

3、FIFO的空满状态

FIFO具有空标志和满标志,用于指示FIFO的存储状态。

当FIFO空时,写入操作将停止,直到FIFO非空;当FIFO满时,读取操作将停止,直到FIFO非满。

空满状态的判断通常采用比较读写指针的位置关系,例如当写入指针等于读取指针时,FIFO为空;当写入指针比读取指针多一位(达到FIFO的深度)时,FIFO为满。

4、FIFO的读写操作

FIFO的读写操作遵循先进先出的原则。

写入数据时,根据写地址将数据写入FIFO的空闲位置;读取数据时,根据读地址从FIFO的存储位置读取数据。

在连续的读写操作中,读写指针会自动递增,以便在下次读写时正确指向FIFO的下一个位置。

5、FIFO的同步处理

由于FIFO通常涉及不同时钟域之间的数据传输,因此需要进行同步处理。

在异步FIFO中,写入时钟和读取时钟是不同的,需要使用握手协议进行同步。

在同步FIFO中,读写时钟是同一个时钟,但仍然需要进行时序分析,以保证数据的稳定性和可靠性

本文将不断定期更新中,码字不易,点⭐️赞,收⭐️藏一下,不走丢哦

本文由FPGA狂飙原创,有任何问题,都可以在评论区和我交流哦

您的支持是我持续创作的最大动力!如果本文对您有帮助,请给一个鼓励,谢谢。