ARM汇编指令3 - CP15协处理器介绍和操作方法

一. ARM CP15协处理器寄存器简介

CP15协处理器寄存器是ARM处理器里面的一些有特殊功能的寄存器,CP15协处理器一般包括C0 - C15寄存器,它们分别控制高速缓存cache,MMU,TLB等功能,下面分别介绍

二. CP15寄存器访问

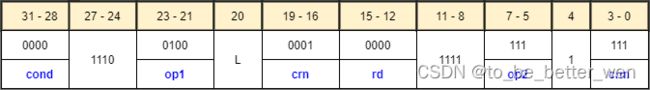

1. CP15协议处理器指令的编码格式

op1 : 协处理器行为操作码,对于CP15,op1必须为0b000(二进制0),否则结果未知。

rd :不能是r15/pc寄存器,否则结果未知。

crn :作为目标寄存器的协处理器寄存器,编号为C0 - C15。

crm :附加的目标寄存器或源操作数寄存器,如果不需要设置附加信息,将crm设置为C0,否则结果未知。

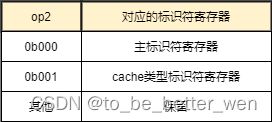

op2 :提供附加信息比如寄存器版本号或者访问类型。用于区分同一编号的不同物理寄存器,可以省略op2或将其设置为0,否则结果未知。

2. 汇编指令语法

mcr :将ARM处理器的寄存器中的数据写到CP15中的寄存器中。

语法:

mcr{

mrc :将CP15中的寄存器中的数据读到ARM处理器的寄存器中。

语法:

mcr{

三. CP15寄存器介绍

1. C0 - ID编码和cache类型(只读)

访问主标识符寄存器:

指令格式如下:

mrc p15, 0, r0, c0, c0, 0 ; 将主标识符寄存器C0的值读到r0中。

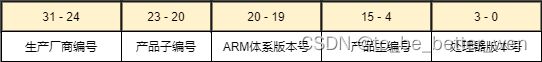

不同的处理器的主标识符寄存器的编码格式说明如下:

ARM7之后处理器的主标识符编码格式:

[ 3 - 0 ] :生产商定义的处理器版本号

[ 15 - 4 ] :生产商定义的产品主编号

[ 19 - 16 ] : 0x1 - ARMv4,0x2 - ARMv4T,0x3 - ARMv5, 0x4 - ARMv5T,0x5 - ARMv5TE

[ 23 - 20 ] : 生产产商定义的产品子编号

[ 31 - 24 ] :生产产商编号。0x41 - ARM公司,0x44 - Digital Equipment公司, 0x69 - intel公司

ARM7和之前的省略。

cache类型标识符寄存器:

指令格式如下:

mrc p15, 0, r0, c0, c0, 1 ; 将cache类型标识符寄存器C0的值读到r0中。

cache类型标识符寄存器的编码格式:

[ 28 - 25 ] :字段说明如下表所示:

[ 24 ] :定义系统中的数据cache和指令cache是统一或者分开的。0 - 系统的指令cache和数据cache是统一的,1 - 系统的指令cache和数据cache是分开的。

[ 23 - 12 ] :定义数据cache的相关属性,如果位24为0,本字段定义整个cache的属性

[ 11 - 0 ] : 定义指令cache的相关属性,如果位24为0,本字段定义整个cache属性

数据cache和指令cache的编码格式如下:

2. C1 - 控制位

指令格式:

mrc p15, 0, r0, c1, c0{, 0} ; 将CP15的寄存器C1的值读到r0中

mcr p15, 0, r0, c1, c0{, 0} ; 将r0的值写到CP15的寄存器C1中

CP15寄存器C1的编码格式及其含义:

M :0 - 禁止MMU或者PU,1 - 使能MMU或者PU

A :0 - 禁止地址对齐检查,1 - 使能地址对齐检查

C :0 - 禁止数据/指令cache,1 - 使能数据/指令cache

W :0 - 禁止写缓冲,1 - 使能写缓冲

P :0 - 异常中断处理程序进去32位地址模式,1 - 异常中断进入26位地址模式

D :0 - 禁止26位地址异常检查,1 - 使能26位地址异常检查

L :0 - 选择早期终止模型,1 - 选择后期终止模型

B :0 - 小端模式,1 - 大端模式

S : 在基于MMU的存储系统中,本位用于系统保护

R :在基于MMU的存储系统中,本位用作ROM保护

F :0 - 由生产产商确定

Z : 0 - 禁止跳转预测功能,1 - 使能跳转预测功能

I :0 - 禁止指令cache,1 - 使能指令cache

V :0 - 选择低端异常中断向量0x0 - 0x1c,1 - 选择高端异常中断向量0xffff0000 - 0xffff001c

RR :0 - 选择常规的cache淘汰算法,如随机淘汰,1 - 预测性淘汰算法,如round-robin淘汰算法

L4 :0 - 保持ARMv5以上版本的正常功能,1 - 将ARMv5以上版本与以前版本处理器兼容

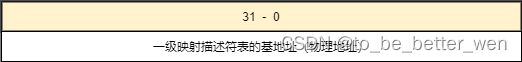

3. C2 - 地址转换表基地址

C2保存的是页表的基地址,即一级映射描述符表的基地址

4. C3 - 域访问控制位

C3定义ARM处理器的16个域的访问权限

5. C5 - 内存失效状态

6. C6 - 内存失效地址

7. C7 - 高速缓存与写缓存控制

8. C8 - TLB控制

9. C9 - 高速缓存锁定

10. C10 - TLB锁定

13. C13 - 进程标识符

14. C15 - 因不同设计而异

四. 总结

学习CP15协处理器寄存器对于深入学习ARM的一些机制非常重要,为分析Linux内核启动时运行的汇编代码非常有帮助,后续的CP15寄存器用到时再来补充。