【AMBA】AHB-Lite总线协议

文章目录

- 1. 基本结构

-

- (1) Master

- (2) slave

- (3) Address decoding

- (4) slave-to-master multiplexor

- 2. 信号时序

-

- (1) 基本时序

- (2) wait state

- 3. 基本信号

-

- (1) Transfer types

-

- 信号时序

- (2) Transfer size

- (3) Burst operation

-

- 时序信号

-

- (1) Four-beat wrapping burst,WRAP4

- (2) Four-beat incrementing burst,INCR4

- (3) Eight-beat wrapping burst,WRAP8

- (4) Eight-beat incrementing burst,INCR8

- (4) Slave Response Signaling

-

- Transfer done

- Transfer pending

- Transfer Error

- (5) Waited transfer

-

- Transfer type changes during wait states

-

- IDLE transfer

- BUSY transfer,fixed length burst

- BUSY transfer,undefined length burst

- Address changes during wait state

- (5) Protection control

- 4.参考文献

1. 基本结构

AHB-Lite的主要组成部分为:

(1)Master

(2)Slave

(3)Address Decoder

(4)slave-to-master multiplexor

(1) Master

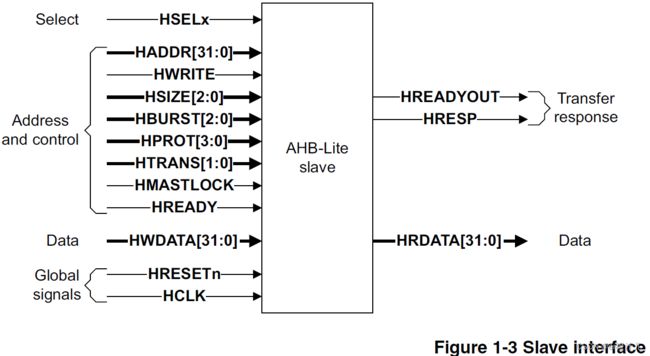

(2) slave

(3) Address decoding

(4) slave-to-master multiplexor

2. 信号时序

AHB-Lite的一次传输,信号时序分为两步:

(1)Address Phase:Master发送地址和控制信号

(2)Data Phase:Master发送写数据/Slave发送读数据

其中,Address Phase不可主动被扩展,通常为一个cycle(不能通过拉低hready来扩展Address Phase);Data Phase可以主动扩展(slave通过拉低hready扩展Data Phase)

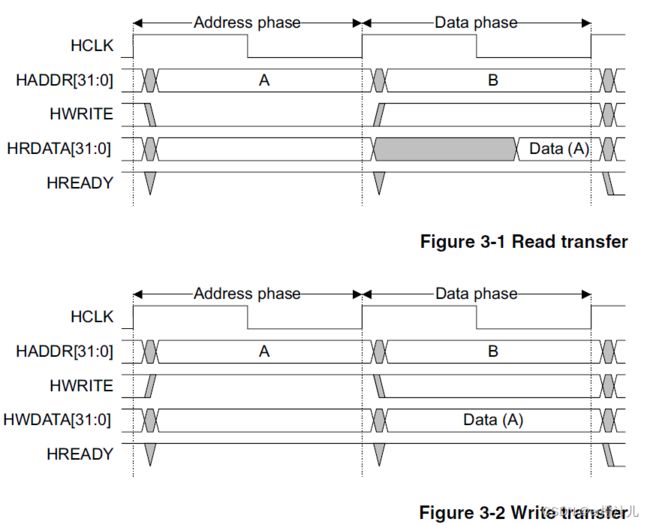

(1) 基本时序

基本操作为:

(1)在HCLK第一个上升沿,Master发送地址和控制信号

(2)Slave在第二个时钟上升沿采样地址和控制信号

(3)Slave采样了地址和控制信号后,驱动相应的HREADY电平。在第三个时钟周期Master采样相应的HREADY信号

读时序:

(1)在第一个时钟上升沿,Master发送地址和控制信号,HWRITE为低

(2)在第二个时钟上升沿,Master采样HREADY为高,进入Data Phase阶段

(3)在第三个时钟上升沿,Master采样HREADY为高,读出数据HRDATA,传输完成

写时序:

(1)在第一个时钟上升沿,Master发送地址和控制信号,HWRITE为高

(2)在第二个时钟上升沿,Master采样HREADY为高,进入Data Phase阶段,Master发送写数据HWDATA

(3)在第三个时钟上升沿,Master采样HREADY为高,传输完成

(2) wait state

读时序:

(1)在第一个时钟上升沿,Master发送地址和控制信号,HWRITE为低

(2)在第二个时钟上升沿,Master采样HREADY为高,进入Data Phase阶段,slave将HREADY拉低

(3)在第三个时钟上升沿,Master采样HREADY为低,扩展Data Phase

(4)在第四个时钟上升沿,Master采样HREADY为低,扩展Data Phase

(5)在第五个时钟上升沿,Master采样HREADY为高,读出数据HRDATA,传输完成

写时序:

(1)在第一个时钟上升沿,Master发送地址和控制信号,HWRITE为高

(2)在第二个时钟上升沿,Master采样HREADY为高,进入Data Phase阶段并发送写数据HWDATA

(3)在第三个时钟上升沿,Master采样HREADY为低,扩展Data Phase

(4)在第四个时钟上升沿,Master采样HREADY为高,传输完成

备注:

(1)此处Address A是wait state

(2)写操作—在扩展周期保持数据不变;读操作—在扩展周期不提供有效数据,直到传输快结束时才给出有效数据

3. 基本信号

| 信号 | 含义 | 所属组 |

|---|---|---|

| HCLK | 时钟信号,所有输入信号都在hclk上升沿进行 | 全局信号 |

| HRESETn | 复位信号,低电平有效 注:复位master时,需要保证此时HTRANS=idle 复位slave时需要保证HREADYOUT=high |

全局信号 |

| HADDR[31:0 | 32bit地址总线 | master output |

| HBURST[2:0] | 该信号表明传输的burst类型 | master output |

| HMASTLOCK | 当为高时,该信号表明当前传输为锁定序列的一部分 | master output |

| HPROT[3:0] | 该信号表明当前传输的privileged mode access、user mode access、opcode fetch、data access | master output |

| HSIZE[2:0] | 表明传输的大小,通常为byte、halfword、word | master output |

| HTRANS[1:0] | 传输类型,分为:IDLE/BUSY/NONSEQ/SEQ | master output |

| HWDATA[31:0] | master给slave的写数据 | master output |

| HWRITE | 指明传输方向。当hwrite为高时,表示写;当hwrite为低时,表示读 | master output |

| HRDATA[31:0] | slave返回master的读数据 | slave output |

| HREADYOUT | 当该信号为高时,表示该次传输完成 | slave output |

| HRESP | 该信号为高时,表示此次传输为OKAY; 当该信号为低时,表示此次传输为ERROR |

slave output |

| HSELx | slave的片选信号 | slave input |

| HREADY | 当该信号为高时,表示之前的传输已经完成 | master input & slave input |

(1) Transfer types

| HTRANS[1:0] | 传输类型 | 描述 |

|---|---|---|

| 2’b00 | IDLE | IDLE态表示不需要数据传输。当Master不想进行数据传输时,可以发送该传输状态。Slave忽略IDLE传输态,返回一个零延时的okay hresp |

| 2’b01 | BUSY | BUSY态使得Master在burst传输中间插入idle(即burst中间暂停传输) 。该传输态表明Master正在进行burst操作,但是下一次操作还未开始。当Master使用BUSY传输态时,地址和控制信号反应和下一次burst传输信息保持一致。Slave忽略BUSY态,返回一个零延时的okay hresp |

| 2’b10 | NONSEQ | 该传输态表示单次传输或者是burst传输的起始。地址和控制信号与之前的传输无关 |

| 2’b11 | SEQ | 该传输态表示burst传输。地址和控制信号与之前的传输相关,地址依次递增(hsize定义的递增大小) 注:地址的递增分为incr和wrap,见后面 |

信号时序

基本操作:

(1)T0-T1:NONSEQ传输态开始一次读取操作,为burst操作的第一拍

(2)T1-T2:Master插入BUSY态,延迟burst操作的第二拍,同时Slave提供第一拍的读数据

(3)T2-T3:Master开始burst传输的第二拍,传输态为SEQ,同时master忽略hrdata(BUSY态读回的数据,Master忽略掉)

(4)T3-T4:Master继续传输第三拍,Slave提供第二拍的hrdata

(5)T4-T5:Master传输第四拍,Slave将hready拉低,插入wait state

(6)T5-T6:Slave提供第三拍hrdata

(7)T6-T7:Slave提供第四拍hrdata

(2) Transfer size

| HSIZE | size(bits) | 描述 |

|---|---|---|

| 3’b000 | 8 | Byte |

| 3’b001 | 16 | Halfword |

| 3’b010 | 32 | Word |

| 3’b011 | 64 | Doubleword |

| 3’b100 | 128 | 4-word line |

| 3’b101 | 256 | 8-word line |

| 3’b110 | 512 | - |

| 3’b111 | 1024 | - |

注:(1)HSIZE定义的传输大小必须要小于等于数据宽度

(2)联合HSZIE和HBURST,可以定义wrapping bursts的地址边界

(3)HSIZE和HADDR有完全相同的时序,在burst transfer中保持常数

(3) Burst operation

| HBURST[2:0] | Type | Description |

|---|---|---|

| 3’b000 | SINGLE | Single burst |

| 3’b001 | INCR | Incrementing burst of undefined length |

| 3’b010 | WRAP4 | 4-beat wrapping burst |

| 3’b011 | INCR4 | 4-beat incrementing burst |

| 3’b100 | WRAP8 | 8-beat wrapping burst |

| 3’b101 | INCR8 | 8-beat incrementing burst |

| 3’b110 | WRAP16 | 16-beat wrapping burst |

| 3’b111 | INCR16 | 16-beat wrapping burst |

注:(1)Master发送的burst操作最大不能超过1KB

(2)地址边界=the number of beats in a burst * the size of the transfer,其中beats的大小由HBURST控制,传输带下由HSIZE控制

时序信号

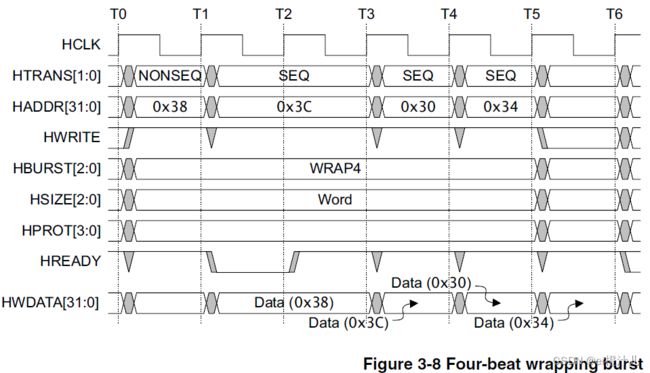

(1) Four-beat wrapping burst,WRAP4

HBURST=WRAP4:burst four-beat

HSIZE=Word:地址递增值为0x4

地址边界:4-beat *word=16byte

T0-T1:NONSEQ传输态开始一次写传输,地址为0x38;为burst传输的第一beat

T1-T2:SEQ传输态继续burst传输的第二beat,地址递增为0x3C;同时Slave拉低0x38的HREADY,扩展0x38的Data Phase

T2-T3:0x38的传输完毕

T3-T4:SEQ传输态继续burst传输的第三beat,地址递增为0x30(WARP4对齐16byte边界);同时0x3C完成传输

T4-T5:SEQ传输态继续burst传输的第四beat,地址递增为0x34;同时0x30完成传输

T5-T6:0x34传输完毕

(2) Four-beat incrementing burst,INCR4

HBURST=INCR4:burst four-beat

HSIZE=Word:地址递增值为0x4

因为是incrementing burst,因此到达16byte地址边界后继续增加

T0-T1:NONSEQ传输态开始一次读传输,地址为0x38;为burst传输的第一beat

T1-T2:SEQ传输态继续burst传输的第二beat,地址递增为0x3C;同时Slave拉低0x38的HREADY,扩展0x38的Data Phase

T2-T3:HREADY为高,Slave给出0x38的读数据

T3-T4:SEQ传输态继续burst传输的第三beat,地址递增为0x40(INCR4,地址递增跨过16byte边界);同时Slave给出0x3C的读数据

T4-T5:SEQ传输态继续burst传输的第四beat,地址递增为0x44;同时Slave给出0x40的读数据

T5-T6:Slave给出0x44的读数据

(3) Eight-beat wrapping burst,WRAP8

HBURST=WRAP8:burst eight-beat

HSIZE=Word:地址递增值为0x4

地址边界:8-beat *word=32byte

T0-T1:NONSEQ传输态开始一次读传输,地址为0x34;为burst传输的第一beat

T1-T2:SEQ传输态继续burst传输的第二beat,地址递增为0x38;同时Slave给出0x34的读数据

T2-T3:SEQ传输态继续burst传输的第三beat,地址递增为0x3C;同时Slave给出0x38的读数据

T3-T4:SEQ传输态继续burst传输的第四beat,地址递增为0x20(WARP8对齐32byte边界);同时Slave给出0x3C的读数据

T4-T5:SEQ传输态继续burst传输的第五beat,地址递增为0x24;同时Slave给出0x20的读数据

T5-T6:SEQ传输态继续burst传输的第六beat,地址递增为0x28;同时Slave给出0x24的读数据

T6-T7:SEQ传输态继续burst传输的第七beat,地址递增为0x2C;同时Slave给出0x28的读数据

T7-T8:SEQ传输态继续burst传输的第八beat,地址递增为0x30;同时Slave给出0x2C的读数据

T8-T9:Slave给出0x30的读数据

(4) Eight-beat incrementing burst,INCR8

HBURST=INCR8:burst eight-beat

HSIZE=Halfword:地址递增值为0x2

因为是incrementing burst,因此到达16byte地址边界后,地址继续增加

T0-T1:NONSEQ传输态开始一次读传输,地址为0x34;为burst传输的第一beat

T1-T2:SEQ传输态继续burst传输的第二beat,地址递增为0x36;同时Slave给出0x34的读数据

T2-T3:SEQ传输态继续burst传输的第三beat,地址递增为0x38;同时Slave给出0x36的读数据

T3-T4:SEQ传输态继续burst传输的第四beat,地址递增为0x3A;同时Slave给出0x38的读数据

T4-T5:SEQ传输态继续burst传输的第五beat,地址递增为0x3C;同时Slave给出0x3A的读数据

T5-T6:SEQ传输态继续burst传输的第六beat,地址递增为0x3E;同时Slave给出0x3C的读数据

T6-T7:SEQ传输态继续burst传输的第七beat,地址递增为0x40(INCR8,地址递增跨过16byte边界);同时Slave给出0x3E的读数据

T7-T8:SEQ传输态继续burst传输的第八beat,地址递增为0x42;同时Slave给出0x40的读数据

T8-T9:Slave给出0x42的读数据

(4) Slave Response Signaling

Master发起一次transfer后,Slave控制该transfer如何工作。Master发起一次transfer之后,不能取消该transfer。Slave通过HRESP来反映transfer状态。

| HRESP | Response | Description |

|---|---|---|

| 0 | OKAY | 成功完成传输/扩展周期 注:HREADY表明该次传输是完成还是等待(wait state) |

| 1 | ERROR | 传输过程中发生错误 注:Error response需要两个周期,在第二个周期HREADY为高 |

Transfer Response是由HRESP和HREADY组合完成的,组合行为

也就是说,Slave反应transfer的状态有三种方式

(1)立即完成(HREADY为高,HRESP为OKAY)

(2)插入一个或者多个wait states,等待完成(HREADY为低,HRESP为OKAY)

(3)返回error

Transfer done

HREADY为高(高电平),HRESP为OKAY(低电平)

Transfer pending

HREADY为低(低电平),HRESP为OKAY(低电平)

注:推荐Slave插入的wait state不超过16

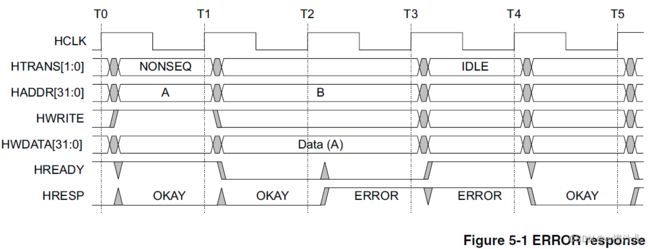

Transfer Error

OKAY response一般在一个周期给出,Error response在两个周期给出。

第一个周期:HREADY为低(低电平),HRESP为ERROR(高电平)

第二个周期:HREADY为高(高电平),HRESP为ERROR(高电平)

Error response需要两个周期的原因是因为AHB-Lite总线的二级流水特性。当Slave开始返回一个ERROR响应的时候,Master已经发送了下一次transfer的地址。因此two-cycle error response使得Master在第二周期时将HTRANS设置为IDLE,Slave对IDLE态响应OKAY。

T0-T1:HREADY为高,HRESP为OKAY,传输完成

T1-T2:HREADY为低,HRESP为OKAY,传输等待(地址A的等待)

T2-T3:HREADY为低,HRESP为ERROR,传输失败,Error response的第一个周期(地址A写失败)

T3-T4:HREADY为高,HRESP为ERROR,传输失败,Error response的第二个周期(地址A写失败)

Master将HTRANS设置为IDLE,地址B(Address Phase在T2处采样)的传输操作被取消

T4-T5:HREADY为高,HRESP为OKAY,传输完成(Slave对IDLE态不进行处理)

(5) Waited transfer

当Slave需要更多时间提供和采样数据时,使用Hready插入wait state。处于wait state状态时,master只能改变传输类型和地址。

Transfer type changes during wait states

当传输处于wait state时,Master只能在以下几种情况改变传输类型

1.IDLE transfer

2.BUSY transfer,fixed length burst

3.BUSY transfer,undefined length burst

IDLE transfer

当传输处于wait state时,Master被允许将传输类型从IDLE更改为NONSEQ。当传输类型更改为NONSEQ,除非HREADY为高且Transfer不再处于wait state状态,否则Master不能再更改传输类型。

T0-T1:Master对地址A发起一次Single burst

T1-T2:Master对地址Y插入IDLE状态,Slave插入wait state(HREADY=LOW)

此次wait state是地址A的状态

T2-T3:Master对地址Z插入IDLE状态

T3-T4:Master将传输状态更改为NONSEQ,并对地址B发起INCR4 burst操作

T4-T5:HREADY=LOW,传输处于wait state状态,Master不能更改HTRANS,将HTRANS保持为NONSEQ

T5-T6:HREADY=HIGH,Slave返回地址A的读数据DATA(A),Master开始INCR4传输的第一拍

T6-T7:HREADY=HIGH,Slave返回地址B的读数据DATA(B),Master开始INCR4传输的第二拍,将HTRANS更改为SEQ,给出地址B+4

BUSY transfer,fixed length burst

当传输处于wait state且burst长度固定时,Master被允许将传输类型从BUSY更改为SEQ。当传输类型更改为SEQ,除非HREADY为高且Transfer不再处于wait state状态,否则Master不能再更改传输类型。

注:由于BUSY态只能在两次连续的burst之间插入,因此这种情况只适用于burst长度固定的几种类型:

(1)INCR4,INCR8和INCR16

(2)WRAP4,WRAP8和WRAP16

T0-T1:Master对地址0x24发起INCR4操作

T1-T3:Master在地址0x28插入BUSY态,Slave插入wait state(HREADY=LOW)

此次wait state是地址0x24的状态

T3-T4:Master将HTRANS更改为SEQ

T4-T5:HREADY=LOW,传输处于wait state状态,Master不能更改HREANS状态,保持为SEQ

T5-T6:HREADY=HIGH,Slave返回地址0x24的读数据DATA(0x24),Master开始传输INCR4第二拍,给出地址0x28

T6-T7:HREADY=HIGH,Slave返回地址0x28的读数据DATA(0x28),Master开始传输INCR4第三拍,给出地址0x2C

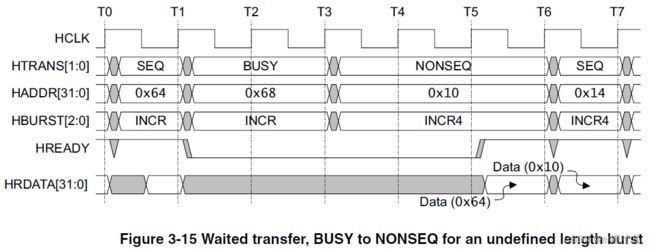

BUSY transfer,undefined length burst

当传输处于wait state且burst长度不固定(INCR)时,Master被允许将传输状态从BUSY更改为其他任何传输类型。如果更改为SEQ则该burst继续,如果更改为IDLE或NONSEQ则该burst终止。

T0-T1:Master对地址0x64发起INCR操作

T1-T3:Master对地址0x68插入BUSY态,Slave插入wait state(HREADY=LOW)

此次wait state是地址0x64的状态

T3-T4:Master将HTRANS更改为NONSEQ,同时地址更改为0x10,HBURST更改为INCR4,结束INCR burst

T4-T5:HREADY=LOW,传输处于wait state状态,Master不能更改传输类型,将HTRANS保持为NONSEQ

T5-T6:HREADY=HIGH,Slave返回地址0x64的读数据DATA(0x64),Master开始INCR4传输的第一拍,给出地址0x10

T6-T7:HREADY=HIGH,Slave返回地址0x10的读数据DATA(0x10),Master开始INCR4传输的第二拍,给出地址0x14

Address changes during wait state

当传输为wait state时,Master只能在HTRANS发生变化时改变地址。但是当HTRANS=IDLE时,地址可以任意改变。

T0-T1:Master对地址A发起一次Single burst

T1-T2:Master对地址Y插入IDLE状态,Slave插入wait state(HREADY=LOW)

此次wait state是地址A的状态

T2-T3:Master对地址Z插入IDLE状态

T3-T4:Master将传输状态更改为NONSEQ,并对地址B发起INCR4 burst操作

T4-T5:HREADY=LOW,传输处于wait state状态,Master不能更改HTRANS,将HTRANS保持为NONSEQ

T5-T6:HREADY=HIGH,Slave返回地址A的读数据DATA(A),Master开始INCR4传输的第一拍

T6-T7:HREADY=HIGH,Slave返回地址B的读数据DATA(B),Master开始INCR4传输的第二拍,将HTRANS更改为SEQ,给出地址B+4

(5) Protection control

| HPROT[3] Cacheable |

HPROT[2] Bufferable |

HPROT[1] Privileged |

HPROT[0] Dtat/Opcode |

Description |

|---|---|---|---|---|

| - | - | - | 0 | Opcode fetch |

| - | - | - | 1 | Data access |

| - | - | 0 | - | User access |

| - | - | 1 | - | Privileged access |

| - | 0 | - | - | Non-bufferable |

| - | 1 | - | - | bufferable |

| 0 | - | - | - | Non-cacheable |

| 1 | - | - | - | Cacheable |

如果主机不能提供明确的保护信息,则推荐使用:

1.Master设置HPROT=4’b0011,表示Non-cacheable,Non-bufferable,Privileged access,Data access

2.除非必须,Slave不使用HPORT

注:HPROT控制信号和address bus有相同的时序,在burst传输中要一直保持常数

4.参考文献

AMBA3 AHB-Lite