数电第七周实验:从全加器到四位串行进位加法器

Verilog:

题目:设计一个全加器,并用该全加器实现4位串行进位加法器。

(拓展:用七段数码管显示两个加数,按键显示相加的结果。)

要求:

2. 用Verilog HDL实现并在FPGA开发板上验证。3. 将Verilog代码和运行效果图上传

Logisim:

P6 Logisim组件的延迟,竞争冒险组合逻辑电路的分析,小规模组合电路设计

P7 Logisim中的震荡现象

一、全加器实现

原理还不懂的可以看看这个视频:【计算机组成原理(一)】半加器与全加器_哔哩哔哩_bilibili

代码如下:

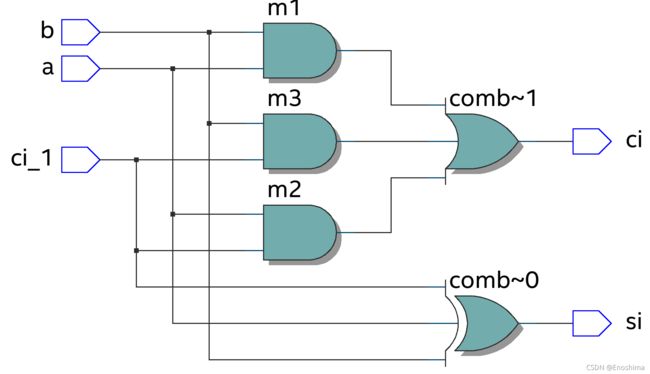

module adder(a,b,ci_1,si,ci);

input a,b,ci_1;

output si,ci;

wire s1,m1,m2;

xor(s1,a,b);//s1=a^b

xor(si,s1,ci_1);//si=s1^ci_1=a^b^ci_1

and(m1,a,b);//m1=a&b

and(m2,a,ci_1);//m2=a&ci_1

and(m3,b,ci_1);//m3=b&ci_1

or(m4,m3,m2);//m4=m3+m2

or(ci,m1,m4);//ci=m1+m4=m1+m3+m2= a&b + a&ci_1 + b&ci_1

endmodule tools->netlistviewers->rtl viewer:

接下来就是想办法把硬件和程序接上。

二、四位串行加法器

原理不懂看这个,看前六分钟就够了。【计算机组成原理(二)】串行进位加法器/行波进位加法器原理及延迟时间计算_哔哩哔哩_bilibili

因此最终是三个文件:底层的全加器adder.v,四位串行全加器my_4adder.v,主函数display.v。

(1) adder.v

module adder(a,b,ci_1,si,ci);//全加器

input a,b,ci_1;

output si,ci;

wire s1,m1,m2;

xor(s1,a,b);//s1=a^b

xor(si,s1,ci_1);//si=s1^ci_1=a^b^ci_1

and(m1,a,b);//m1=a&b

and(m2,a,ci_1);//m2=a&ci_1

and(m3,b,ci_1);//m3=b&ci_1

or(m4,m3,m2);//m4=m3+m2

or(ci,m1,m4);//ci=m1+m4=m1+m3+m2= a&b + a&ci_1 + b&ci_1

endmodule (2) my_4adder.v

module my_4adder(a,b,s,ci,cout);//四位串行加法器

input [3:0] a;

input [3:0] b;

input ci;

output [3:0] s;

output cout;

wire c1,c2,c3;

//非常粗暴的实现:四次adder运算

adder u0(.a(a[0]),.b(b[0]),.ci_1(ci),.si(s[0]),.ci(c1));

adder u1(.a(a[1]),.b(b[1]),.ci_1(c1),.si(s[1]),.ci(c2));

adder u2(.a(a[2]),.b(b[2]),.ci_1(c2),.si(s[2]),.ci(c3));

adder u3(.a(a[3]),.b(b[3]),.ci_1(c3),.si(s[3]),.ci(cout));

endmodule (3) display.v

module display(sw,key_confirm_1,key_confirm_2,led);//main

input [3:0]sw;

input key_confirm_1,key_confirm_2;

output [3:0]led;

reg [3:0]a;

reg [3:0]b;

wire ci,cout;

always@(*)begin

if (key_confirm_1==0)begin //1号确认键确认被加数

a=sw;

end

else if(key_confirm_2==0)begin //2号确认键确认加数

b=sw;

end

end

my_4adder u5(.a(a),.b(b),.s(led),.ci(ci),.cout(cout));

endmodule