Synplify使用小结

1 创建Tcl scipt文件

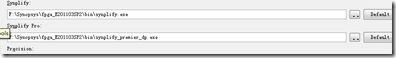

1.1建立新工程 project –new

1.2添加源文件 add_file –verilog 或 add_file –vhdl

1.3 综合控制命令设置目标器件、设计速度目标等。调用symbolic FSM complier及其它option设置。 set_option

1.4供应商提供的指令 vendor—specific

1.5添加约束文件 add_file –constraint

1.6 执行综合命令 project –run

2常用的Tcl指令

2.1工程命令

project –new 创建新工程 –save 指定工程名字 在工程运行其它指令前必须有 project -new和project –load两者之一

project –load “project_name.prj” 装载一个工程

project –log_file “new_log_filename.srr”指定一个新的log文件名代替隐含的log文件名project_name_srr。该文件包含了以下信息:简单的编译信息,技术映射信息,资源利用信息和时序报告

project –result_file “result_filename”指定一个新的综合结果文件名代替隐含的综合结果文件。

project –result_format “result_file_format”改变综合结果文件的数据格式。

project –compile 编译设计工程不进行技术映射 ,进行语法检查,可综合性检查、生成RTL级综合结果

project –run 编译并综合 project –save “project_filename.prj”保存工程文件

2.2 添加文件的命令

add_file –verilog “verilog_filename.v” 可用”*.v”代表添加所有文件

add_file –vhdl [-lib library_name] “vhdl_filename.vhd”

add_file –constraint “constraint_filename.sdc” 添加约束文件

2.3控制命令

set_option –top_module {verilog_modle | vhdl_entity|vhdl_entity.arch}指定顶层文件

set_option –write_verilog {true|false}把综合的网表存成一verilog格式的文件,以便综合后仿真调用

set_option –write_vhdl {true|false}把综合的网表存成一vhdl格式的文件,以便综合后仿真调用

set_option –write_apr_constaint {true|false} 把综合中的约束信息生成一个指导布局布线的约束文件。文件的格式与所选器件有关

set_option –frequency MHZ_frequency 指定时间约束目标

set_option –technology {vendor_technology} 指定综合选用的器件系列

set_option –part {vendor_part_name} 指定综合选用器件的器件名

set_option –package {vendor_package_name} 指定综合选用器件的封装

set_option –speedgrade {number}指定综合选用器件的速度等级

set_option –symbolic_fsm_compiler{true|false}选择是否在综合时调用针状态机优化的强有力的工具symbolic FSM compiler

set_option –default_emum_encoding {onehot|sequential |gray} 指定对设计中的状态机进行综合时选用的隐含编码方式

2.4打开文件

open_file –edit_file “filename”直接打开源文件或其它文件

open_file –rtl_view 显示综合结果的RTL级

open_file –technologty_view 打开映射后的结果