07- RTC实时时钟

RTC实时时钟

- RTC实时时钟

-

-

- RTC时钟来源:

- RTC的特征:

- 简化的RTC框图及原理简介:

- RTC由两部分组成:

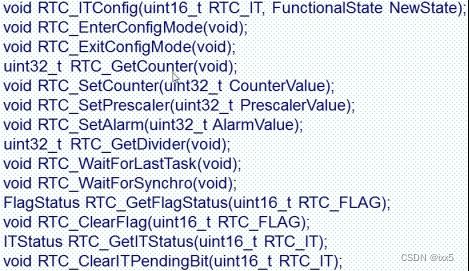

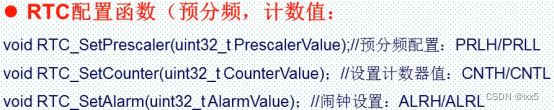

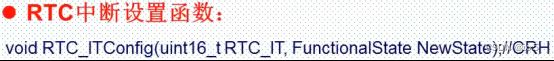

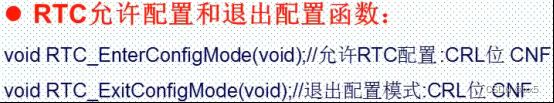

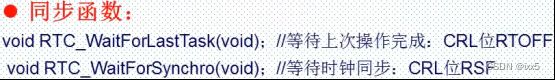

- RTC相关库函数:

- 库函数的讲解和使用:

- RTC配置步骤:

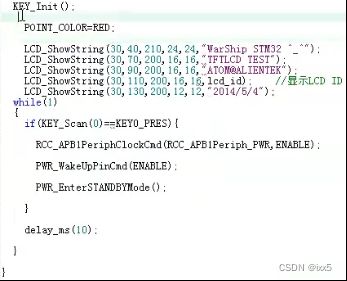

- 示例

-

RTC实时时钟

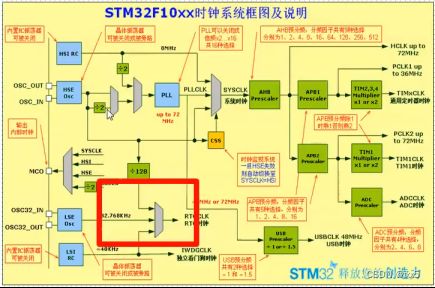

RTC时钟来源:

RTC的特征:

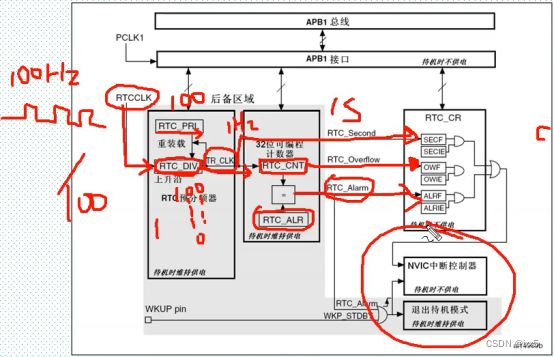

简化的RTC框图及原理简介:

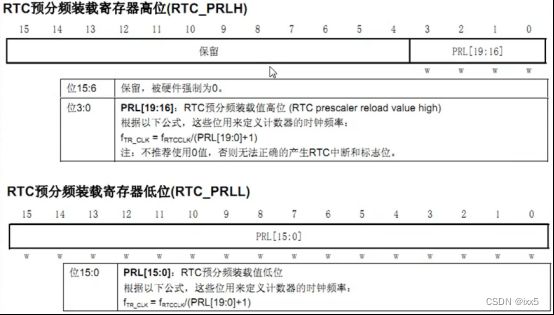

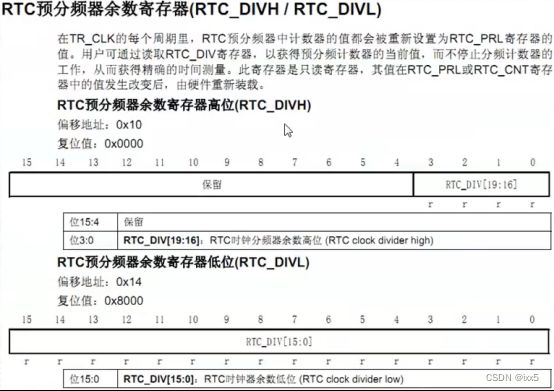

RTC_DIV根据RTC_PRL中的重装载数值开始递减计数,输入的时钟源的高低电平(或上升沿),RTC_DIV减到0时重新装载计数,从而由RTC_DIV输出产生了TR_CLK。可以通过编程产生最长为1秒的RTC时间基准TR_CLK。

从TR_CLK之后的模块可以产生3种中断:

<1>根据TR_CLK的计数产生秒中断;

<2>根据RTC_CNT对TR_CLK计数,产生溢出中断;

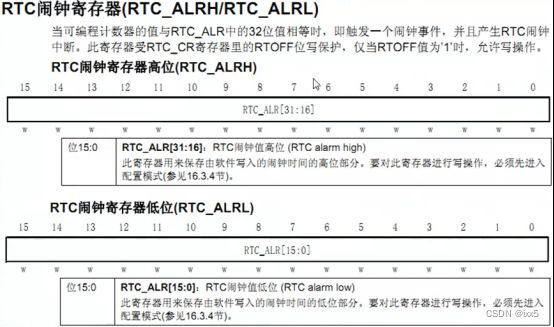

<3>当计数器RTC_CNT中的数值与RTC_ALR中数值相等时,会触发一个闹钟事件,同时产生闹钟中断。

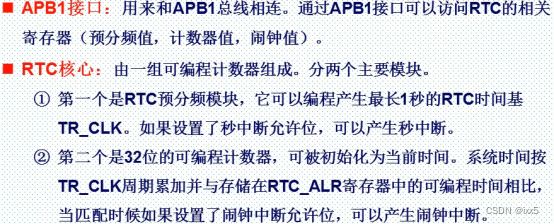

RTC由两部分组成:

BKP备份寄存器:

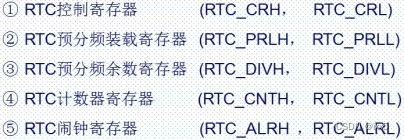

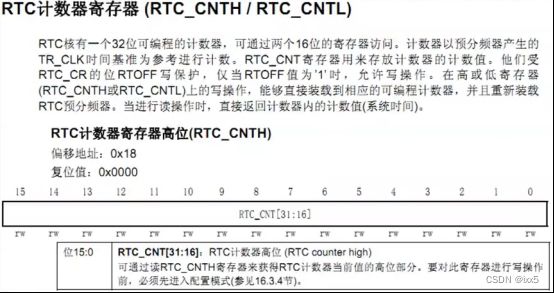

RTC相关的寄存器:

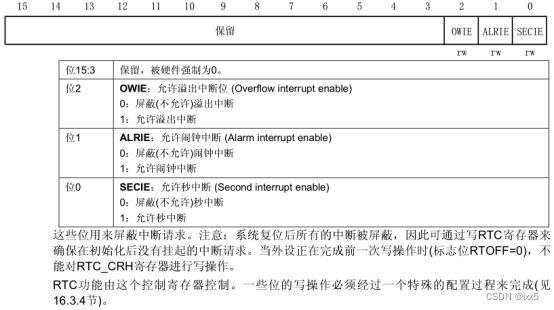

RTC_CRH:

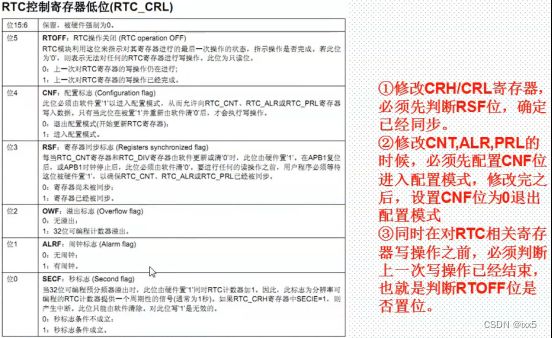

RTC_CRL:

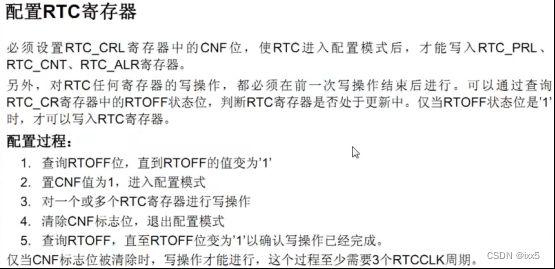

配置:

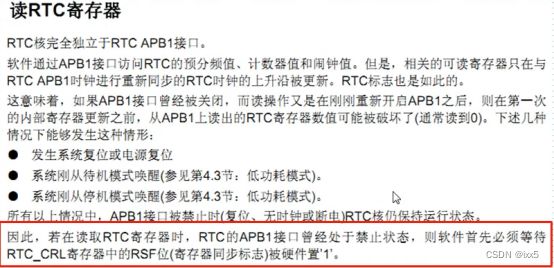

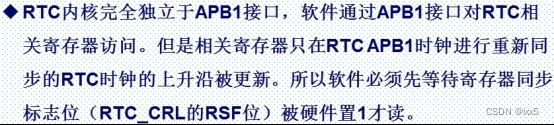

读RTC寄存器: