VCS+Verdi脚本化仿真Vivado工程流程

前言

前面的章节对VCS+Verdi与Vivado的联合仿真,从软件安装、VCS编译vivado仿真库以及直接通过Vivado界面export出VCS仿真文件夹,可直接执行仿真流程。

本文介绍使用另一种仿真的方式---Makefile脚本,对Vivado生成的GTH transceiver example进行仿真。

一、为什么要使用VCS仿真,使用Verdi看仿真波形?

1.1先了解下VCS和Verdi软件

VCS 是Synopsys公司为从事 IC 设计工作的业界人员提供的验证解决方案平台。VCS 是编译型仿真器,可编译 C、C++、Verilog、SystemVerilog 等文件,编译后生成simv可执行文件进行仿真。VCS具有高性能、大规模和高精度的特点,适用于从行为级到 Sign-Off 等各个阶段的仿真验证。

Verdi 最开始是由 novas 公司设计的,2012年由 Synopsys公司间接收购。除了源代码浏览器的标准功能(原理图、状态机图和波形比较),Verdi平台还具有自动跟踪信号活动的高级功能(基于断言的调试、功耗感知调试以及事务和消息数据的调试和分析)。Verdi平台有助于快速定位和解决设计错误,加速IC设计流程。

1.2 为什么大部分使用VCS+Verdi用于仿真原因?

因为现在大部分的同学或是打工人都会用到服务器,而在服务器中FPGA的仿真主要还是以VCS平台为主,配合使用Verdi查看仿真波形。而在linux系统中,直接使用脚本比使用界面编译更加方便快捷。

二、使用VCS仿真Vivado工程操作流程

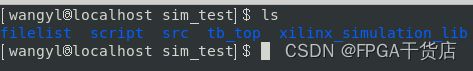

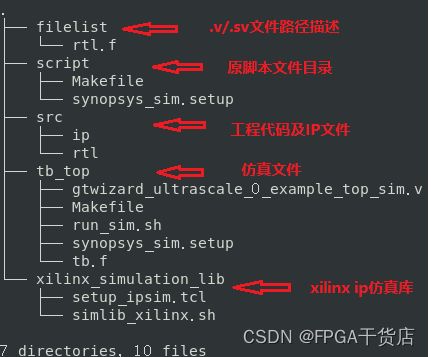

在我们设计代码时99%都会用到Xilinx提供的IP core,所以本文就以Transceiver Wizard IP的Example工程为例子讲解如何使用所提供的仿真脚本进行仿真(如果设计代码是纯逻辑编写也是适用),此处的链接是已经梳理完成的GTH transceiver example仿真脚本文件夹VCS仿真vivado脚本文件,我们看到此sim_test文件夹下有5个子目录,接下来我们根据仿真一步步的流程分别对应讲解各文件。

2.1Transceiver Example工程生成

首先我们在Vivado中例化一个Transceiver Wizard IP,按照个人需求修改设置选项后生成IP,并在此IP基础上生成Example工程。Example生成完成后需要导出VCS仿真文件,具体如何导出请参考之前的文章内容。Vivado 2021.2版本与VCS/Verdi 2018版本联合仿真

(这时候会想你都打算用另一个仿真脚本去仿真了,为啥还要从Vivado中再导出VCS仿真脚本文件???因为在仿真过程中发现好多IP文件找不到,因为这个IP并不在Example下,而是在Xilinx的安装目录下,主要是为了方便做filelist设置文件路径,否则编译一次,找一个文件,太没有效率了,后续会对这个问题说明。)

2.2Xilinx IP仿真库编译

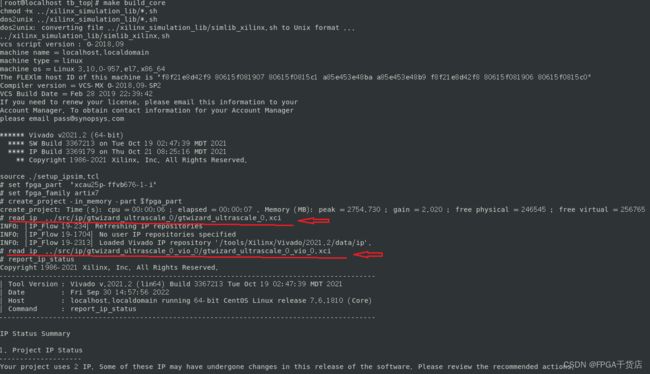

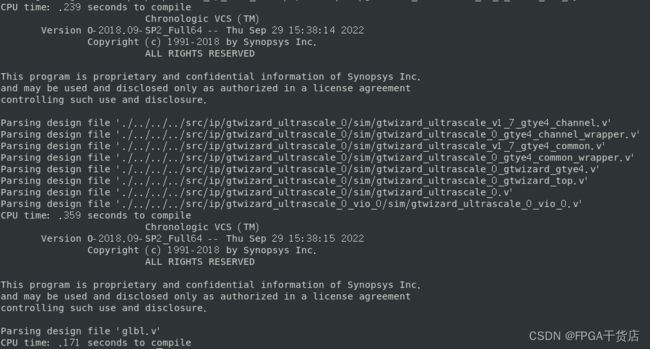

因为Transceiver Example工程中有Xilinx的IP core,我们需要将ip使用vcs进行仿真编译成可以使用的库文件,此时我们就需要使用tb_top文件夹下的Makefile这个脚本文件,此时在文件夹下执行make build_core就对工程中使用的IP进行库编译。

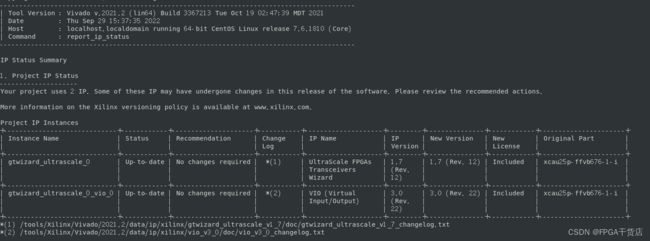

我们看到只是对使用的两个IP进行库编译,之前文章中我们是对所有的IP进行库编译,这是好处是只对使用的IP进行库编译,不仅解决编译时间也方便管理。

那么我i就看看该指令执行后做了哪些工作?使用了哪些脚本文件?

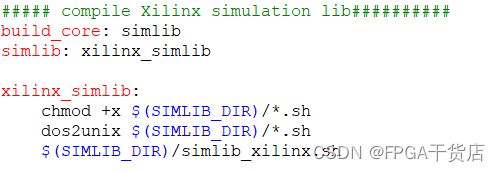

1.首先我们打开Makefile这个脚本文件,看到build_core这个变量下执行的是simlin_xilinx.sh脚本;

2.在脚本中定义了simlin_xilinx.sh脚本在xilinx_simulation_lib文件夹中,打开后如下:

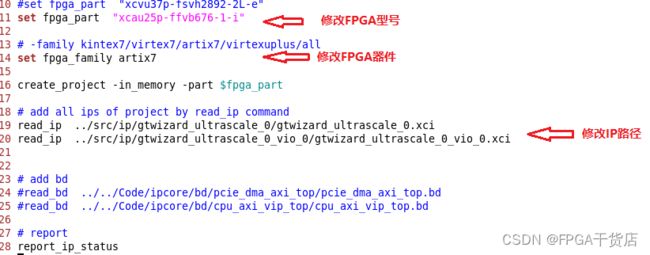

3.在simlin_xilinx.sh脚本中也看到要执行setup_ipsim.tcl脚本文件,打开后如下:

以上的修改部分都可以根据自己的工程去修改。

注意几点:

- 在这里面的IP路径是以xilinx_simulation_lib为相对路径设置;

- 脚本中这个两个IP文件是从Transceiver Example工程中的*.src文件建中拷贝出来,放在sim_top/src/ip路径下,但是只包含.xci文件,其他的仿真文件却在Transceiver Example工程中的*.gen,也需要将各自ip文件拷贝到sim_top/src/ip对应的ip文件下,否则IP编译会报没有文件编译问题。(这个问题只有在vivado自生成example中会有,如果单独建立工程例化IP,IP的文件都会在*.src文件夹下,不会分开)

2.3VCS仿真Transceiver Example

2.3.1VCS仿真流程介绍

VCS工具仿真分为compile、elaborate和simulate三个步骤

(1)compile主要是对文件的语法进行检测,然后产生中间文件(库)保存到执行的库目录下,供elaborate使用,具体来说可能会涉及3中不同类型的文件:verilog、VHDL和SystemVerilog:

针对VHDL文件命令:vhdlan [vhdlan_options] file1.vhd file2.vhd

针对Verilog文件命令:vlogan [vlogan_options] file1.v file2.v

针对SystemVerilog文件命令:vlogan -sverilog [vlogan_options] file1.sv file2.sv不仅需要对compile需要存放库的位置进行指定,而且编译的过程中verilog文件可能会涉及到xilinx的IP或者硬核,这时候需要通过synopsys_sim.setup这个文件来指定IP库的位置。

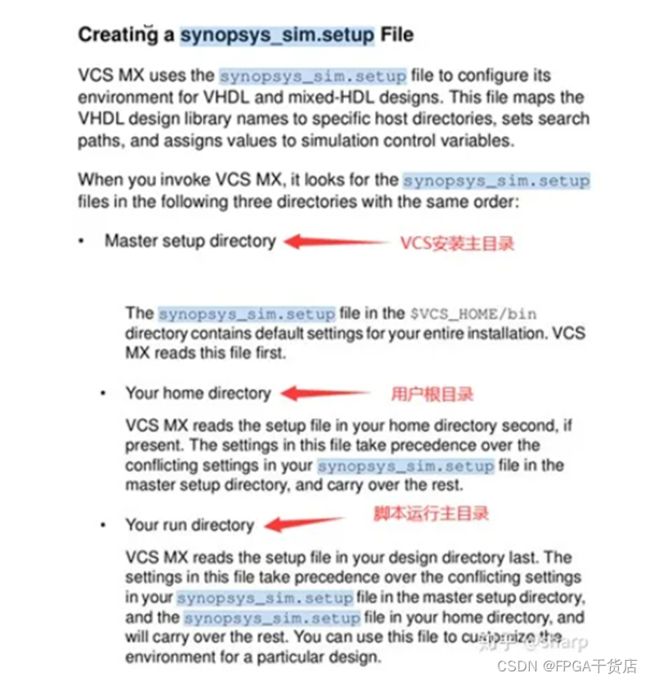

在此仿真平台中synopsys_sim.setup放在tb_top目录下,即Makefile脚本放在同目录下。这个文件是必须有的,在VCS参考手册中有说明:

打开在tb_top目录下文件synopsys_sim.setup文件可以看到只有两行:

第一行表示:在VCS compile编译文件时指定产生中间文件(库)要放在什么地方;

第二行表示:在VCS编译时使用的IP相关编译库的位置,使用OTHERS用于链接第2章节生成的synopsys_sim.setup,这样就避免需修改文件,添加此行说明进行调用就可以。

(2)elaborate主要是编译设计,在synopsys_sim.setup中定义的所有库中,找一个库(通常是DEFAULT),设置一个顶层module。然后从这个顶层module开始,把一个个instance连接起来,如果遇到无法识别的instance,就去我们别的库里找这个instance的模块定义 ,如果还是找不到的话就报错。

(3)simulate这一步就是执行上面生成的simv.o可执行文件,进行仿真。

2.3.2VCS仿真前提前准备

我们简单介绍了VCS的仿真流程,那么在进行Transceiver Example之前,需要将仿真所需的文件及脚本进行修改;

(1)src文件夹:

在该文件夹下存放仿真使用的所有代码文件.v/.sv和ip核文件,需要从Transceiver Example工程文件中imports文件夹下的所有代码拷贝到rtl目录下,从*.src和*.gen文件夹下将ip相关文件拷贝到ip目录下。

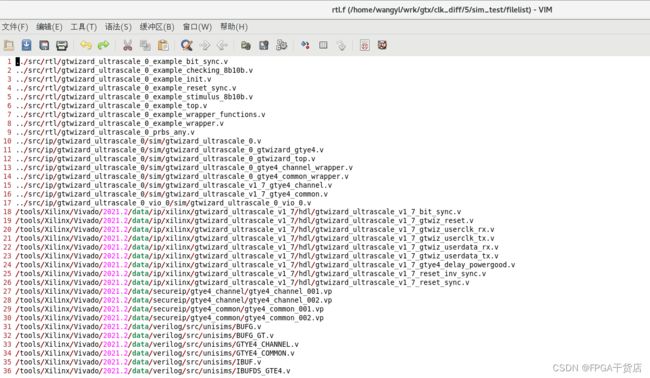

(2)filelist文件夹:

该文件夹下的rtl.f中是仿真文件的位置路径,该路径是以tb_top目录为相对路径下仿真文件的位置;(也可以包含绝对路径)

注意:在这里面有很多的源文件并没有在Transceiver Example工程下,而是在Vivado安装路径下,之前我只是使用工程下源文件,但在编译阶段发现是有些模块是不在这个目录下,后来上网查到是由于ip中调用了Xilinx SecureIP包中的一部分,则指定下这个文件位置就可以了,但是编译一次找一个,文件少可以,要是文件很多岂不是工作量很大。后来发现使用vivado导出来的vcs文件中肯定会有文件的路径信息,执行仿真后果然发现了文件列表,找到一个名字叫src_files_verilog文件,将其使用的了Xilinx Secure文件路径都拷贝粘贴到rtl.f中。

(3)tb_top文件夹

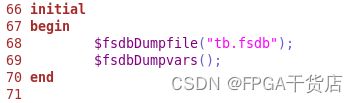

1)将Transceiver Example工程文件中的imports的*_top_sim.v文件拷贝到tb_top目录下,并在该文件中添加生成verdi的fsdb仿真文件语句;

2)在tb.f中添加仿真文件路径;

3)修改Makefile中DUT_TOP_MODEL_NAME和TB_TOP_MODEL_NAME变量,为*_top_sim.v中工程顶层例化名和仿真文件名;

将所有的文件修改完成后,就开始仿真流程了~~~

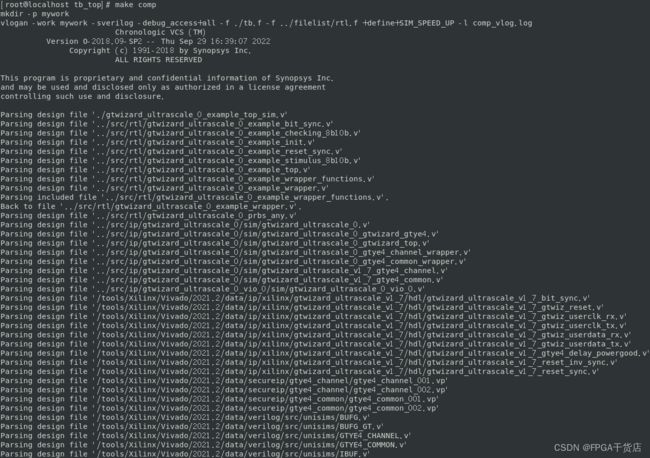

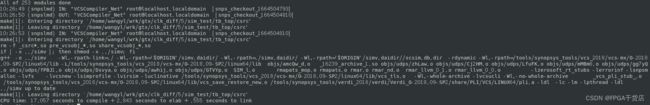

2.3.3Compile编译

在tb_top目录下执行make comp,编译完成后会看到生成一个名字为mywork的文件夹,将编译的库文件都存放在此目录下。

各编译选项:

- -work:用于指定库的位置。该选项后面的mywork称为logical library,而mywork在synopsys_sim.setup文件中指定了编译的路程称为physical library,所以该选项就是指定logical library 到 physical library 的mapping关系;

- -sverilog:编译支持Systemverilog文件;

- -debug_access+all:提高仿真性能;

- -f:指定文件,其中包含文件的路径名列表;

- -l:生成编译报告;

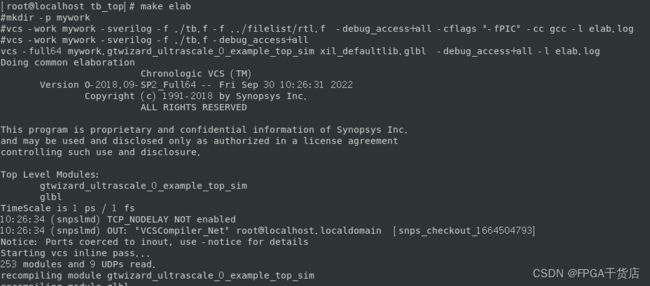

2.3.4elaborate编译

在tb_top目录下执行make elab,编译完成后会看到生成一个名字为simv的执行文件,用于进行后面仿真。

![]()

各编译选项:

- -full64:在64bit模式下编译、仿真,用于64位操作系统;

- -debug_access+all:提高仿真性能;

- -l:生成编译报告;

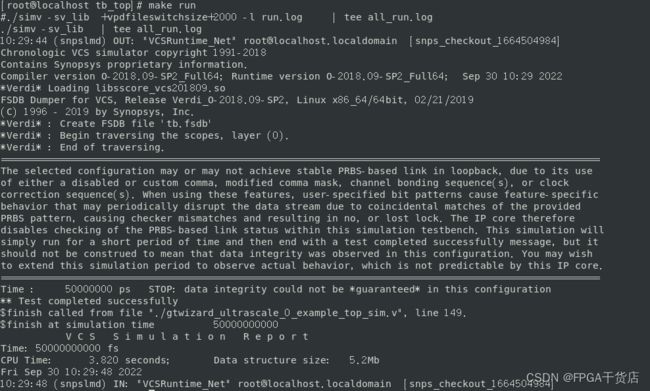

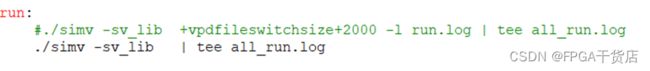

2.3.5simulate仿真

在tb_top目录下执行make run,仿真完成后就会看到在仿真顶层文件的tb.fsdb波形文件,用于Verdi软件打开波形。

在tb_top目录下执行make run,仿真完成后就会看到在仿真顶层文件的tb.fsdb波形文件,用于Verdi软件打开波形。

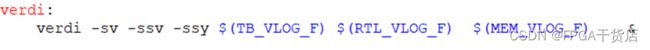

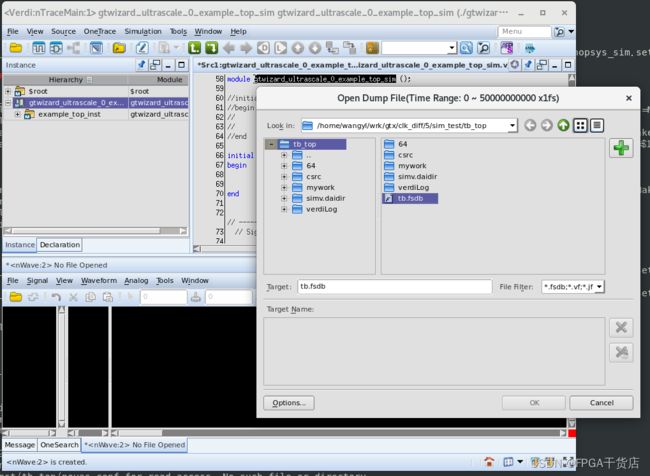

2. 3.6Verdi波形文件

在tb_top目录下执行make verdi,则Verdi软件打开了仿真的波形文件,选择打开波形文件后,添加所需查看的信号就可以看到波形了。

三、其他说明

VCS常用到的编译参数选项:

| 选项 |

说明 |

| -full64 |

在 64-bit 模式下编译、仿真,用于 64 位操作系统 |

| -notice |

详细的显示编译信息 |

| -debug_access+all |

提高仿真性能 |

| -j8 |

指定编译器可并行编译的进程数为 8 |

| -timescale=1ns/1ps |

指定仿真时间单位与精度,RTL 设计中没有指定 timescale 时,使用此设置 |

| +plusarg_save |

使能传参功能。 simv 仿真时可将具体数值传递给设计中的相关变量 |

| +libext+.v+.V+.sv+.svh |

识别 .v、.sv 等多种格式的设计文件 |

| -sverilog |

支持 SystemVerilog编译 |

| +memcbk |

使能多维数组变量 (Memory 类型) 的回调。配合 UCLI 接口,设置波形打印的信号范围时,指定 "+all" 选项,可以查看多维数组变量的波形 |

| -P |

指定使用的 PLI 表文件与库文件 pli.a 。其中 .tab 文件可以理解为 PLI 接口说明,pli.a 可以理解为系统函数库。 当然也可以指定用户自定义的 table 文件和自定义的函数库 |

| -cpp /usr/bin/g++-4.4 |

指定 VCS 可识别的 g++ 版本 |

| -cc /usr/bin/gcc-4.4 |

指定 VCS 可识别的 gcc 版本 |

| -f file.list -f macro.list |

指定包含所有设计文件列表的文件名,文件中可包括源代码文件的路径名称,和编译选项参数等。 建议 file.list 中存放设计文件列表,macro.list 存放编译参数等内容 |

| -top test |

设置顶层模块为 test。因为仿真包括 testbench,所以要设置最顶层的 testbench 为 top design |

| -l compile.log |

输出 VCS 编译的 log 至文件 compile.log 中 |

| +define+MACRO |

定义一个宏变量 MACRO,可作用到 Verilog 设计中 |

| +define+MACRO=10 |

为定义的宏变量 MACRO 指定具体值为 10 |

| -v |

指定库文件,建议包含路径,可指定多个 |

| -y |

指定库文件、IP 等 Verilog 模型的路径,可指定多个 |

| +incdir+ |

指定 `include 指令使用的包含文件的目录,可指定多个 |

总结

本文也是抛砖引玉,VCS的功能还是很强大,在慢慢的探索中继续分享~~~