Xilinx-7系列之可配置逻辑块CLB

目录

一、概览

二、CLB结构

三、Slice内部结构

3.1 SliceM结构

3.2 SliceL结构

3.3 查找表LUT

3.4 多路复用器

3.5 存储单元

3.6 进位逻辑

四、应用

4.1 分布式RAM

4.2 ROM(只读存储器)

4.3 Shift Registers( 移位寄存器)

4.4 存储资源容量估算

五、参考资料

一、概览

二、CLB结构

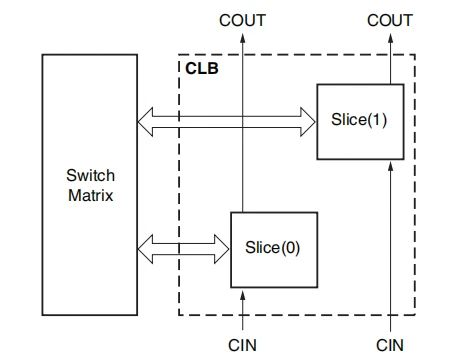

可配置逻辑块CLB(Configure Logic Block)是实现组合逻辑和时序逻辑的主要资源,由一对Slice(片单元)组成,每一个CLB都是连接到了一个交换矩阵(Switch Matrix)中。

每个Slice资源包含4个6输入的LUT,8个FF以及MUX和Carry。Slice又可分为SliceL和SliceM两种类型,在7系列器件中,大约2/3的Slice为SliceL,其余为SliceM,两者区别是SliceM可配置为分布式RAM(Distribute RAM)和移位寄存器,SliceL则不行。

每个CLB都包含一对Slice,这对Slice可能都是SliceL或是一个SliceLSliceM。属于一个CLB中的SliecL和SliceM是独立的,无相互连接的线路,只有属于同一列的Slice之间才会通过进位链进行连接。每个Slice有一个坐标XcYr,r为slice的列序号,c为行序号,同一个CLB的slice行序号是相同的。

三、Slice内部结构

3.1 SliceM结构

3.2 SliceL结构

SliceM和SliceL的大体结构相同,唯一的区别在于SliceM中每个LUT6的输入多了一路DI,并且CE信号中多了WE控制,正是这一差异使得SliceM可以将LUT配置成移位寄存器和分布式RAM。

3.3 查找表LUT

7系列器件中,可用LUT(Look-Up Table)实现函数生成器,LUT为6输入的LUT6。在一个Slice中,每个LUT6可作为一个6输入的LUT6或是2个5输入的LUT5,也可以是2个小于5输入的LUT。

6输入的LUT6时,A1-A6为输入,O6为输出。作为2个5输入或更少输入的LUT时,A1-A5为输入,A6为高电平,O5和O6作为两个LUT的输出。

3.4 多路复用器

每个slice都包含3个多路复用器:F7AMUX,F7BMUX,F8MUX。F7AMUX,F7BMUX可将两个LUT6组合7输入的LUT7,F8MUX可将两个LUT7组合成8输入的LUT8。

1个LUT6可以实现4:1的选择器,2个LUT6可实现8:1的选择器,4个LUT6可实现16:1的选择器,以16:1的多路选择器为例,从每个LUT中选择2位D[1:0]作为选择位,其余4位D[3:0]作为数据选择输入位,4个LUT共16个选择输入位,结合F7AMUX,F7BMUX,F8MUX,选择位为4位,组合后即是有16种结果。

3.5 存储单元

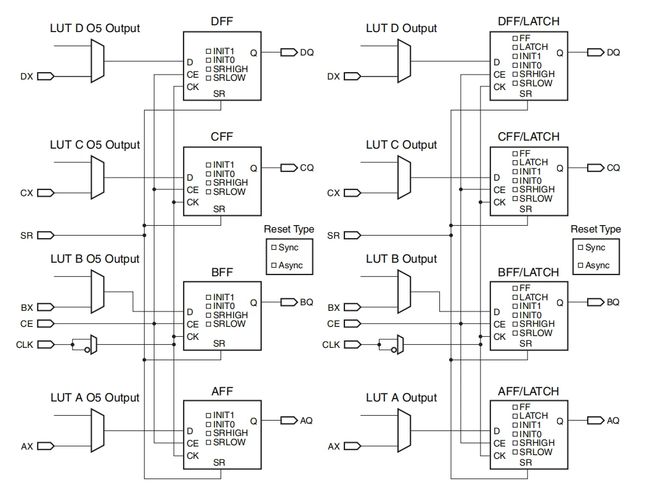

CLB中信号存储是通过触发器实现,每个Slice中包含8个触发器,前面4个只能配置为边沿触发的D触发器,后面4个可配置为D触发器或电平触发的锁存器。当后面4个配置为锁存器时,前面4个FF将不能被使用。

在下图中,8个FF是共用SR,CE,CLK信号,两个FF中如果存在控制信号不同,则不能放置到同一个slice中。8个FF都可以配置为不使用置位,复位,同步置位,同步复位,异步置位,异步清零的FF。

8个FF中,前4个和后4个FF的D端口数据来源也不同,前者来自LUT6的O5输出,后者来自LUT6的O6输出。同时,也都可以来自外部Switch matrix,通过AX,BX,CX,DX进入

3.6 进位逻辑

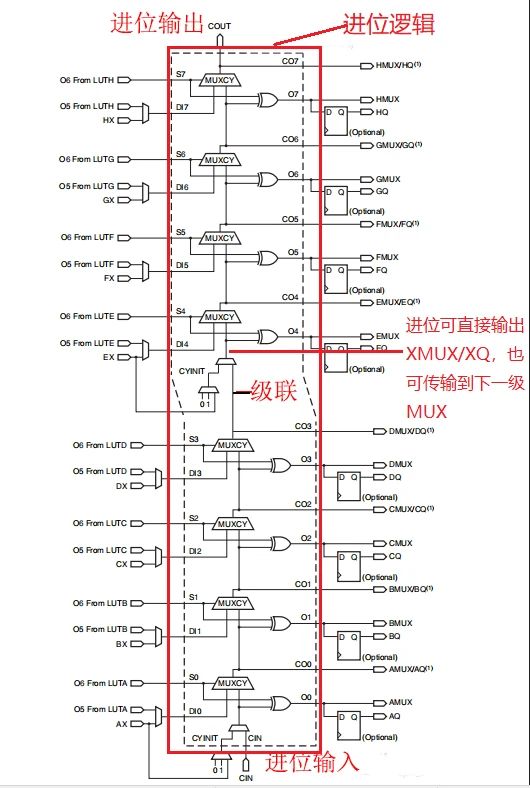

Carry可以快速实现算术加减法运算,一个slice包含一条进位链,同一列的slice可以进行级联实现更多位的加减法逻辑。

四、应用

4.1 分布式RAM

前面的章节提到sliceM可以配置为分布式RAM,RAM是中随机存取数据的单元,根据地址可对RAM进行读写操作。分布式RAM指由LUT构成的RAM,除了分布式RAM,还有专用的BRAM单元,用于存储更多的数据,少量的数据建议用分布式RAM。

以器件xc7k480tffv1156-1为例,BRAM分布如下图红色小方块,按列分布。

分布式RAM根据规格大小以及端口类型可划分如下,规格中包含了RAM的深度和宽度,格式为深度x宽度+端口类型,端口类型包括单端口,双端口,四端口,简单双端口,原语即为设计时进行实例化时使用。

涉及到具体器件时会存在差异,具体可在Language Templates中搜索RAM查看LUTRAM

分布式RAM是同步写入,异步读取,在写使能信号WE为高电平时,并且处于时钟跳变沿时,数据写入到RAM中指定地址的空间中。数据读取则是异步操作,每次地址引脚的数据更新后,在经过LUT的时延后将指定地址的数据输出。

4.2 ROM(只读存储器)

CLB中SliceL和SliceM的单个LUT都可以实现64*1比特的ROM,因为包含4个LUT,当对4个LUT都进行配置时,可实现ROM256*1比特的ROM

4.3 Shift Registers( 移位寄存器)

移位寄存器可用于延时补偿,实现同步FIFO,进行跨时钟域。CLB中的SliceM可以只使用LUT,不使用FF来配置成32比特的移位寄存器,单个LUT可实现数据1-32个时钟周期的延时。也可将一个SliceM中的4个LUT进行级联,可最大实现128个时钟周期的延时。若需更大的移位,可将SliceM级联。

使能信号CE与时钟同步,固定的在Q31中读取数据,LUT的最低有效为A[1]未被使用,工具将自动将其值设为1,A[6:2]为5位的地址,数据在Q(LUT6的O6)中进行输出。如果要进行同步读取数据,则将输出O6连接到一个FF中。移位寄存器不支持置位或复位,但在配置后可将其初始化为任何值。

4.4 存储资源容量估算

根据对实现分布式RAM,移位寄存器的实现可以根据器件的SliceM和FF资源数计算最大容量,一个LUT6可实现64bit的分布式RAM,一个SliceM可实现的容量为4*64bit=256bit,4个SliceM可实现4*256bit=2^10bi=1Kb。因此,SliceM的数量为分布式RAM容量的大小的4倍。

下表为Artix-7系列器件资源表,SliceM数量和分布式RAM数量关系基本符合4倍左右。

五、参考资料

官网用户手册《ug474_7Series_CLB.pdf》

文档获取

链接:https://pan.baidu.com/s/1doSb8K0EJF8GQr6lGOWYyw

提取码:svhl