根据逻辑分析仪实际波形,解析IIC通信及可能出现的问题(从机控制时钟SCL)

1、通信是信息的传递

1.1、信息

信息是多种多样的,在数字电路中,最基本的信息是高低电平,高低电平的提供需要电路转化的,维持高/低是要消耗能量的,信息需要借助能量来存在。

1.2、传递

从发送端传递到接收端需要媒介(物质),可以分为有线和无线。

2、IIC通信

2.1、通信角色(主机、从机)

IIC的全称是Inter IC,意为IC器件之间的通信协议,占主导地位、负责控制何时开始/结束通信、通信什么特定内容的器件称为主机,被控的器件称为从机。

主机:通常是可编程的控制端,比如各种单片机(stc8,stm8,stm32);

从机:通常是实现具体功能的,比如电池管理(电量计bq40z50)、屏幕显示(0.96寸OLED),数据存储器(AT24C02);

2.2、通信角色(发送端、接收端)

7位从机地址,加1位读写控制,这个读写控制的就是发送/接收的角色转换。

主机首先作为发送端,7位从机地址+1位写,代表主机向从机写数据,主机将继续作为发送端,那么从机就是接收端;

主机首先作为发送端,7位从机地址+1位读,代表主机从从机读数据,主机将转而作为接收端,那么从机就是发送端;

2.3、通信的开始和结束信号

起始信号:SCL 是高电平时, SDA 由高电平向低电平切换;结束信号: SCL 是高电平时 , SDA 由低电平向高电平切换;

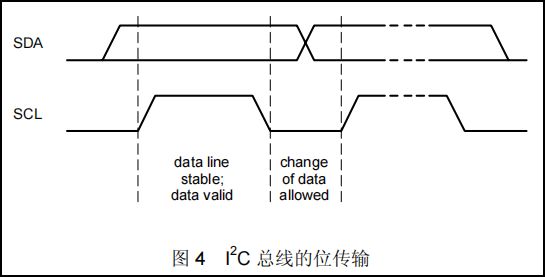

2.4、通信的最小单位(位传输)

通信其实就是要做到:发送端发送什么,接收端就接收什么。

比如要传输0x16,二进制00010110,下图是单独数据线SDA的0x16的波形,如果你是接收端如何解析,会不会把3个0当成2个0?会不会刚好检测到01的跳变的时候导致数据错误?

有了时钟,我们就可以解决:

1、每个位的长度:1个时钟周期代表1个位;

2、数据检测的时机:高电平数据有效,低电平允许数据变化;

下图是时钟SCL和数据SDA的共同波形,现在你就可以清楚地知道发送的数据是什么了。

补一个位传输的时序图:

2.5、通信的一个个数据(字节传输)

传输8个位就是1个字节,需要注意的是先传输MSB,也就是最高位。

2.6、响应

响应是在发送端发送一个字节的数据后,下一个时钟周期高电平期间,数据线上的电平状态,低电平0代表响应,高电平1代表不响应;

不管是响应ACK还是不响应NACK,都是通信过程中的一个信息。

3、实例

3.1、从机(电量计应用手册)要求的IIC通信流程如下:

“主机-发送端”:起始位

“主机-发送端”:地址+写

“从机-接收端”:ACK

“主机-发送端”:Gauge指令

“从机-接收端”:ACK

“主机-发送端”:重新起始位

“主机-发送端”:地址+读

“从机-接收端”:ACK

“从机-发送端”:第一个字节

“主机-接收端”:ACK

“从机-发送端”:第二个字节

“主机-接收端”:NACK (表示主机读取数据完毕)

“主机-发送端”:停止位

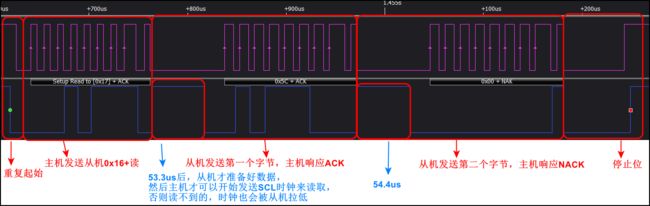

3.2、逻辑分析仪波形

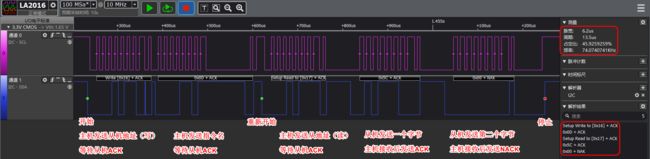

3.2.1、先看实际总体的波形

从波形和右下角IIC解析结果,可以看到数据通信是成功的。

由于是GPIO口模拟IIC,受程序中别的代码影响,时钟SCL并不是标准的占空比50%的固定频率的时钟,大概是占空比为46%、74KHz的时钟;

从这里也可以反映出前面2.4节说的时钟的必要性,现实情况下难免不准,每个位的时间并不是固定的。

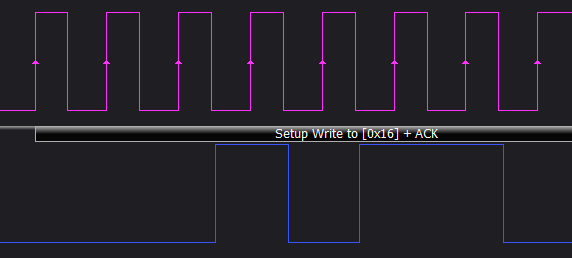

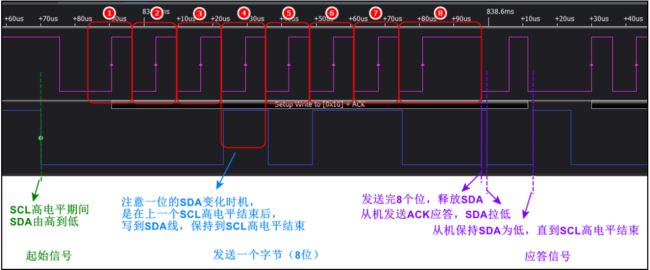

3.2.2、起始+寻址+应答过程

都在图中标了,位传输、从机应答信号

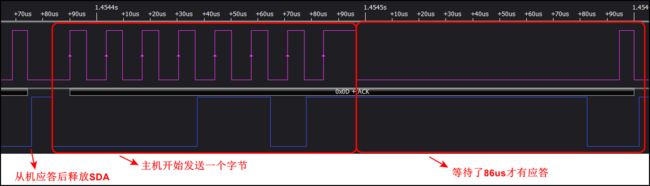

3.2.3、主机寻址后发送第一个数据+应答过程

可以看到第二次的应答非常慢,一开始这里认为从机有问题,一直没有ACK应答,后来才发现是有应答的,但是要等很久。

3.2.4、应答信号不在下一个周期,不代表从机没有应答

主机等待从机应答信号,不一定是发送完数据的下一个时钟周期就能等到,可能要等多个时钟周期,可以用标尺对比一下两次的从机应答时间。

3.2.5、从机需要准备数据之后,再发送数据

一开始是以为主机寻址从机应答,之后就可以直接开始读数据了,但是读不到,后面发现从机无法在收到主机读指令之后就准备好数据,要等待多个时钟周期,这个延时大概都是50us左右。

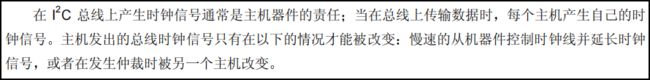

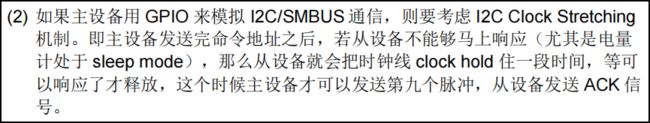

4、从机也是控制时钟SCL的

3.2.3和3.2.5中出现的问题,都是因为不知道从机也是可以控制时钟的,我一直错误地记忆主机控制时钟,从机根据时钟接收/发送数据。

下图来自《I2C总线规范》的第4章“I2C总线的概念” ,提到了慢速从机器件可以控制并延长时钟信号。

下图来自《TI 电量计应用指导》的5.2.1 电量计通信协议,也提到,如果从设备不能马上响应,会把时钟线hold住延长,等可以响应了再释放。

这就解释了实际波形中,从机应答和从机发送数据前,出现的SCL线较长时间被拉低的现象。