Boost升压电路调试

背景:

项目用到了一款升压电路,将12V升压到32V,电流要求有12A,最大18A。

设计的方案是使用Boost Controller + 外置MOS来实现。

选定的Controller芯片为Maxim的MAX25203。

问题:

回板后进行调试,在不使能芯片EN的时候,可以测到Vout端有12V的电压,这个电压是输入电压经过NMOS的体管漏过来的,符合预期,同时也说明没有短路等异常。

但当把芯片的EN拉高后,输入端的12V电源便直接被拽下来了。此时输出端是空载的,输入12V的电源使用的是稳压电源,限流10A,电压被拽到约4V左右,此时的输出端还是有电压的!只不过不是预期的32V,而是一个20多V波动的值。

算下来整板消耗了大概40W的功率,这…怎么看也不像是一个空载的Boost电源应该具有的正常功耗,而且输入电源已经过流保护,很明显电路不正常,出问题了。

这么大的电流必定是回到了GND上,而回到GND的路径似乎只有MOS,事实也证实了猜测,因为发热源就是MOS,而且MOS的下管比较热。

测试:

最开始也有比较怀疑的几个点,但都一一被推翻了:

1、芯片自身问题,因为当时做SMT时没有申请到样片,而是从中发抓的现货,不确定是不是芯片的问题,其实这个方向我们不太怀疑,因为不止一块板子出现这种情况,都出问题而且现象相同,就不像是个别芯片自身体质的问题了。后来找Maxim原厂申请到了芯片,替换上做了验证,还是同样的问题,这个原因可以排除。

2、电路原理图设计问题,普遍性的问题出现,问题可能出现在设计端,原理图设计出错是很有可能的,为了排除这个问题,我们又将自己的电路图与Demo板的电路图进行了对比,一个pin一个pin的对比,其中也包括了symbol和footprint的检查,没有发现什么问题。

不过区别也有,比如芯片有一个PGATE引脚,用来控制一个外置的PMOS,手册上说若是不使用,可以接地,但是我们的设计里面直接将他悬空了。因为当时我们设计的时候发现它就是一个输出的功能,怎么使用似乎并不会影响到芯片的逻辑,因此就悬空处理了。

为了验证是不是这个问题,我们进行了飞线操作,从这个QFN芯片的引脚处飞了一根漆包线,连接GND上(焊接有点难啊),结果肯定还是不行的,这个不是引起异常的根本原因。

在过程中,我们还发现了芯片手册上的一个bug,电流回采的CS2P和CS2N接反了(当然我们还飞线改成这种反着的,结果自然还是会出问题)。

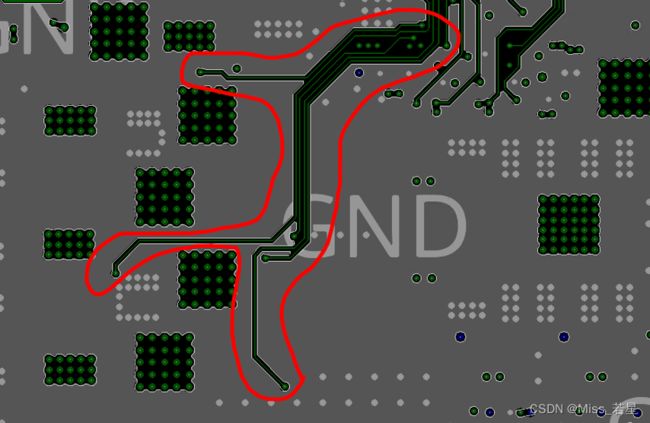

3、layout问题,既然从原理上没有发现什么问题,那么会不会是layout有问题,MOS的控制线被干扰了?一番查找,发现四颗MOS的控制线是并行着走在了一起,这个确实不好,会有干扰。但到底是不是它的问题,我们又做了验证,断开串接的0Ω电阻,直接飞线,将这四个控制线接到Gate级上,结果还是一样,而且没有什么改善的趋势,看来这个也不是根本原因。

其他的地方就没有发现什么问题了。目前没有证据证明是layout的问题。

4、软件问题,会不会是软件呢,因为这个芯片是有IIC接口的,是有什么东西需要IIC配置一下后才能正常工作嘛,仔细阅读手册后,这个假设也不成立,因为芯片只有EN拉高之后才能使用IIC接口,而EN一拉高就已经“弱短路”了,软件根本没有机会参与,因此和软件没关系。

5、电感选型问题,会不会选型有问题呢,大电流经过MOS管回到GND,这中间电感似乎没有起到阻碍电流的作用啊,下管一开,输入直接短地?难道电感饱和了吗,查看电感的参数,3.3uH,最大可以通过26A的电流,直流DRC3.3mΩ,理论电流很大,没啥问题啊。

后来我们还怀疑是不是感值选小了,于是试了4.7uH、10uH、22uH,但是都不太行,最终也是暂时排除了电感的问题。

6、MOS选型问题,这才是正解,其实一开始我们就有怀疑过MOS有问题,但是实测过MOS的Vgs电压,电压值确实大于MOS的开启电压(1.7V),所以MOS是可以充分导通的,因此就没有再把精力放在它的身上,直到后面拿到了Maxim的EVM板,将板子测试了个遍,最终决定更换它的MOS管到我们的板子上,才惊奇得发现电路可以正常跑起来了,输出电压32V正常了。

分析原因:

经过对比,发现了EVM板和我们板子上的MOS的区别,我们最开始选用的是一种逻辑电平的MOS,Vgsth电压在1.7V左右,而EVM板上的MOS是一种功率MOS,开启电压大概在3V左右。

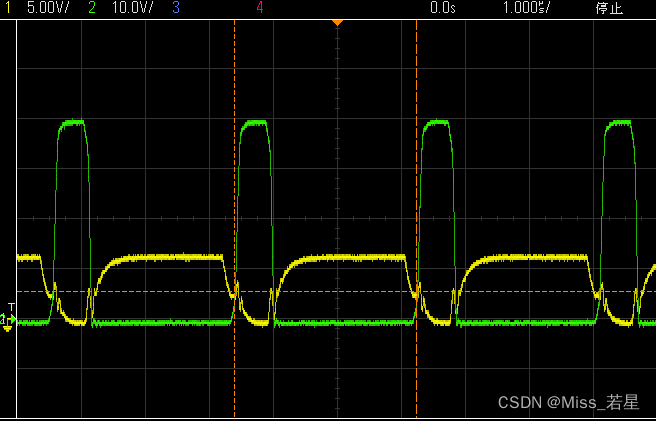

因此在上下管开启、关闭的交界处,可能会让MOS的上下管出现同时导通的情况,导致输出端直接对地短路,电容上存储的能力被释放,下个时刻电感又继续给这些电容充电,最终导致了输入端呈现了一种类似短路的状态。如下图为异常和正常状态的上下管Gata级波形。

其实就是因为MOS管选型不好,导致了死区控制有问题,Boost不像Buck一样,出现了上下管短路大概率烧MOS,这个是通过MOS放电,导致输入被拉下来。