OrCAD原理图绘制使用操作

文章目录

- 工程的创建

- 原理图整体设置

- 调用元器件库

-

- 常用元器件库调用

- :key:一些元器件库介绍

- :key:常用元器件搜索名

- 自建元器件库

-

- 新建元器件库

- 新建元器件

- 绘制元器件管脚设置

- :key:Homogeneous和Heterogeneous区别

- 其他选型设置

- 元器件绘制

- 自建库的保存

- 原理图绘制

-

- 同一页面内建立电气互联

- 不同页面内建立电气互联

- Net Alias与Off-page Connector区别

- 总线的使用方法

- 镜像

- 备注文本放置

- PCB封装检查

- DRC(设计规则检查)

-

- :key:DRC检查术语解释

- 创建输出网表

- 生成元件清单BOM表

- 打印原理图

- 快捷键或技巧

-

- 放大缩小

- 旋转元件

- 元件检索

- 重复放置

- 元件名下划线去除

- 元件管脚修改

- Edit-browse 的使用技巧

- 查找操作(CTRL+F)

- 批量替换/更新元件

- 备注

工程的创建

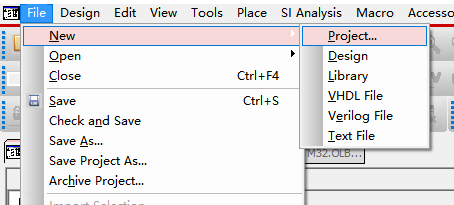

打开orcad,选择orcad capture,新建工程(file-new-project)

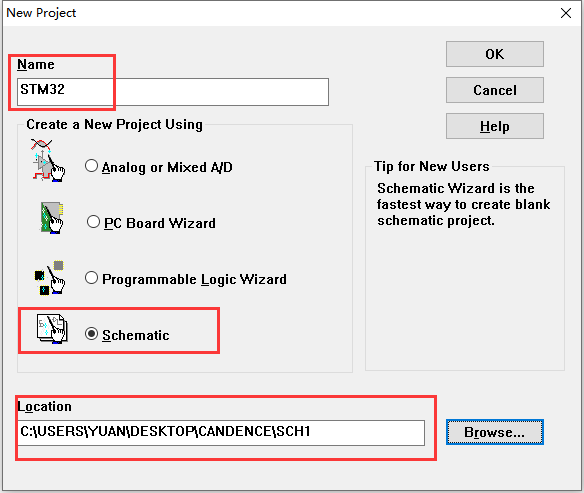

命名工程名,原理图,存放地址

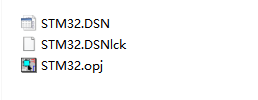

文件生成

其中.opj是工程文件,.DSN(design)为设计文件。只需要设计文件打开即可生成出其他文件,所以主要保存设计文件就行。

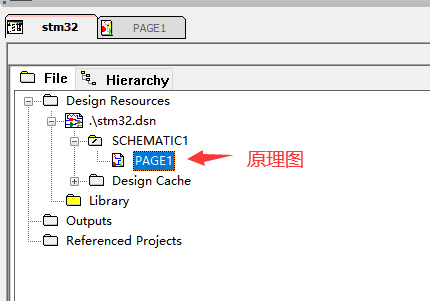

4.原理图设计

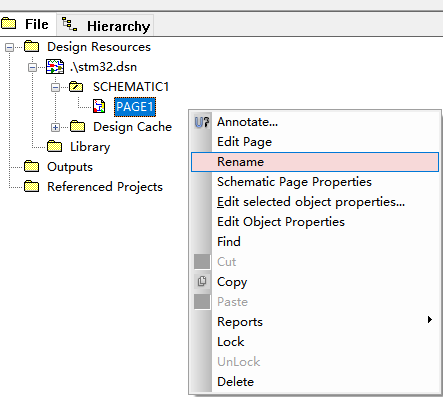

右键PAGE1-rename可对原理图重命名有实际意义的名字。

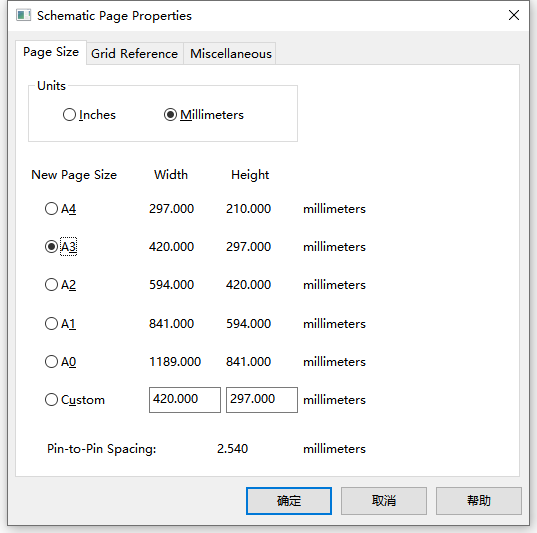

选择Schematic Page Properties可以设置原理图页面大小大小、栅格、单位等。或者选择Options-schematic paga properties 也可设置本页原理图。

一页绘制不完时可以新建原理图(New Page)

原理图整体设置

Options-Template用于总的模板设置,用于公用设置,边框显示、纸张大小、单位等。

Options-preference 可以设置原理图背景颜色

调用元器件库

常用元器件库调用

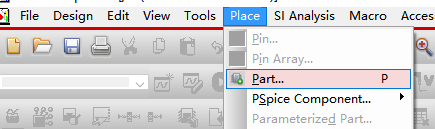

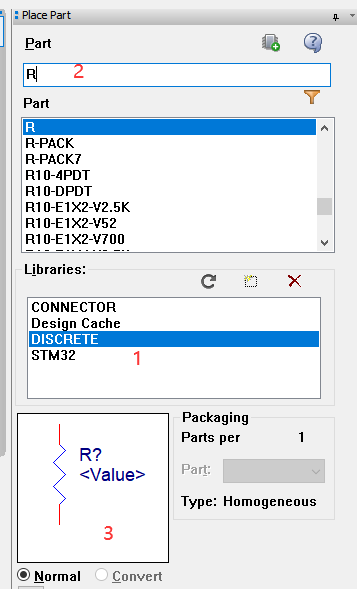

按P键或place-part或选型中的放置part图标以放置元器件。

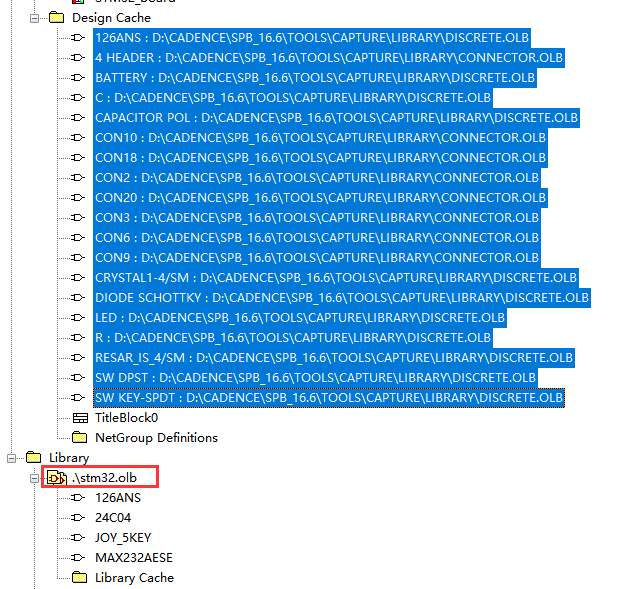

其中的为Design Cache本原理图中元器件库。放置使用过的元件,Design Cache中会出现已经使用的元件和元件来自的位置。

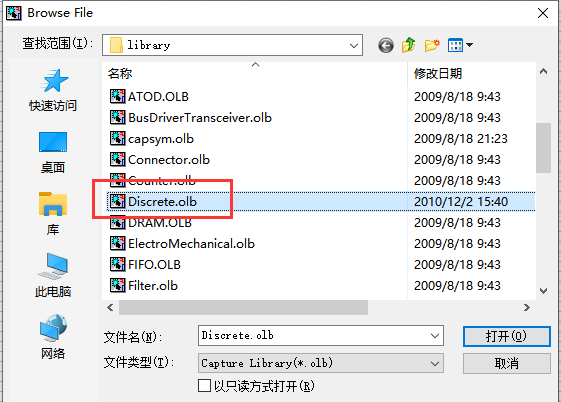

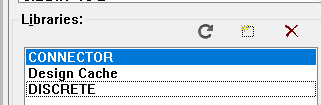

点击增加库,调用出需要的元器件库(Discrete(电阻电容二极管等等)和connector(连接器)),双击可放置元器件。(默认路径:Cadence\SPB_16.6\tools\capture\library)

出现3个库。

一些元器件库介绍

元器件库介绍:

AMPLIFIER.OLB:共182个零件,存放模拟放大器IC,如CA3280, TL027C, EL4093等。

ARITHMEtiC.OLB:共182个零件,存放逻辑运算IC,如TC4032B, 74LS85等。

ATOD.OLB:共618个零件,存放A/D转换IC,如ADC0804, TC7109等。

BUS DRIVERTRANSCEIVER.OLB:共632个零件,存放汇流排驱动IC,如74LS244, 74LS373等数字IC。

CAPSYM.OLB:共35个零件,存放电源,地,输入输出口,标题栏等。

CONNECTOR.OLB:共816个零件,存放连接器,如4 HEADER, CON AT62, RCA JACK等。

COUNTER.OLB:共182个零件,存放计数器IC,如74LS90, CD4040B。

DISCRETE.OLB:共872个零件,存放分立式元件,如电阻, 电容,电感,开关,变压器等常用零件。

DRAM.OLB:共623个零件,存放动态存储器,如TMS44C256, MN41100-10等。

ELECTRO MECHANICAL.OLB:共6个零件,存放马达,断路器等电机类元件。

FIFO.OLB:共177个零件,存放先进先出资料暂存器,如40105, SN74LS232。

FILTRE.OLB:共80个零件,存放滤波器类元件,如MAX270, LTC1065等。

FPGA.OLB:存放可编程逻辑器件,如XC6216/LCC。

GATE.OLB:共691个零件,存放逻辑门(含CMOS和TLL)。

LATCH.OLB:共305个零件,存放锁存器,如4013, 74LS73, 74LS76等。

LINE DRIVER RECEIVER.OLB:共380个零件,存放线控驱动与接收器。如SN75125, DS275等。

MECHANICAL.OLB:共110个零件,存放机构图件,如M HOLE 2, PGASOC-15-F等。

MICROCONTROLLER.OLB:共523个零件,存放单晶片微处理器,如68HC11, AT89C51等。

MICRO PROCESSOR.OLB:共288个零件,存放微处理器,如80386, Z80180等。共1567个零件, 存放杂项图件, 如电表 ( METER MA), 微处理器周边 ( Z80-DMA)等未分类的零件。

MISC2.OLB:共772个零件,存放杂项图件,如TP3071, ZSD100等未分类零件。

MISCLINEAR.OLB:共365个零件,存放线性杂项图件(未分类),如14573, 4127, VFC32等。

MISCMEMORY.OLB:共278个零件,存放记忆体杂项图件(未分类),如28F020, X76F041等。

MISCPOWER.OLB:共222个零件,存放高功率杂项图件(未分类),如REF-01, PWR505, TPS67341等。

MUXDECODER.OLB:共449个零件,存放解码器,如4511, 4555, 74AC157等。

OPAMP.OLB:共610个零件,存放运放,如101, 1458, UA741等。

PASSIVEFILTER.OLB:共14个零件,存放被动式滤波器,如DIGNSFILTER, RS1517T, LINE FILTER等。

PLD.OLB:共355个零件,存放可编程逻辑器件,如22V10, 10H8等。

PROM.OLB:共811个零件,存放只读记忆体运算放大器,如18SA46, XL93C46等。

REGULATOR.OLB:共549个零件,存放稳压IC,如78xxx, 79xxx等。

SHIFTREGISTER.OLB:共610个零件,存放移位寄存器,如4006, SNLS91等。

SRAM.OLB:共691个零件,存放静态存储器,如MCM6164, P4C116等。

TRANSISTOR.OLB:共210个零件,存放晶体管(含FET, UJT, PUT等),如2N2222A, 2N2905等。

常用元器件搜索名

选择库,输入元器件名(不知道就依次查找),看显示的器件是否是需要的器件。双击放置。

常用器件名

电阻 Discrete-R

普通电容 Discrete-C

极性电容 Discrete-CAPACITOR POL

发光二极管 Discrete-LED

稳压二极管 Discrete-DIODE SCHOTTKY

排阻 Discrete-RESAR_IS_4/SM(需要几排阻就换数字几)

晶振 Discrete-CRYSTAL

电池 Discrete-BATTERY

单刀双掷开关 Discrete-SW SPDT(signal double)

双刀单掷开关 Discrete-SW DPST(double signal)

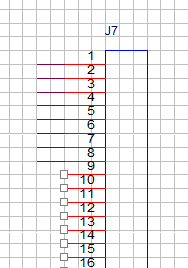

插座 CONNECTOR-CON2(需要几pin的就是CON几)

自建元器件库

新建元器件库

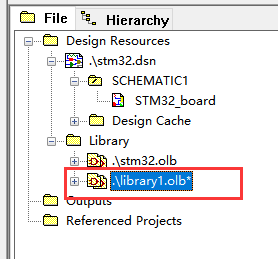

对于器件库中没有的器件如一些芯片等需要我们自己绘制元器件。

file-New-library

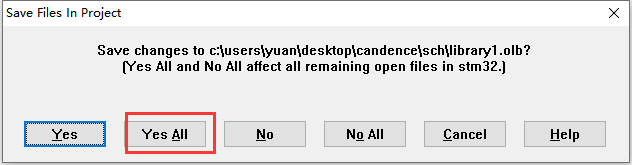

出现新的元器件库,点击保存,YES ALL,

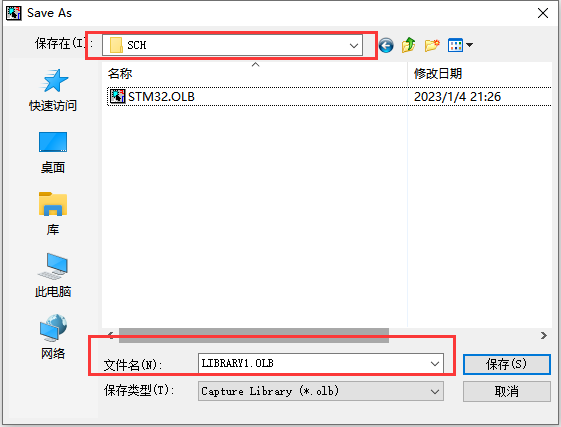

选择库存放位置(建议放在工程中),命名库名称。

新建元器件

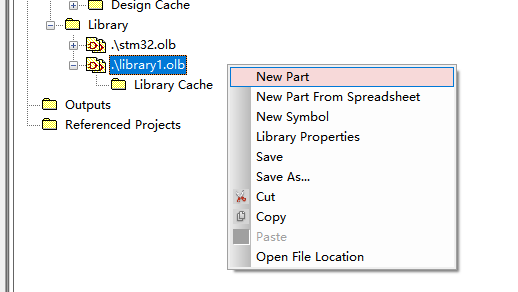

右键New part即可创建元器件。

输入part名称。对于不用分裂绘制的器件点击OK即可。

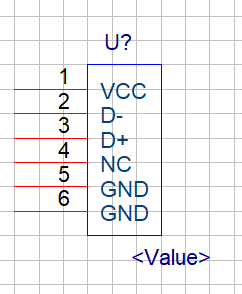

图N

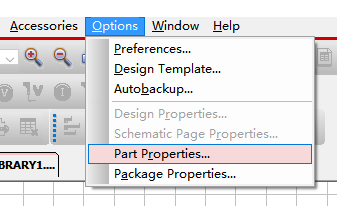

Options-part properties (或在元器件绘制界面双击鼠标左键)里可以设置是否显示元件number、name(元件名的隐藏)、value等。

Package properties 里可以重新修改元件name、单元U几等。

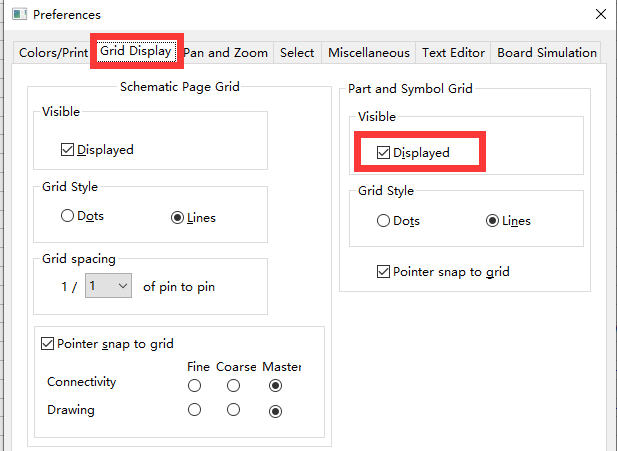

Options-Preferences中的Grid Display-Displayed能够选择界面是否显示栅格,默认是显示的。

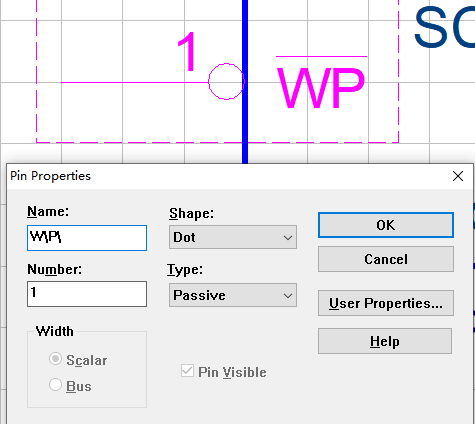

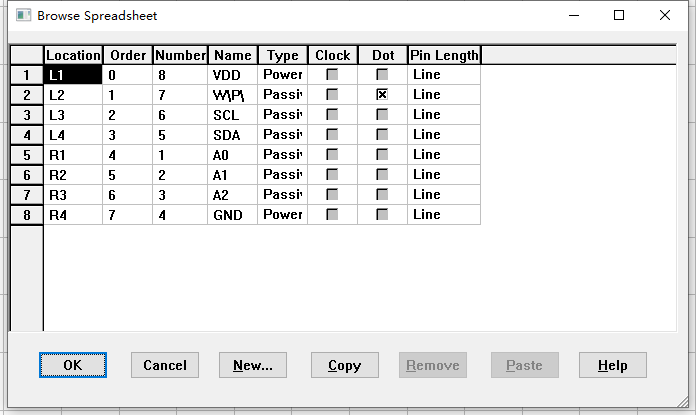

绘制元器件管脚设置

对于有电源属性的元器件管脚要设置Type为Power并勾线上Pin Visible以显示,其余可默认为Passive。

Homogeneous和Heterogeneous区别

分裂元件通俗地说就是同一个元件,分为几块画出来,最典型的就是FPGA,由于FPGA引脚众多,不可能在一块封装上画完,必须分为多个部分画出来。

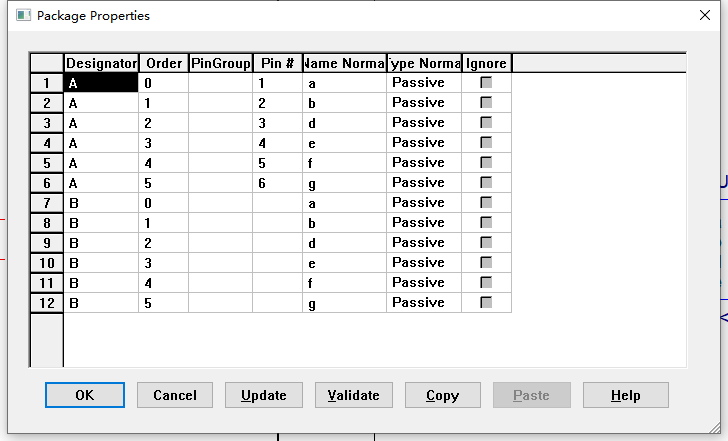

Parts per Pkg填的数字表示此元件分为几部分绘制。将元件分成几部分绘制就将的数字改成几。一个部分处用CTRL+N可以看到另一个相同部分。

VIEW- Package 可以看到一个元件的各部分,双击后放大。此时在点击Edit-Propertirs 也可以方便的修改各管脚名称。

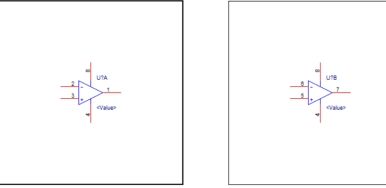

Homogeneous:绘制的各个部分的元器件相同,只需要画出其中一个part,其他part自动生成,相同模式下允许出现相同的管脚,如电源共用时。用于一块芯片集成有几个相同部分绘制,如对称式运放。

Heterogeneous:表示各个部分的元器件不同,每一个部分均需要重新绘制。用于引脚多,需要分开绘制的芯片。

其他选型设置

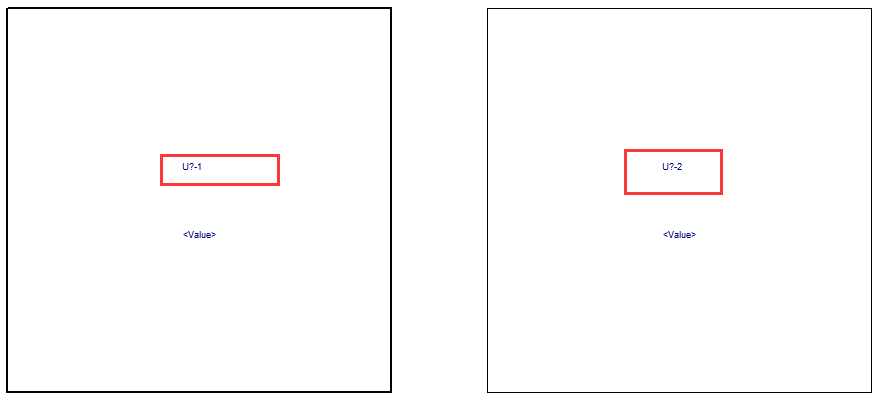

在图N中的Part Numbering选型中的Alphabetic(字母次序)、Numeric(数字的)生成出的器件名的排序方式不同。

选择Alphabetic时

选择Numeric时

元器件绘制

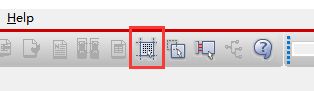

红框中为pin放置,其他为器件无电气部分绘制工具。

输入管脚名和编号,shape表示电气线的长短和形式,Type中选电气线的功能(默认为passive,VCC\GND等电源选择Power,记得勾选上Pin Visible)

双击非电气线可以设置线的样式和粗细。

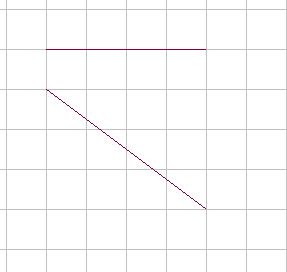

点击图标可以绘制线到非栅格点上

对于有上横线的管脚命名时需要加上\。

自建库的保存

复制cache(shift按住第一个和最后一个全选)粘贴到自建的.olb文件中,这样自建库工程中的.olb文件中就包含了原理图中的全部元器件。

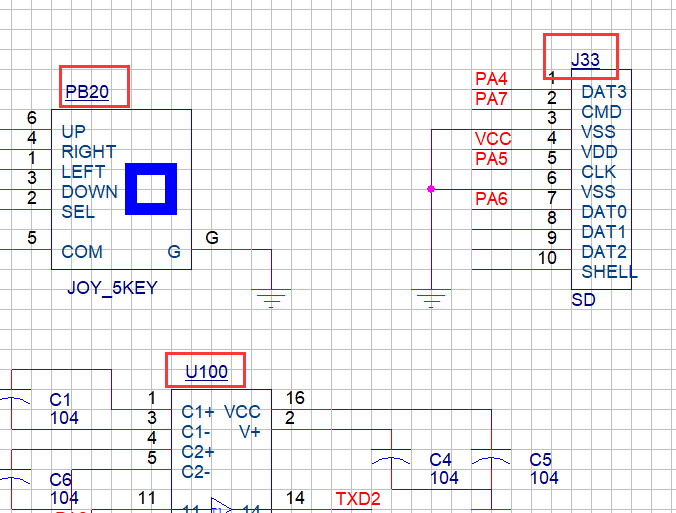

原理图绘制

原理图中先需要放置元器件,如何放置,在常用元器件库调用部分已经说明。全部元器件绘制放好元器件后便可以开始进行原理的的绘制了。

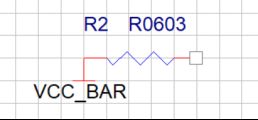

对于在同一页面的元器件可以用place-wire进行链接(或在英文状态线按下w实现线绘制命令),这是具有电气属性的线。

- Place no connect,用于管脚悬空设置。

- 两元件的互联最好不要直接放一起连接,而是中间用wire连接两部分,避免你在PCB是报错。

下图是将电阻和VCC直接连接。

下图是通过wire链接两元件。

同一页面内建立电气互联

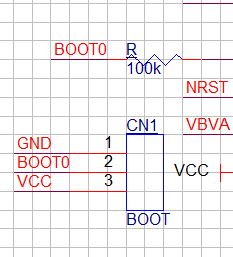

也可以通过增加网络标识实现各引脚的互联(快捷键N)。Place net alias(N)可以不用连wire来建立电气互联,只能用于本张原理图,不能跨图连接,跨图时用Place off-page connector.

具有相同网络名的管脚表示具有连接关系。如此处的BOOT0两处的网络名一样,所以表示此处是连接的。

不同页面内建立电气互联

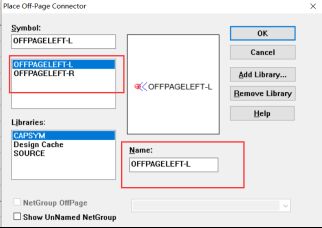

使用Place off-page connector。

![]()

两种模式,文字在左,文字在右。命名在Name中。

Net Alias与Off-page Connector区别

Net Alias与Off-page Connector都可以用于同一页面内的网络连接;

Off-page Connector可以用于不同页面之间的网络连接,而Net Alias不能实现此功能。

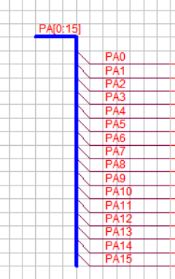

总线的使用方法

Place bus(B)放置总线,同样shift+bus可以放置任意角度总线。

![]()

总线放置好后,加上place bus entry(E)放置总线入口,按R可以调整方向,按F4可以快速连续放置。

注意:总线的电气连接必须用Place bus entry 来实现电气互联,如果只用wire实现总线的连接,实际上并没有形成真正的电气互联。

![]()

给总线加net alias 时,其总线名称有三种命名方式:

BUSNAME[0…31]

BUSNAME[0:31]

BUSNAME[0-31]

BUSNAME后不能以数字结束 如BUSNAME2[0…31]

BUSNAME与[之间不能有空格

总线命名为PA[0:15]时,wire 命名只能是PA0、PA1…

不能是PA[0]、PA[1]…

加net alias PA0后,继续点击可以得到PA2345一直到PA15。

两段总线形成的T型连接,默认自动放置连接点,电气上互联。

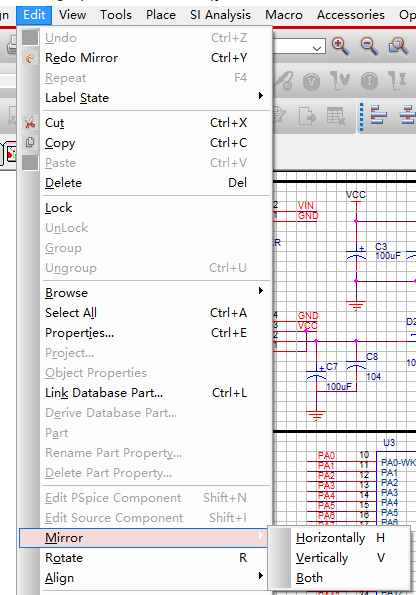

镜像

选择需要镜像的原理图,Edit-Mirror 可以实现水平、垂直、180°翻转镜像。

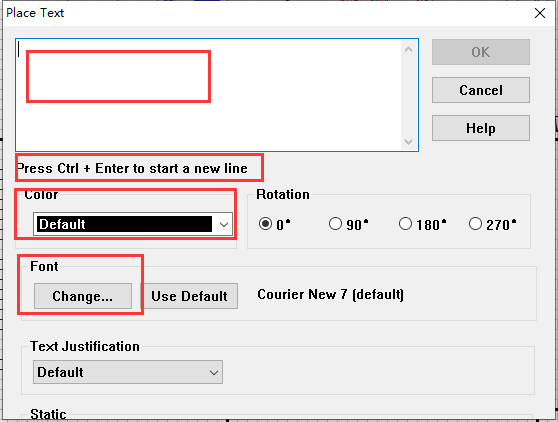

备注文本放置

在原理图加入文字说明时,用Place text(T),也可以是在工具栏Place-Text中选择。

第一个红框为文本内容输入。

第二个红框为换行操作(Ctrl +Enter)。

第三个红框为文本颜色选择。

第四个红框为字体及大小选择。

需要对文本加矩形、椭圆等外框时,可以选择右边工具栏放置(Place)。

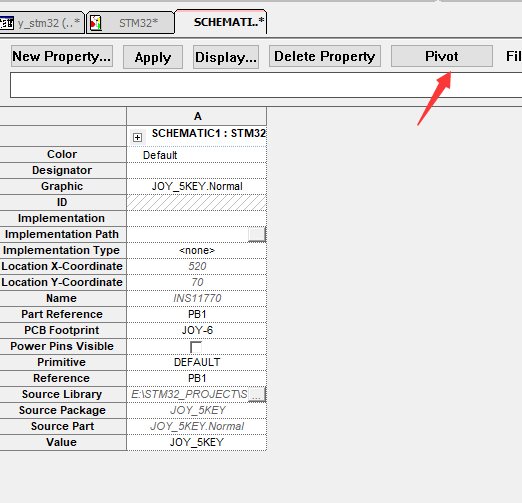

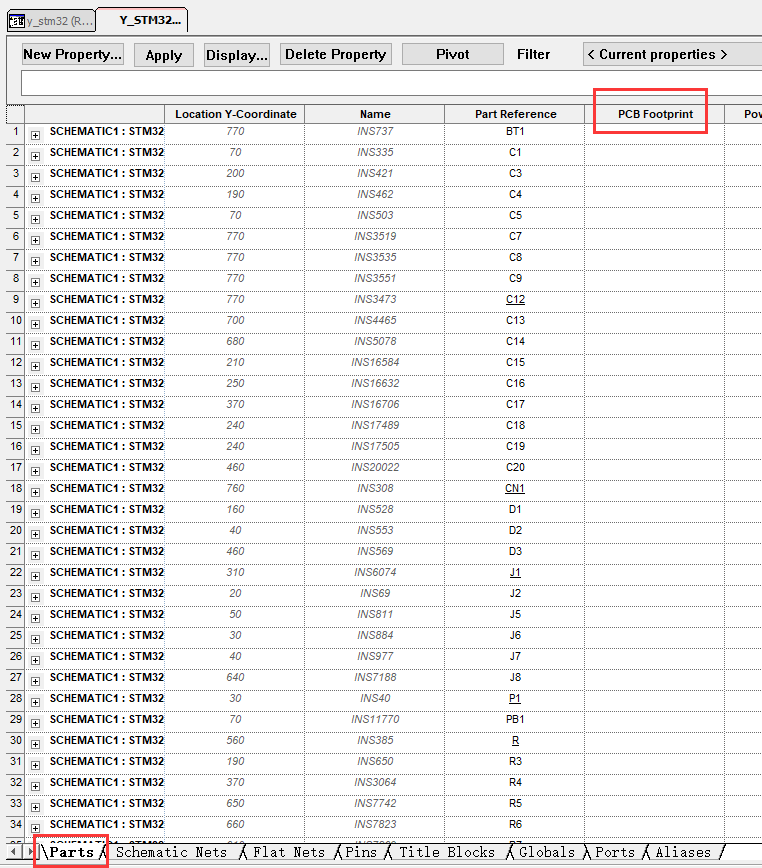

PCB封装检查

- 单个封装添加:双击原理图中的元件后会出现property Editor 框。在属性框中右键选择Pivot 可以水平或垂直显示属性。

在原理图处右键选择Edit Object Properties.在PCB Footprint中填写封装。

- 批量添加封装

选择parts填写PCB Footprint

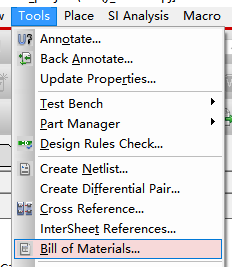

DRC(设计规则检查)

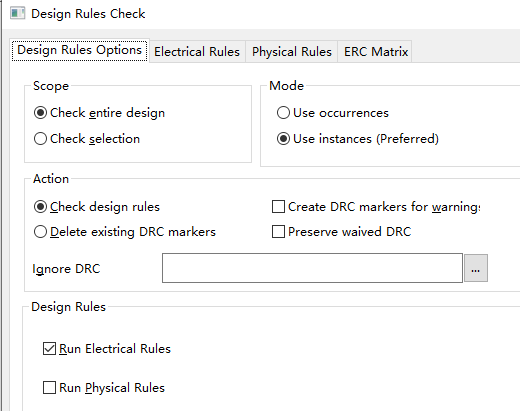

选择原理图根目录-Tools-DRC

一般按照默认的设置点击确定即可,输出的drc文件查看错误和警告进行修改。

DRC检查术语解释

Check entire design:DRC检查整个原理图;

Check Selection:DRC检查选择的部分电路;

Use occurrences:选择所有事件进行检查;

Use instances(preferred):使用当前实体(建议)。所谓实体是指放在绘图页内的元件符号,而事件指的是在绘图页内同一实体出现多次的实体电路。例如,在复杂层次电路图中,某个子方块电路重复使用了3次,就形成了3次事件;不过子方块电路内本身的元件却是实体;

Check design rules:对当前的设计文件进行DRC检测;

Delete existing DRC marker:删除DRC检测标志 Report;

Create DRC markers for warnings:进行DRC检测若发现错误,在错误之处放置警告标志;

Run Electrical Rules:勾选进行电气规则的检查;

Run Physical Rules:勾选进行物理规则的检查。

Check single node nets:检查设计中的单端网络;

Check no driving source and pin type…:检查器件属性无源管脚与有源管脚的连接是否正确;

Check duplicate net name :检查重复的网络名称;

Check off-page connector connect:检测分页图纸间接口的连接性;

Check hierarchical port connection:检测阶层端口的连接性;

Check unconnected bus net:检测没有连接的总线网络;

Check unconnected pins:检查没有连接的管脚;

Check SDT compatibility:检测对于SDT文件的兼容性;

Report all net name:报告所有网络的名称;

Report off-grid object:报告不在格点上是器件;

Report hierarchical ports and off-page connection:报告阶层端口和分页图纸间接口的连接;

Report Misleading Tap Connection:报告易误解的连接。

Check power pin visible:检测电源属性的管脚是否显示了管脚名称与编号;

Check missing/illegal PCB Footprint:检测封装名称是否填写。是否含有非法字符;

Check Normal convert view system:检测一个部件的正常视图上的pin号是否与转换视图上的pin号不同;

Check incorrect pin group assignment:检查同一个Pin Group的所有插脚是否有相同的类型;

Check high speed props syntax:在设计中检查网络高速属性的语法是否正确;

Check missing pin number:检测缺失管脚编号的管脚;

Check device with zero pins::检测设计中是否含有零宽度的管脚;

Check power ground short:检测一个Part内部的电源网络名称是否有两个不同的网络标号名称;

Check Name Prop consistency:检测层次原理结构中是否含有相同的网络名称;

Report Visible unconnected power pins:报告所有具有可见电源属性的管脚是否有连接;

Report unused part packages:报告原理图中未使用的器件part;

Report invalid Refdes:报告原理图中无效的器件位号;

Report identical part references:报告原理图相同的位号。

创建输出网表

或者

一般都是使用第一方网表,直接点击确认即可。报错就进行修改,不报错则会输出网表文件。

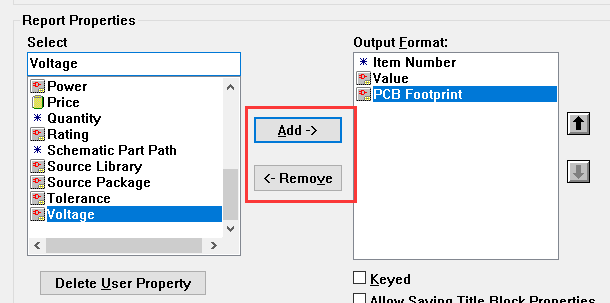

生成元件清单BOM表

- 选择DSN文件,选择Reports-CIS Bill of Materials-Standard

选择需要输出得内容output format.

勾画选择是否输出到EXCEL.

增加需要输出包含的内容

- 或者使用选择 Tools-BOM

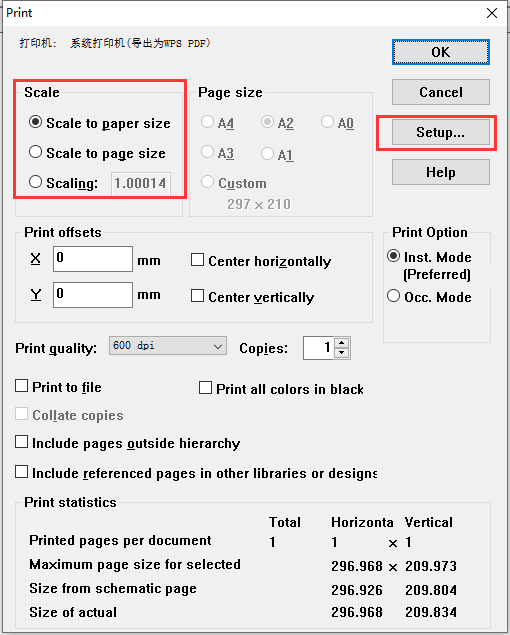

打印原理图

选择DSN文件,选择File-Print,点击Setup 选择打印纸张大小,横向还是纵向。就可以打印,也可以输出为PDF效果。

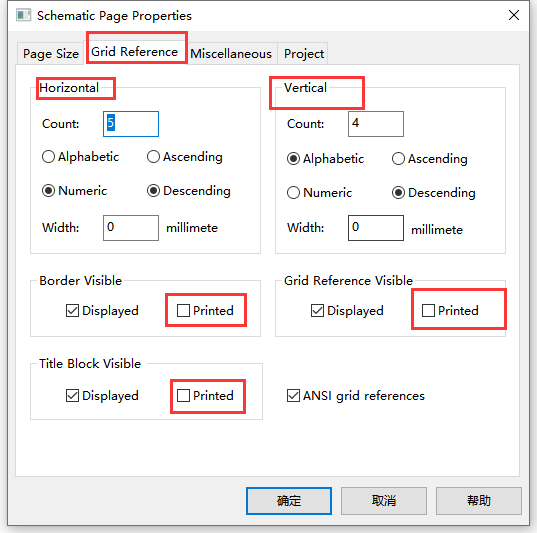

如果不想打印出有边框、数字标识等

![]()

选择对应的原理图(只能一个个设置)选择 Schematic Page Properties

取消勾选Print 即可使得打印出的原理图没有外围边框。

快捷键或技巧

放大缩小

- 原理图的放大、缩小:鼠标放置在需要缩放处,英文状态下i为放大,O为缩小。

旋转元件

- 双击放置元件时快捷键R,可使元件旋转后再放置。

元件检索

重复放置

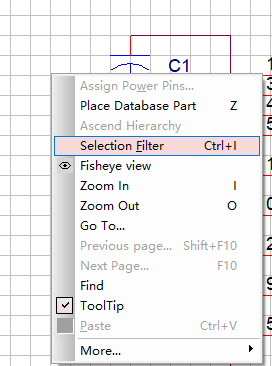

元件名下划线去除

- 原理图中修改的元件名有下划线,看这不习惯,可以进行整体去除。

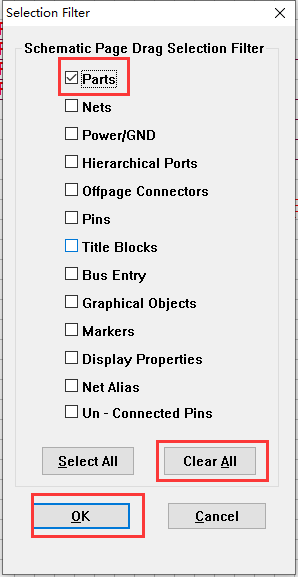

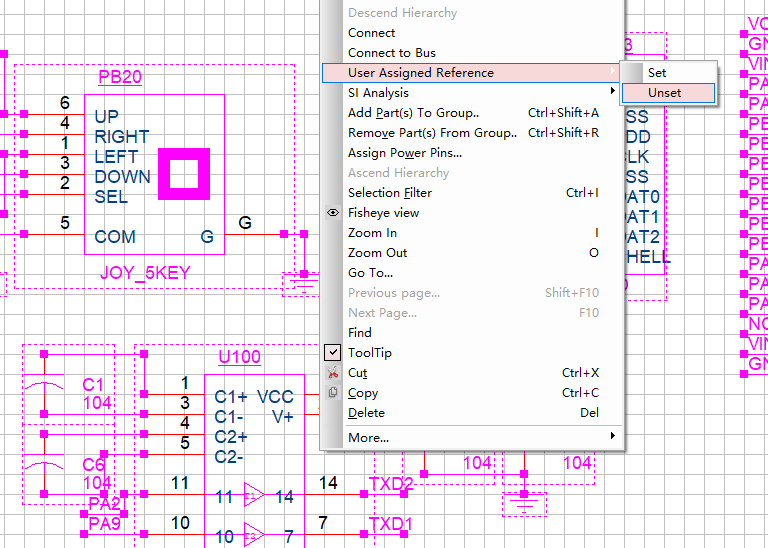

操作方式右键选择Selection Filter-Clear All-选择parts-点击OK,CTRL+A选择所有parts后在某一元件上右键点击-选择User Assigned Reference - Unset就消除了下划线。

元件管脚修改

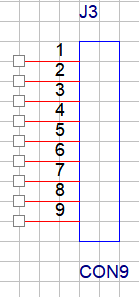

Edit-browse 的使用技巧

选择DSN文件,点击菜单栏中的Edit-browse(浏览整个设计工程)

选择某个原理图文件,点击菜单栏中的Edit-browse(浏览该原理图)

选择part

生成的part表中reference中可以看到哪些元件没有编号;value 中可以看到哪些元件没有赋值。

在part表中双击没有编号或赋值的元件可以快速定位到原理图中的位置进行更改。

Edit-browse-nets 生成网络连接表。

Edit-browse-off-page connector生成多页互联网络表。

Edit-browse-DRC markers 可以看到DRC检查中的错误,进行修改。

查找操作(CTRL+F)

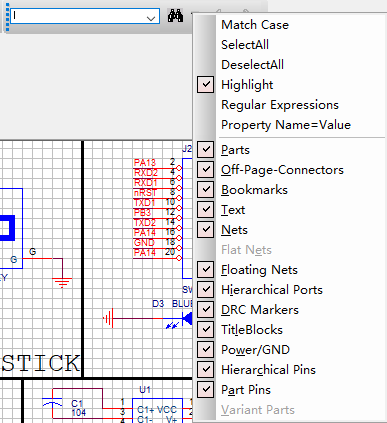

- 页面右上角可以查找元件、网络、电源等,对需要查找的进行勾画。

批量替换/更新元件

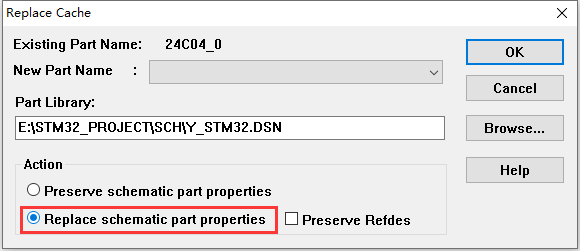

在Design Cache 中右键点击元件,选择 replace cache 可以替换元件。

在Design Cache 中右键点击元件,选择 update cache 可以更新元件(用于原来元件属性修改后更新)。

![]()

元件库中的PCB foot print修改后更新只能用replace cache后选择Replace schematic part properties 。

用update不能更新PCB foot print。

备注

原理图的元器件只表示连接关系,绘制时不用一定和实际的样式类似,例如下面的9脚座子可以用9pin连接件代替。