DSP芯片F2803x系列之PWM模块及高精度PWM使用

DSP芯片F2803x之ePWM模块

文章目录

-

-

- 1 ePWM模块概述

- 2 ePWM模块构成

- 3 ePWM各子模块

-

- 3.1 TB模块

- 3.2 CC模块

- 3.3 AQ模块

- 3.4 DB模块

- 3.5 PC模块

- 3.6 TZ模块

- 3.7 ET模块

- 3.8 DC模块

- 4 高精度PWM

-

1 ePWM模块概述

ePWM模块是电力电子数字控制中重要的部分。其主要功能和作用如下:

1 用于电力电子拓扑中可控功率器件的驱动信号;

2 实现DAC功能,有时ePWM也做为功率DAC的一部分;

3 用于继电器等器件的控制信号;

4 用于模拟一些带信息的信号,如模拟电机码盘信号。

2 ePWM模块构成

DSP中有多个ePWM模块,各个系列型号的ePWM模块数量不尽相同。

F2803x系列中,每个ePWM模块都包含两个PWM输出,EPWMxA和EPWMxB。其中,x表示第几个模块,x = 1,2,…。

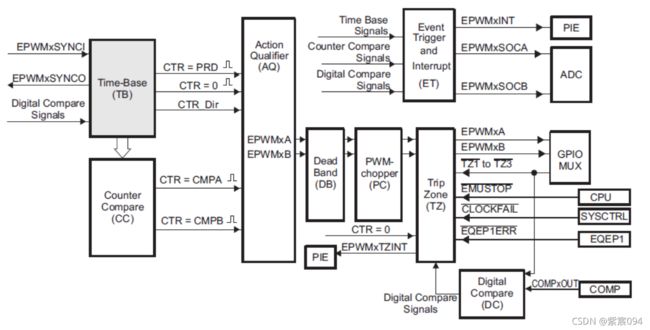

从图可知,各个模块的主要对外信号:

-

ePWM模块输出信号(EPWMxA和ePWMxB)

-

TZ信号( T Z 1 ‾ \overline{TZ1} TZ1~ T Z 6 ‾ \overline{TZ6} TZ6)

在ePWM模块外部发生故障时,可通过这些信号给ePWM模块示警。每个ePWM模块都可以选择使用或者不使用这些信号。

-

时基同步输入信号(EPWMxSYNCI)和时基同步输出信号(EPWMxSYNCO)

同步信号通过菊花链将ePWM模块连接在一起。每个模块都可以配置位使用或者忽略自身模块的同步输入信号。其中,只有ePWM1模块才可以将其输入输出同步信号带出引脚。ePWM1同步信号的输入输出也连接到eCAP1的同步输入信号上。

-

ADC起始转换信号(EPWMxSOCA和EPWMxSOCB)

每个ePWM模块都有两个ADC起始转换信号。任一个ePWM模块都可以触发一个转换起始。

-

COMP输出信号(COMPxOUT)

COMP的输出信号可以连接到TZ信号用于产生DC事件。

-

外设总线

外设总线是32位宽并且允许16位和32位写入ePWM寄存器文件。

每个ePWM模块包含以下子模块:

- 时基模块(TB, Time-Base Module);

- 计数比较模块(CC, Counter Compare Module);

- 动作模块(AQ, Action Qualifier Module);

- 死区模块(DB, Dead-Band Generator Module)

- 斩波模块(PC, PWM Chopper Module)

- 刹车模块(TZ, Trip Zone Module),也称联防模块

- 事件触发模块(ET, Event Trigger Module)

- 数字比较模块(DC,Digital Compare)

子模块和外部信号如下图:

每个ePWM模块的特点如下:

-

16位专用时基计数器用于控制周期和频率

-

两个PWM输出,并且可以配置为:

-

两个独立单边缘操作输出;

-

两个独立双边缘对称操作输出;

-

一个独立双边缘非对称操作输出;

-

-

通过软件异步控制PWM信号

-

可编程控制相对于其他ePWM模块的超前/滞后的相位

-

逐周期硬件同步相位关系

-

独立的上升沿/下降沿延时控制死区

-

TZ可设置为CBC和one-shot

-

TZ控制可强制PWM的输出为高、低、高阻态

-

比较器模块的输出和TZ输入都可以产生事件、滤除事件或TZ条件。

3 ePWM各子模块

3.1 TB模块

TB模块在ePWM的部分如下:

TB模块的作用:

-

设定TB计数器的周期频率

-

管理和其他ePWM模块的同步

-

设定和其他模块的相位

-

设定计数模式,计数模式有增计数模式、减技术模式和增减技术模式

-

产生事件:

- CTR = PRD时产生事件;

- CTR = ZERO时产生事件;

-

配置TB时钟速率

TB计数共有三种模式

其计数方式及周期频率计算方式如下:

周期影子寄存器

为了避免软件异步装载寄存器的值导致出现不可预料的错误,因此有影子寄存器。影子寄存器不直接用于硬件,而是作为一个缓冲,当特定条件下装载到活动寄存器,作用于硬件。

对于TB模块,可以选择不使用影子寄存器而是直接作用,也可以选择使用影子寄存器。使用影子寄存器时,只有当TBCTR = 0x0000时,影子寄存器的值装载到活动寄存器作用于硬件。

同步信号

使能同步信号时,所有使能的ePWM模块时钟都开始于TBCLK的第一个上升沿。为了能正确的使能TBCLK,每一个ePWM模块的顶预定必须设置一样。

每个ePWM模块都有同步输入和同步输出信号。其中,ePWM1的同步输入信号来源于外部引脚。各ePWM模块同步信号之间的连接如下图:

虽然模块内部是这样连接的,但是针对每个模块,都可以选择使用或者不使用同步信号。当使用同步信号时,出现以下情况可使得TBCTR自动装载相位寄存器TBPHS的值:

- 输入同步脉冲,当输入同步脉冲来时,将在下一个TBCTR上升沿将相位寄存器的值给到TBCTR,产生的延迟:

- 当TBCLK = SYSCLKOUT时,延迟为2 x SYSCLKOUT

- 当TBCLK != SYSCLKOUT时,延迟为1个TBCLK

- 软件强制同步

- DC事件同步脉冲

TB的计数可以同步,而TBCLKSYNC位可以被用于同步使能的ePWM模块的TB时钟。这个位是设备时钟使能寄存器的一部分。当TBCLKSYNC = 0,TB时钟是停止的(默认);当TBCLKSYNC = 1,所有的ePWM模块的TB时钟就开始了,并起始于TBCLK的上升沿。为了能够正确地同步TBCLK,TBCTL的预定标位必须设定为一样的。正确处理ePWM时钟的方式步骤如下:

- 使能各自的ePWM时钟;

- 设定TBCLKSYNC为0,这将停止每一个使能的ePWM模块的TB时钟;

- 配置预定标的值和ePWM模块;

- 设定TBCLKSYNC为1;

3.2 CC模块

CC模块在ePWM的部分如下:

CC模块的输入是时基计数器的值。CC模块将该值持续和CMPA和CMPB寄存器比较。当数值相等时,产生对应的事件。如果AQ配置为对应的设定,那么可以使用CC模块改变PWM的占空比。

3.3 AQ模块

AQ模块在ePWM的部分如下:

AQ模块作用:

- 基于如下事件产生动作:

- CTR = PRD

- CTR = ZERO

- CTR = CMPA

- CTR = CMPB

- 管理事件同时发生的优先级

- 当设置为增计数或减计数时,提供独立事件的控制

AQ模块是基于事件驱动逻辑。可以认为AQ模块是通过编程选择输入事件然后进行输出动作。其输入事件有:

- CTR = PRD

- CTR = Zero

- CTR = CMPA

- CTR = CMPB

- 软件强制事件

其中,软件强制事件由AQSFRC和AQCSFRC寄存器控制。AQSFRC为软件强制寄存器(Action-Qualifier Software Force Register),AQCSFRC为软件持续强制寄存器(Action-Qualifier Continuous Software Force Register)。

AQ模块可能配置epWM模块输出EPWMxA、EPWMxB执行的动作有:

- 置高

- 置低

- 翻转

- 无动作。通过无动作可以配置对应的事件,但PWM不动作。比如,配置CTR = CMPB为ADC起始事件,但对应的PWM不动作。

其中,EPWMxA和EPWMxB是独立配置的。输出的动作可以配置为任一或者所有事件输入。比如,CTR = CMPA和CTR= CMPB都可以在EPWMxA上配置。

如果,CMPA/CMPB的值超过周期值,那么:

- 如果是增计数模式,那么CMPA/CMPB > TBPRD时,不会触发CAU/CBU事件;

- 如果是减计数模式,那么CMPA/CMPB ≥ TBPRD时,会触发CAD/CBD事件(该事件发生在TBCTR = TBPRD);

关于这个问题有点想不通,为啥减计数的时候,会触发这个事件呢?

PWM配置生效问题

在运行的系统中,一般CMPA/CMPB活动寄存器的值是每个周期由影子寄存器更新的。但是存在一些异常情况。这些情况是当基于更新的值得动作延迟一个周期或者是基于旧值的动作继续生效额外个周期。

3.4 DB模块

DB模块在ePWM的部分如下:

DB模块的主要功能:

- 由EPWMxA通过DB产生适当的信号对(EPWMxA和EPWMxB)

- 信号对可控制为:

- EPWMxA和EPWMxB输出高有效(AH)

- EPWMxA和EPWMxB输出低有效(AL)

- EPWMxA和EPWMxB输出互补高有效(AHC)

- EPWMxA和EPWMxB输出互补低有效(ALC)

- 上升沿死区

- 下降沿死区

- 死区模块被旁路

DB模块的结构如下图:

其中,EPWMxA in和EPWMxB in为AQ模块的输出,DB模块的输入。

半周期时钟

死区模块可以使用半周期,因此有双倍的精度。即,计数的时钟为2 x TBCLK。

极性控制

上升沿延迟和下降沿延迟的输出信号,可以选择是否进行反极性。

死区计算

上升沿及下降沿死区计算公式:

F E D = D B F E D ∗ T T B C L K R E D = D B R E D ∗ T T B C L K FED = DBFED * T_{TBCLK} \\ RED = DBRED * T_{TBCLK} FED=DBFED∗TTBCLKRED=DBRED∗TTBCLK

其中, T T B C L K T_{TBCLK} TTBCLK为TBCLK的周期值;

当半周期时钟使能时,计算公式如下:

F E D = D B F E D ∗ T T B C L K / 2 R E D = D B R E D ∗ T T B C L K / 2 FED = DBFED * T_{TBCLK}/2 \\ RED = DBRED * T_{TBCLK}/2 FED=DBFED∗TTBCLK/2RED=DBRED∗TTBCLK/2

3.5 PC模块

PC模块在ePWM的部分如下:

PC模块的主要功能:

- 设定斩波频率

- 设定第一个脉冲的脉宽

- 设定第二个和之后脉冲的脉宽

- 可被旁路

PC模块操作重点:

简化波形如下:

第一个脉冲宽度设定:

如图所示:

斩波的第一个脉冲宽度可设。第一个脉冲宽度的时间计算如下:

T 1 s t p u l s e = T S Y S C L K O U T ∗ 8 ∗ O S H T W T H T_{1stpulse} = T_{SYSCLKOUT} * 8 * OSHTWTH T1stpulse=TSYSCLKOUT∗8∗OSHTWTH

第二个及之后的斩波的占空比:

可设定占空比从12.5%到87.5%。

3.6 TZ模块

TZ模块在ePWM的部分如下:

TZ模块被连接到6个 T Z n ‾ \overline{TZn} TZn上,其中 T Z 1 ‾ \overline{TZ1} TZ1~ T Z 3 ‾ \overline{TZ3} TZ3连接到GPIO口上, T Z 4 ‾ \overline{TZ4} TZ4是连接到eQEP模块中EQEP1ERR的翻转信号上, T Z 5 ‾ \overline{TZ5} TZ5连接到系统时钟错误逻辑上, T Z 6 ‾ \overline{TZ6} TZ6到CPU的EMUSTOP输出上。这些信号表示故障或者联防条件满足,当故障发生时,ePWM的输出可以配置为对应相应。

TZ模块的主要功能:

- 6个联防输入信号 T Z n ‾ \overline{TZn} TZn可以映射到任何一个ePWM模块;

- 针对错误信号,EPWMxA和EPWMxB输出可以被强制为:

- 高电平

- 低电平

- 高阻抗

- 无动作

- 在短路或过流时,支持one-shot

- 针对限流,支持CBC

- 支持基于COMP模块输出、 T Z 1 ‾ \overline{TZ1} TZ1~ T Z 3 ‾ \overline{TZ3} TZ3信号的数字比较联防

- 每一个错误联防输入和数字比较子模块的DCAEVT1/2 or DCBEVT1/2强制事件都可以被配置为CBC或者OSHOT

- 如何一个错误联防输入都可以产生中断

- 也支持软件强制触发

- 可被旁路

TZ模块控制逻辑如下图:

当 T Z 1 ‾ \overline{TZ1} TZ1~ T Z 6 ‾ \overline{TZ6} TZ6信号变低或者DCAEVT1/2 or DCBEVT1/2强制事件发生都表明联防事件已经发生。每个ePWM模块都可以独立被配置为忽略或者使用错误联防信号或DC事件。具体哪个 T Z ‾ \overline{TZ} TZ信号、DC事件被用于ePWM模块由TZSEL寄存器决定。其中, T Z ‾ \overline{TZ} TZ信号输入,最小三个TBCLK时钟宽度可以触发ePWM模块上的错误条件。少于3个时钟则有可能不能被CBC或OST锁存。

每个 T Z ‾ \overline{TZ} TZ信号输入都可以独立地被配置为CBC或OST事件;DCAEVT1 and DCBEVT1事件可以被配置直接联防ePWM模块或者可以给模块提供一个one-shot联防事件。DCAEVT2and DCBEVT2事件可以被配置直接联防ePWM模块或者可以给模块提供一个cycle-by-cycle联防事件。

因此,可以使得PWMxA动作的有TZA、DCAEVT1 、DCAEVT2。其中,TZA又可以是one-shot,也可以是CBC。这里TZA如果是通过DC的事件触发,只能是DCAEVT1 、DCAEVT2,而不能是DCBEVT1 、DCBEVT2。

因此,可以使得PWMxB动作的有TZB、DCBEVT1 、DCBEVT2。其中,TZB又可以是one-shot,也可以是CBC。这里TZB如果是通过DC的事件触发,只能是DCBEVT1 、DCBEVT2,而不能是DCAEVT1 、DCAEVT2。

所以,COMP的输出封波,即可以让COMP的输出触发DCAEVT1事件,DCAEVT1事件直接封波;还可以让COMP的输出触发DCAEVT1事件,DCAEVT1事件配置为One-shot事件,One-shot事件封波。区别在于事件锁存。

以下分别针对CBC、OSHOT及DC事件做说明:

1.CBC

当一个cycle-by-cycle联防事件发生时,EPWMxA/EPWMxB输出将按照TZCTL[TZA]和 TZCTL[TZB]位中规定的动作进行动作。此时事件发生时,如果使能了对应的中断(TZEINT 寄存器和PIE外设),那么cycle-by-cycle联防中断位((TZFLG[CBC])将被置位。

如果CBC中断通过TZEINT 寄存器被使能,并且DCAEVT2或 DCBEVT2通过 TZSEL寄存器被选择为CBC联防源,那就没必要使能在TZEINT寄存器中也使能DCAEVT2或 DCBEVT2中断。这是因为DC事件触发中断是通过CBC机制的。

当触发事件不再出现,当ePWM模块TBCTR = 0x0000时,输入上指定条件被自动清除。因此,在CBC这种模式下,每个PWM周期触发事件都被清除。但一直到手动通过给TZCLR(CBC)写入来清除之前,TZFLG[CBC]位会持续被置位。清除之后,cycle-by-cycle触发事件再出现,TZFLG[CBC]还是会被置位。

2.One-shot(OSHT)

当one-shot 触发事件发生,EPWMxA/EPWMxB输出将按照TZCTL[TZA]和 TZCTL[TZB]位中规定的动作进行动作。此时,one-shot触发事件标志位(TZFLG[OST])被置位。并且事件发生时,当TZEINT寄存器和PIE外设使能时,产生一个EPWMx_TZINT中断。one-shot联防条件只能通过给TZCLR[OST]位手动写入来清除。

如果one-shot中断通过TZEINT寄存器被使能,并且DCAEVT1或 DCBEVT1通过TZSEL寄存器被选择为OSHT联防源,那么就没有必须在TZEINT寄存器中使能DCAEVT1或 DCBEVT1中断。这是因为DC事件触发中断是通过OSHT机制。

3.Digital Compare Events (DCAEVT1/2 and DCBEVT1/2):

通过TZDCSEL寄存器可以选择DCAH/DCAL和 DCBH/DCBL信号的组合。基于这个信号组合可以产生一个数字比较事件(DCAEVT1/2 or DCBEVT1/2 事件)。这些DCAH/DCAL和 DCBH/DCBL信号的源信号(输入信号)可以是通过DCTRIPSEL选择。这些源信号(DCAH/DCAL和 DCBH/DCBL的输入信号)可以是任一个TZ输入引脚,也可以是COMP的输出信号。

当DC事件发生,EPWMxA/EPWMxB输出将按照TZCTL[DCAEVT1/2]和 TZCTL[DCBEVT1/2]位中规定的动作进行动作。此时,对应的DC联防事件标志(TZFLG[DCAEVT1/2] /TZFLG[DCBEVT1/2])被置位。并且事件发生时,如果TZEINT寄存器和PIE外设使能时,将会产生一个EPWMx_TZINT中断。

**当DC联防事件不在出现时,引脚上的特定条件将被自动清除。**但一直到手动给TZCLR[DCAEVT1/2] 或 TZCLR[DCBEVT1/2]为写入来清除,TZFLG[DCAEVT1/2] 或 TZFLG[DCBEVT1/2]标志位会一直被置位。清除之后,如果DC联防事件再出现,对应位还是会被置位。

其中,CBC用于电流逐周期限幅,OSHOT为单次锁死。这里的原因是CBC锁存的清除是TCR = 0 ,而OSHOT的清除必须通过软件清除。

而对于DC事件,其DC事件没有锁存功能,因此当DC事件的条件消失,那么DC事件将会消失,但是对应标志位和CBC及OSHOT是一样的,不会直接消失,而是需要手动清除。

3.7 ET模块

ET模块的主要功能有:

-

通过TB、CC、DC各子模块产生事件输入

-

使用TB方向信息产生相应的事件

-

使用预定标逻辑发出中断请求或ADC转换起始信号

每个事件

每两个事件

每三个事件

-

通过事件计数器和标志提高事件产生可视化

-

允许软件强制中断和ADC起始转换

ET操作

每个ePWM模块都有一个中断请求线和两个ADC起始转换信号。所有的ePWM模块的ADC起始转换信号都连接到ADC独立的触发输入上,因此多个模块都可以通过ADC触发输入开始ADC转换。

ET模块实时监控事件的产生,检测到事件之后可以配置多次事件后动作。

3.8 DC模块

DC模块在ePWM的部分如下:

DC子模块的比较信号延伸到ePWM模块去直接产生ePWM事件或动作。该事件或动作可以反馈到ET、TZ、TB模块。此外,针对DC事件信号支持滤除。

DC模块主要功能:

- COMP模块输出和 T Z 1 ‾ \overline{TZ1} TZ1、 T Z 2 ‾ \overline{TZ2} TZ2、 T Z 3 ‾ \overline{TZ3} TZ3输入产生数字比较A的高低信号(DCAH,DCAL)和数字比较B的高低信号(DCBH,DCBL)

- DCAH/L 和 DCBH/L信号触发事件,可以选择滤除或不滤除,然后反馈到TZ、ET、TB模块

- 产生一个TZ中断

- 产生一个ADC转换起始信号

- 强制一个事件

- 对于同步到ePWM模块的TBCTR,产生一个同步事件

- 事件信号滤除

DC模块的操作

通过DCTRIPSEL位,可以选择COMP模块输出和 T Z 1 ‾ \overline{TZ1} TZ1、 T Z 2 ‾ \overline{TZ2} TZ2、 T Z 3 ‾ \overline{TZ3} TZ3输入产生数字比较A的高低信号(DCAH,DCAL)和数字比较B的高低信号(DCBH,DCBL)。

通过TZDCSEL寄存器选择 DCAH/L 和 DCBH/L 信号,用于产生DCAEVT1/2 和 DCBEVT1/2事件。

当 T Z ‾ \overline{TZ} TZ信号作为DCEVT触发功能时,可以将 T Z ‾ \overline{TZ} TZ信号作为一个普通的输入信号,并且 T Z ‾ \overline{TZ} TZ信号可以被配置为高输入有效和低输入有效。EPWM输出为异步触发。

经过滤除或不滤除的DCAEVT1/2 和 DCBEVT1/2事件信号可以产生一个强制给TZ模块,可以产生一个TZ中断,可以产生一个ADC的SOC,或者可以产生一个PWM的同步信号。以下依次介绍:

强制信号:

DCAEVT1/2强制信号通过配置TZCTL[DCAEVT1] 或 TZCTL[DCAEVT2]产生一个强制TZ条件,这个条件可以直接影响EPWMxA的引脚。如果DCAEVT1/2信号源通过TZSEL寄存器选择为one-shot或cycle-by-cycle输入,DCBEVT1/2.force信号可以通过TZCTL[TZA]配置影响联防动作。DCBEVT1/2.force信号性能相似,只是该信号影响的是EPWMxB输出引脚。

TZCTL寄存器上影响动作的有:TZA、TZB、DCAEVT1/2、DCBEVT1/2。当同时来临时,其具有优先级。其优先级如下:

Output EPWMxA: TZA (highest) -> DCAEVT1 -> DCAEVT2 (lowest)

Output EPWMxB: TZB (highest) -> DCBEVT1 -> DCBEVT2 (lowest)

TZ中断:

一旦DCAEVT1、DCAEVT2、DCBEVT1、DCBEVT2中任一事件触发,并且TZEINT寄存器对应中断使能位使能,那么都会触发到EPWMxTZINT。清除时,置位TZCLR寄存器中对应的位去清除。

ADC的SOC信号:

DCAEVT1.soc 信号给到ET模块,可以作为ET模块的事件输入用于产生ADC的起始信号SOCA; DCBEVT1.soc 信号给到ET模块,可以作为ET模块的事件输入用于产生ADC的起始信号SOCB;

同步信号:

DCAEVT1.sync 和 DCBEVT1.sync事件与EPWMxSYNCI输入信号或,用于给TB计数器产生同步脉冲。

各输入信号和输出信号之间的连接如下:

从四个事件的连接来看,其中DCAEVT1和DCAEVT2产生DCAEVTx.force和DCAEVTx.inter;

DCAEVT2和DCBEVT2不产生SOC和同步信号。

事件滤除

DCAEVT1/2和DCBEVT1/2事件可以实现滤除。事件滤除是通过事件滤除逻辑,在一个特定时间内选择性的消除事件,来消除事件干扰的。

事件滤除在以下工况是很有用的:

比较器输出用于触发DCAEVT1/2和DCBEVT1/2事件,消除逻辑可用于滤除联防PWM输出之前、中断产生之前、ADC起始转换之前的,可能的干扰。事件滤除还可以捕获联防事件的TBCTR的值。

事件滤除的输入是DCAEVT1, DCAEVT2, DCBEVT1, DCBEVT2事件。当消除窗口使能时,消除逻辑可以滤除信号上出现的事件。消除窗口可通过配置与CTR = PRD或CTR = 0对齐。可以程序写入TBCLK计数的偏置数,该值决定在CTR = PRD或CTR = 0之后多久开启消除窗。

消除窗的持续时间,是由应用着写入DCFWINDOW寄存器的。消除窗期间,所有的事件都会被忽略。在开始之前和消除窗结束之后,事件可以象之前一样产生SOC、同步、中断和强制信号。

其时序图如下:

4 高精度PWM

HRPWM(High Resolution Pulse Width Modulator)模块可以拓展传统PWM的时间精度。

HRPWM的主要特征为:

- 拓展时间精度能力;

- 用于占空比和移相控制方式;

- 使用CMPA/CMPB的拓展来得到更好的时间粒子控制和边缘位置控制;

- 独立使用PWM的A信号路径,比如EPWMxA输出;

- 自检诊断软件模式用于检测是否微边沿定位(MEP)逻辑是最优运行;

- 通过交换PWM A和B的通道来使能PWM输出B的高精度;

- 通过翻转A信号输出,使能高精度输出B信号;

- 使能PWMxA输出的高精度周期控制(Type1的PWM模块)

HRPWM和PWM精度对比

传统生成PWM的有效分辨率是PWM周期和系统时钟频率的函数。

F28033主频为60M,那么100K的PWM精度为:

P W M _ r e s o l u t i o n = F P W M / F S Y S C L K O U T ∗ 100 % = 100 K / 60 M = 0.1667 % P W M _ r e s o l u t i o n = log 2 ( T P W M / T S Y S C L K O U T ) = 9.2 PWM\_resolution=F_{PWM}/F_{SYSCLKOUT}*100\% = 100K/60M = 0.1667\% \\ PWM\_resolution=\log_{2}{(T_{PWM}/T_{SYSCLKOUT})} = 9.2 PWM_resolution=FPWM/FSYSCLKOUT∗100%=100K/60M=0.1667%PWM_resolution=log2(TPWM/TSYSCLKOUT)=9.2

即,设定100k周期的PWM,那么可能生成的PWM的精度为100.167kHz。计算如下:

设定的100kHz,那么周期值为600,则实际的可能是599计算的值,那么60M/601 = 100.167KHz。

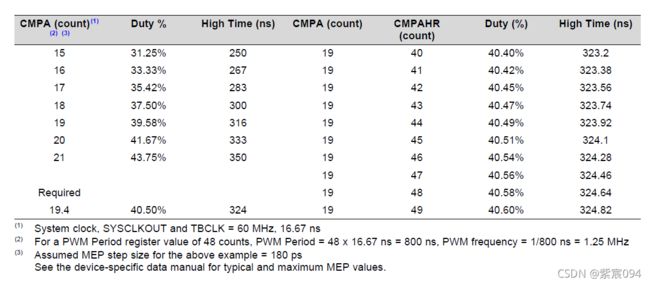

如果在一些需要高精度的场合,那么就可以使用HRPWM。下表为使用HRPWM和传统PWM精度的对比,对了方便,这里MEP的步长为180ps。具体数据如下:

虽然每个应用均有差别,但是典型的低频PWM(低于250kHz)操作一般不需要HRPWM。HRPEM在高频中最有用,比如:

- 单相buck,boost和反激;

- 多相buck,boost和反激;

- 移相全桥;

- Direct modulation of D-Class power amplifiers

HRPWM操作

HRPEM是基于微边沿定位(MEP)技术进行的。MEP逻辑可以通过细分传统PWM中一个粗略的系统时钟来很好的定位一个边沿。时间步进精度近似150ps。HRPEM还有软件自检诊断模式来检测是否MEP逻辑运行在最优。

上图给出了一个粗略的系统时钟和MEP的边沿位置。具体的边沿位置是由比较A拓展寄存器(CMPAHR)中的8bit控制的。

控制HRPWM性能

HRPWM的MEP是由三个拓展寄存器控制的。这些HEPWM寄存器和16位的TBPHS、TBPRD和CMPA相连用于控制PWM操作。

镜像寄存器都有一个"M"的后缀(比如 CPMA镜像 = CMPAM)。图中镜像的镜像寄存器都可以在不同内存地址被写入。读取高精度镜像寄存器将会导致不可确定的值。

TBPRDHR和TBPRD只在镜像地址可以以32位的值写入。

使用通道A PWM信号路径可以控制HRPWM性能。通过正确配置HRCNFG寄存器,HRPWM也可用于通道B信号路径。

配置HRPWM

一旦PWM已经被配置为传统的PWM,那么就可以在偏移0x20的内存地址通过编程配置HRPWM。寄存器提供如下配置选项:

边沿模式(Edge mode):在上升沿(RE)、下降沿(FE)或者上升下降沿(BE),MEP都可以通过编程提供一个精细的位置控制。FE和RE用于需要占空比控制的拓扑,即CMPA好精度控制;BE用于需要相移的,比如移相全桥拓扑,此时使用TBPHS或者TBPRD高精度控制。

控制模式(Control Mode):CMPAHR(占空比控制)或者TBPHSHR(相移控制)都可以通过程序控制MEP。RE或FE应该被用于CMPAHR寄存器。BE控制被用于TBPHSHR寄存器。当MEP被TBPRDHR寄存器(周期控制)控制时,占空比和相位也还可以通过对应的高精度寄存器控制。

影子模式(Shadow Mode):这种模式下提供和常规PWM模式相同的影子选项(双缓冲)。但这个影子选项只有在操作CMPAHR和TBPRDHR寄存器,并且被选择为和传统CMPA寄存器相同负载选项时才是有效的。如果使用TBPHSHR,该选择无效。

高精度B信号控制(High-Resolution B Signal Control):通过交换A和B输出,ePWM通道的B信号路径可以产生一个高精度输出。或者还可以通过输出高精度ePWM xA信号的翻转信号来输出ePWMxB引脚上的高精度。

自动转换模式(Auto-conversion Mode):该模式只用于连接scale factor优化软件。对于Type1 HRPWM模块,如果自动转换使能,CMPAHR = fraction(PWMduty*PWMperiod)<<8。scale fator优化软件将会在后台代码中计算MEP的scale factor并自动将计算的粗略一步的MEP的值更新到HRMSTEP寄存器中。MEP校准模块将使用HRMSTEP和CMPAHR寄存器中的值,自动计算由占空比小说部分代表的MEP步数适当的值;如果自动转换不使能,CMPAHR寄存器就和Type 0 HRPWM模块一样,并且CMPAHR = (fraction(PWMduty * PWMperiod) * MEP Scale Factor + 0.5)<<8)。在该模式中,所有的这些计算都需要由用户的代码去执行,并且HRMSTEP寄存器被忽略。高精度周期的自动转换和高精度占空比转换是一样的。高精度周期总是使能自动转换。

工作原理

MEP逻辑能够将边缘置于255(8位)离散时间步长之一(参见设备特定数据表,了解典型的MEP步长)。MEP与TBM和CCM寄存器一起工作,以确保最佳应用时间步长,并在宽范围的PWM频率、系统时钟频率和其他操作条件下保持边缘放置精度。

举例说明:

主频为60MHz,PWM的周期为1.25Mhz,占空比为40.5%。

当CMPA的值设置为19时,是接近要求的,但如果是19,那么输出占空比为39.6%。

然而,使用高精度就更近了,具体如下表:

所以,如果使用高精度,那么最终输出的高值时间为CMPA对应的316ns + CMPAHR 44对应的44*0.18 = 7.92ns,一共是323.92ns。是最接近要求的0.405/1.25Mhz = 324ns。

上述是如何利用高精度来提高发波的精度。在应用中,还需要给CPU提供从一个单位(小数)占空比到另一个单位整数(非小数)的内存映射函数。该单位整数被写入[CMPA : CMPAHR]寄存器组合。

为此,首先检查所涉及的缩放或映射步骤。在控制软件中,以单位或百分比表示占空比是很常见的。这样做的优点是可以执行所有需要的数学计算,而不需要考虑最终的绝对占空比,占空比以时钟计数或ns表示。此外,它使代码更易于在运行不同PWM频率的多种变换器之间传输。

为实现映射方案,需要进行两步缩放步骤。具体举例如下:

系统时钟为60MHz,PWM频率为1.25MHz,需要的PWM占空比为0.3

那么PWM周期粗略的步数为:48

MEP步长为180ps,则一个粗略步长里面MEP的步数为:1/60MHz/180ps = 92.59

ScaleFactor值,使CMPAHR保持在1-255和小数舍入常数的范围内(默认值)。

如果frac(PWMDuty * PWMperiod) * MEP_ScaleFactor的小数部分≥0.5,则该舍入常数将CMPAHR值向上舍入1 MEP步长。

第一步:占空比整数值转为CMPA

0.405*48 = 19.44,取整为19

因此,CMPA寄存器的值为19(13h)

第二步:小数值转为CMPAHR寄存器的值

CMPAHR寄存器的值为(frac(PWMDuty*PWMperiod)*MEP_ScaleFactor+0.5) << 8,frac是指小数部分。

(frac(0.405*48)*93+0.5) << 8 = (frac(19.4)*93+0.5) << 8 = (frac(19.4)*93+0.5) << 8 = (0.4 *93 +0.5) << 8 = 37.7 << 8 = 37.7 * 256 = 9651 = 0x25B3

CMPAHR寄存器的低八位将会硬件忽略。

如果自动转换AUTOCONV位(HRCNFG.6)置位,并且MEP_ScaleFactor在HRMSTEP寄存器中,那么CMPAHR寄存器的值就是 frac (PWMDuty*PWMperiod<<8)。剩下的计算在硬件中自定执行,正确的mep缩放信号边缘出现在ePWM通道输出;如果如果自动转换AUTOCONV位(HRCNFG.6)没有设置,那么上述的计算必须有软件进行。

MEP的缩放系数(MEP_ScaleFactor)随着系统时钟和DSP的操作环境在变幻。TI提供了一个缩放系数优化函数(SFO),该函数用于每个HRPWM中的诊断,并且返回给定操作环境下的最优缩放因子。比例因子在有限范围内变化缓慢,因此优化C函数可以在后台循环中非常缓慢地运行。

CMPA和CMPAHR寄存器可以在内存中配置,因此可以32位可以单次写入,比如[CMPA:CMPAHR]。TBPRDM 和 TBPRDHRM镜像寄存器也可以类似配置。

对于精确控制环,环路中每个周期计数,那么就需要汇编版本。这是一个周期优化函数(11个SYSCLKOUT周期),该函数的输入是一个Q15占空比的值,并且写入一个[CMPA:CMPAHR]值。

占空比范围限制

在高精度中,MEP对于100%占空比的PWM周期是不可用的。其可用的变为:

-

在使用高精度周期控制时,在周期起始的3个 SYSCLK

-

当通过HRPCTL寄存器使能高精度周期控制,那么:

在增计数模式时,在周期开始的3个SYSCLK时钟一直到周期结束前的3个SYSCLK周期;

在增减计数,在增时,CTR=0之后的3个SYSCLK周期到CTR=PRD前3个SYSCLK周期,在减时,在CTR= PRD之后的3个周期到CTR = 0的前3个周期。

高精度周期

Type1 ePWM模块支持支持通过THPRDHR(M)寄存器,使用MEP逻辑实现高精度周期控制。

当使能高精度周期控制,那么在增计数模式时,ePWMxB有上下一个TBCLK周期的晃动;在增减计数,ePWMxB有上下两个TBCLK周期的晃动。

其缩放处理和占空比周期应该一样。

举例如下:

系统时钟:60MHz(16.67ns)

需要的PWM频率:175kHz(TBPRD的值为342.857)

MEP的步长为180ps,那么一个粗略的步长,MEP的步数为:

16.67ns/180ps = 92.611,取整为93

MEP_ScaleFactor使得TBPRDHR在1~255的范围内,并且小数取整。

如果不使用高精度:

在增计数模式:

如果TBPRD = 342,那么PWM的频率为174.93kHz(period = (341+1) * T T B C L K T_{TBCLK} TTBCLK)

如果TBPRD = 341,那么PWM的频率为175.44kHz

在增减计数模式:

如果TBPRD = 172,那么PWM的频率为174.42kHz

如果TBPRD = 171,那么PWM的频率为175.44kHz

使用高精度:

在MEP步长为180ps时,步数为93时,

第一步:周期值百分比整数转为TBPRD寄存器的值

60MHz/175kHz = 342.857,取整为342

在增计数模式:

TBPRD = 341 (TBPRD = period value - 1)

在增减计数模式:

TBPRD = 171 (TBPRD =period value / 2 )

第二步:小数值转换TBPRDHR寄存器值

TBPRDHR寄存器的值为:= (frac(PWMperiod) * MEP_ScaleFactor + 0.5)(shift is to move the value as TBPRDHR high byte)

如果自动转换使能,并且HRMSTEP = MEP_ScaleFactor值(93),那么TBPRDHR寄存器的值为:

frac (PWMperiod)<<8 = frac (342.857)<<8 = 0.857 × 256 = 219.392,取整之后为219 = 0xDB

同步信号

当高精度周期模式使能,一个EPWMxSYNC脉冲会给PWM引入上下1~2个周期抖动。因此这个原因,TBCTL[SYNCOSEL]不能设为1(在CTR = 0作为EPWMxSYNCO源),也不能设为2(在CTR = CMPB作为EPWMxSYNCO源)。否则,抖动将在每个带同步脉冲的PWM周期均会发生。

当TBCTL[SYNCOSEL] = 0时(EPWMxSYNCI作为EPWMxSYNCO的源时),在高分辨率周期初始化时只发出一次软件同步脉冲。如果在PWM运行时应用软件同步脉冲,则同步脉冲的时间,PWM输出将出现抖动。

缩放因子优化函数(SFO)

维边缘定位器(MEP)逻辑可以在255个离散时间步数中的其中1个放置边沿。正如之前提到的,步数是基于150ps的,具体的芯片步长是不同的。MEP步长根据最坏情况的工艺参数、操作温度和电压而变化。当变压变小、温度升高,MEP步长变大。如果使用HRPWM的应该TI提供的SFO函数。在使用HRPWM时,这个SFO函数可以在每个SYSCLKOUT周期,动态确定MEP的步数。

在使用Q15占空比(或占空比)给[CMPA:CMPAHR]或者[TBPRD(M):TBPRDHR(M)],有效地利用MEP映射函数,MEP缩放因子(MEP_ScaleFactor)正确的值需要让软件知道。为了完成这个,HRPWM模块构建了用于确定任何操作条件下的最优MEP_ScaleFactor值的自检和诊断能力。TI提供了一个c可调用库,其中包含一个SFO函数,该函数利用这种硬件并确定最优的MEP_ScaleFactor。因此,MEP控制和诊断寄存器保留给TI使用。

SFO()函数运行的最小系统时钟为50MHz。函数返回值为1,表示计算完成;为0表示还在运行;返回2表示出现错误。当出现错误时,HRMSTEP寄存器的值将维持上一个不超过256的值。

在SFO_TI_Build_V6b.lib库中,SFO函数将还会把缩放因子更新到HRMSTEP寄存器中。如果HRCNFG[AUTOCONV]位置位,如果SFO后台运行,应用软件只需要设定CMPAHR = fraction(PWMduty*PWMperiod)<<8 或者 TBPRDHR = fraction (PWMperiod)。而在SFO_TI_Build_V6.lib库,SFO函数不会自动更新HRMSTEP寄存器的值,需要应用软件写入。

该函数是否执行取决于操作环境,大部分一般5~10s左右执行一次,当然更快执行一次也是允许的。

当使用HRPWM特性时,HRPWM逻辑在PWM周期的前3个syclkout周期(如果使用TBPRDHR,则PWM周期的后3个syclkout周期)将不活跃。在此配置中运行应用程序时,如果高分辨率周期控制被禁用(HRPCTL[HRPE=0]),并且CMPA寄存器值小于3个周期,那么它的CMPAHR寄存器必须被清除为零。如果启用了高分辨率周期控制(HRPCTL[HRPE=1]),则CMPA寄存器值不能低于3或高于TBPRD-3。这将避免PWM信号上任何意外的转换。

由于SFO_TI_Build_V6.lib库,还需要手动复制,手册上的代码为:

main()

{

int status;

status = SFO_INCOMPLETE;

while (status==SFO_INCOMPLETE)

{

status = SFO();

}

if(status!=SFO_ERROR)

{ // IF SFO() is complete with no errors

EALLOW;

EPwm1Regs.HRMSTEP=MEP_ScaleFactor;

EDIS;

}

}