关于RISC-V安全性的全面综述

目录

- 摘要

- 引言

- RISC-V安全综述

-

- 通用平台的安全要求

- 信任的根源与硬件安全模块

-

- OTP管理模块

- 安全内存

- 对称加密(如AES)引擎

- 不对称加密[131](例如,公钥RSA)引擎

- HASH/HAMC引擎

- 随机数/位生成(例如TRNG[136])引擎

- Trusted Boot Services

- RISC-V体系结构安全性的构建块

-

- RISC-V体系结构堆栈和特权模式

- 物理内存保护(PMP)

- 加密指令集

- 指令管道

- 硬件安全

-

- 硬件和物理安全

-

- RTL错误

- 硬件特洛伊木马

- 逻辑锁定攻击

- 电磁故障注入

- 隐蔽通道

- 物理访问攻击

- 硬件辅助安全单元

-

- 程序混淆器和Churn单元

- 内存保护

- 加密引擎

- 内存保护

-

- 标记内存

- 内存隔离,加密和身份验证

- ISA安全扩展

-

- 加密算法

- 侧信道攻击防御

- SMPC和CFI

- 降低攻击面

- 密码原语

-

- 轻量级密码

- 对称和非对称加密

- SIKE后量子密码

- TRNG

- DICE

- 防止侧信道攻击

-

- 分支预测漏洞

- 电源和电磁分析攻击

- 定时攻击

- 堆芯内部侧通道

- 基于虚拟样机的侧通道检测

- 结论和未来工作

标题:A Survey on RISC-V Security: Hardware and Architecture

作者:Tao Lu

发布:arXiv: Cryptography and Security

时间:Jul 2021

摘要

物联网(IoT)是一项持续的技术革命。嵌入式处理器是智能物联网设备的处理引擎。几十年来,这些处理器主要基于 Arm 指令集架构 (ISA)。近年来,免费开放RISC-V ISA标准引起了工业界和学术界的关注,成为主流。许多公司已经拥有或正在设计RISC-V处理器。许多重要的操作系统和主要工具链支持RISC-V。数据安全和隐私保护是所有物联网设备面临的共同挑战。为了处理可预见的安全威胁,RISC-V社区正在研究旨在实现信任根 (RoT) 的安全解决方案,并确保 RISC-V 设备上的敏感信息不会被篡改或泄露。许多RISC-V安全研究项目正在进行中,但学术界还没有对RISC-V安全解决方案进行全面调查。RICS-V安全研究的最新技术和未来发展方向仍不清楚。为了填补这一空白,本文对RISC-V安全技术进行了深入的调查。本文总结了RISC-V硬件和体系结构的代表性安全机制。具体来说,我们首先简要介绍RISC-V的背景和发展状态,并将RISC-V机制与最相关的ARM机制进行比较,突出了它们的异同。然后,我们研究了RISC-V在硬件和架构安全主题周围的安全研究。我们的调查涵盖了硬件和物理访问安全、硬件辅助安全单元、ISA安全扩展、内存保护、密码原语和侧通道攻击保护。基于我们的调查,我们预测RISC-V安全未来的研究和发展方向。我们希望我们的研究能够激发 RISC-V 研究人员和开发人员。

引言

指令集架构 (ISA) 是计算机的抽象模型。ISA 指定运行机器代码的行为,而不依赖于特定的机器实现,从而提供相同架构的不同实现之间的程序兼容性。架构规范在概念上定义了硬件和软件之间的基本接口、处理器实现允许的行为以及软件开发和验证的基本假设 [1]。受专有ISA的IP限制以及缺乏64位地址和整体复杂性[2]的启发,RISC-V被开发出来并变得越来越流行。RISC-V 旨在成为一个标准和通用的 ISA,特别是对于三个具有代表性的设备类别:小型物联网设备、个人移动设备和仓库级计算机。

经过多年的技术发展,RISC-V已经成为一种商用ISA。目前,半导体公司正在测试RISC-V,甚至一些产品线正在向RISC-V过渡。从谷歌学者对RISC-V研究工作的统计数据中,我们观察到,在过去十年中,RISC-V相关研究的数量呈指数级增长。RISC-V在计算平台中应用的巨大势头非常明显。从小型物联网微控制器到多核高性能处理器,各种RISC-V设备都已下线。最近,SiFive推出了HiFive1 Rev B和HiFive Unmatch SoC[3],它们已投放市场,用于物联网和桌面应用。SiFive RISC-V核心已经用于SSD控制器[4]。阿里巴巴已经将玄铁-910用于云计算和边缘计算[5]。其他带出和FPGA板包括Microchip PolarFire SoC FPGA Icicle Kit、RISC-V多核加速器SoC BlackParrot[6]、Xilinx多核FPGA系统VC707[7]等。Lee等人[8]实现了一个变形物联网平台,用于在大规模物联网应用场景中按需更换硬件。所有这些后硅实现将RISC-V从概念推向产品。欧洲处理器倡议(EPI)是EuroHPC联合承诺的基石之一,这是一个新的欧盟战略实体,专注于汇集欧盟和国家在HPC上的资源,以在欧洲范围内构建和部署最强大的超级计算机,它正准备采用RISC-V作为其exascale嵌入式HPC平台的核心解决方案[9]。

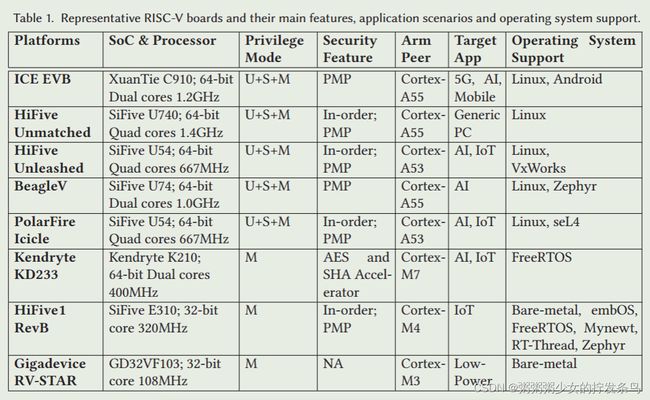

表1列出了现有的硅后RISC-V芯片,主要用于智能设备和物联网(IoT)设备。物联网由数十亿个连接的设备组成,正在改变医疗、运输和公共服务等领域,并继续收集、流程和传输大数据。IDC预测2025年将有41.6亿个连接的物联网设备,生成的数据将超过79ZB[10]。大数据的价值被业界广泛认可。大数据的有效挖掘可以提高企业的竞争优势,为社会功能部门的决策提供了基础。然而,大数据的集合、存储、分析和共享带来了新的信息安全和隐私问题。安全已成为大数据时代的一项重大挑战[11-13]。我们希望 RISC-V 架构的安全机制将在未来的生态系统中发挥重要作用。

随着密码技术的发展,许多安全机制在实践中得到了广泛部署,包括数据保密和完整性保护、身份验证、隐私保护、拒绝服务预防、不可否认性强制执行和数字内容保护。各种安全协议和标准,如TLS、ZRTP、IPSec、IKE和Kerberos,已被用于保护数据服务和应用程序,并缓解平台安全挑战。然而,随着技术的进步,攻击的复杂性也在同时发展,尤其是网络攻击比以往任何时候都更加复杂、虚幻和更有针对性[14]。2019年9月,iPhone黑客被曝光。至少两年来,攻击者利用受感染的网站利用苹果iOS中的14个独立漏洞,并在数千台访问过受恶意软件感染网站的苹果设备上安装间谍软件。攻击者可以访问常规用户数据、密钥链密码和社交媒体内容[15]。最近,公开上市的网络安全公司火眼遭到了一个高度复杂的对手的攻击,该对手窃取了火眼红队的工具,这些工具可能用于对系统进行恶意网络攻击[16]。FireEye被迫发布了数百种对策,以便更广泛的安全社区能够保护自己免受这些工具的攻击。从这起事件中可以清楚地看出,任何组织,无论是否是老练的安全卫士,都无法免受破坏性的网络攻击。根据security Boulevard发布的网络安全报告[17],2018年网络犯罪给受害者造成了约1.5万亿美元的损失。人工智能驱动的攻击[18,19]使情况变得更糟,并使安全防御成为越来越严峻的挑战。除了无数的网络攻击,Meltdown[20]和Spectre[21]的披露还揭示了现代处理器中的硬件漏洞。Spectre和Meltdown攻击证实了将安全性视为跨越硬件和软件边界的系统级设计约束的必要性。ISA漏洞的严重影响引起了业界对架构安全前所未有的关注。侧信道攻击已经广为人知,并吸引了大量的研究。

市场不再只关注产品性能,安全性也是一项苛刻的要求。在应用层,提出了人工智能、物联网和无线传感器网络平台的安全机制[22-33]。在系统级别,安全机制如可信引导[34-39]和可信执行[40-49]被广泛使用。物联网系统通常运行在嵌入式系统的小内核上。这些核心计算能力低,资源有限,难以实现复杂的安全策略。由于硬件执行的高效性,基于硬件的安全机制可以最大限度地降低这些设备的资源成本。Arm TrustZone、Intel SGX和AMD SEV技术通过CPU实现的硬件隔离提供全系统安全解决方案[50]。尽管现有的硬件隔离技术并非无懈可击,例如TrustZone辅助的TEE系统存在安全漏洞[51],但它仍然发挥着重要作用。增强硬件和体系结构的安全性是一项重要要求。平衡平台安全级别和系统性能、硬件和体系结构安全对于平台安全解决方案非常重要。因此,芯片供应商现在正在积极引入硬件安全模块(HSM),并非常小心地避免硬件设计中的安全漏洞。

RISC-V 的开放性能够公开审计架构设计,从而为构建安全平台提供了机会。然而,ISA 的开放性为攻击者提供了场景背后的更多细节,攻击者可以更容易地发现和利用系统安全漏洞。因此,RISC-V 需要使用其开放性来构建可靠的安全机制。RISC-V 安全社区需要了解这种相对较新的架构来执行安全技术创新。RISC-V支持各种特权模式[52]和物理内存保护[52-54]。还实现了可信执行环境[40-49]。其他安全增强措施,包括硬件安全[55-68]、内存已经提出了保护[54,56,57,59,61,69-72]、ISA安全扩展[66,67,73-84]、加密引擎和原语[78-83,85-98]和侧通道预防[99-107]。对最新的RISC-V安全解决方案的系统调查将有助于社区了解当前状态和未来趋势。

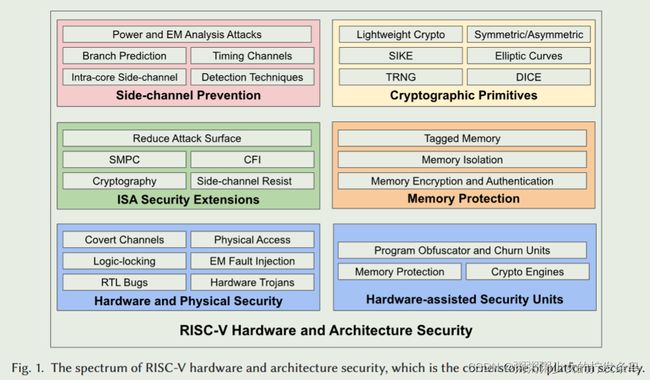

如图 1 所示,本文分为以下主题:硬件和物理安全、硬件辅助安全单元、内存保护、ISA 安全扩展、加密原语以及对侧通道攻击的保护。最后,总结观察结果并讨论了RISC-V安全研究的未来方向。

RISC-V安全综述

在本章中,我们概述了嵌入式平台的安全要求和基础。我们讨论了应用程序和系统安全要求(第2.1节),作为信任根源的硬件安全模块(第2.2节),以及RISC-V安全机制的硬件和架构基础(第2.3节)。

通用平台的安全要求

RISC-V的目标是成为一个通用的指令集体系结构。RISC-V已被用于低功耗物联网[108]、存储控制器[4109]、人工智能机器学习[110-112]、无线传感器网络、数据中心[113]、高性能计算[114]和许多其他应用场景。表1列出了市场上具有代表性的RISC-V板,并总结了处理器型号、安全功能和目标应用场景。从表中我们可以看出,大多数RISC-V SoC仍在低功耗物联网设备中使用。最近,SiFive与英特尔合作发布了Performance P550内核,该内核可以扩展到四核复杂配置,使用的面积与单臂Cortex-A75的面积相似,同时在每个区域提供显著的性能优势[115]。我们可以预期,未来会有越来越多的高性能RISC-V芯片问世。许多软件和工具链已经集成到RISC-V板。Linux和FreeRTOS是两个重要的平台。此外,许多RISC-V SoC可以运行裸机应用程序,这些应用程序不依赖于操作系统。

RISC-V和Arm架构在类似的应用场景中相互竞争。移动互联网是Arm设备的一个重要应用场景。在智能手机和平板电脑等移动设备上运行的应用程序越来越依赖机器学习服务来优化用户体验,例如根据用户行为估计电池寿命、提高图像质量或执行语音识别[25]。这些服务需要与云服务器频繁交互,而此类远程处理数据的高度敏感性导致数十亿用户面临严重的隐私风险。最近,一个包含100多万个指纹和面部识别信息的英国政府承包商数据库被泄露[118],这对用户隐私构成了重大挑战。客户端和服务提供商可以使用加密技术,如同态加密(HE)[119]和安全多方计算(SMPC)[120]来安全地处理加密下的私有输入,或者使用可证明的安全协议来联合计算私有输入上的任何函数。不幸的是,在网络场景中,执行复杂机器学习任务的计算和网络通信瓶颈极大地限制了上述技术的实用性。在前提下处理所有敏感用户数据不仅降低了数据泄露的风险,还提高了数据处理的性能。因此,探索硬件辅助解决方案,直接在移动设备上提供安全和私有的复杂计算服务是一项重要的应用需求。

由于存在通过物理攻击篡改系统可执行文件的风险,可信引导对系统生命周期安全至关重要。构建安全系统的原则之一是从第一个引导程序到最后一个受信任的应用程序之间的所有软件部分生成信任链[36]。这个信任链基于一个永远不会被轻易篡改的信任根(RoT),这被称为安全引导序列。包括笔记本电脑、台式机、智能手机和物联网设备在内的许多安全设备都需要实现安全引导,以确保系统的完整性。安全引导体系结构很复杂,依赖于代码验证单元来确保信任链的完整性。椭圆曲线数字签名算法(ECDSA)和安全哈希算法(SHA)等公钥密码学是安全引导的基本原语,通常在硬件安全模块(HSM)等RoT中实现。我们将在第2.2节中讨论HSM和RoT。

权限管理是体系结构安全的基本机制。如果系统能够控制任务以特权或非特权模式运行,并限制任务对RAM、可执行代码和外围设备等资源的访问,这将使微控制器应用程序更加安全。例如,防止某些代码在RAM中执行可以防止包括缓冲区溢出和恶意代码执行在内的攻击。然而,实现内存保护机制[121]将使应用程序设计更加复杂,因为内存保护需要确定内存区域限制,并向操作系统描述这些限制。此外,内存保护机制需要区分应用程序的操作和限制。将每个任务限制在自己的内存区域的内存保护策略可能是最安全的,但设计和实现也是最复杂的。广泛部署了用于保护敏感代码和数据的可信执行环境(TEE)解决方案。主要的CPU供应商已经推出了他们的TEE,如Arm TrustZone[50]和Intel SGX[122],以启用平台安全区域。TEE有许多应用场景,包括云服务器、手机、ISP、物联网设备、传感器和硬件代币。TEE需要基于硬件安全构建块来实现,包括权限管理、内存保护,甚至可信引导[41,71]。我们将在本节的其余部分概述RISC-V安全构建块。

信任的根源与硬件安全模块

信任根(RoT)[123]是计算系统所有安全操作所依赖的基础。它包含加密功能的密钥,支持可信引导和TEE。RoT对公钥基础设施(PKI)也很重要,PKI用于生成和保护根密钥和证书颁发机构密钥,为软件安全性、不变性和真实性签名代码,并创建用于身份验证的数字证书。由于系统的安全性依赖于用于加密和解密数据的密钥,以及数字签名和签名验证功能,因此RoT是加密系统中始终值得信赖的来源。RoT可以保护数据和应用程序,并帮助在整个生态系统中建立信任链。

RoT必须在设计上是安全的。基于硬件的RoT不会受到恶意软件的攻击,因此它是最安全的。RoT可以是独立的安全模块,也可以是片上系统(SoC)中的安全模块。固定函数RoT是一种状态机,设计用于执行一组特定的操作,例如数据加密、证书验证和密钥管理。通常,这些功能是静态的,只能执行其专门设计的功能。此外,还有一种可编程RoT。它围绕CPU构建,可以执行更复杂的安全功能,可以升级,并可以运行新的加密算法和安全应用程序来对抗不断演变的攻击向量。

由于RoT是攻击者的目标,它通常是孤立执行的,以确保敏感的安全功能在与通用处理器物理分离的专用安全域中执行。在物理分离的RoT中安全隔离安全功能可以降低体系结构复杂性并优化CPU性能。RoT还应具有全面的防篡改和侧通道抵抗能力,防止故障注入和侧通道攻击,并支持分层安全,以提供多层强大的防御。对于基于硬件的信任根[124],加密引擎、密钥和其他敏感安全资源只能在硬件中访问。基于硬件RoT,可以实现软件安全机制以提供额外的灵活性。

RoT解决方案通常包括一个加固的硬件安全模块(HSM),该模块在其安全环境中生成和保护密钥并执行加密功能[125]。HSM是一种可以增强系统安全性的防篡改硬件设备。HSM通常用于具有高数据安全性和信任度的平台,这些平台在系统之外是不可访问的,因此系统可以信任从HSM接收的真实和授权的密钥以及其他加密信息。HSM可以通过各种FIPS认证来证明其安全规范。HSM和RoT的实现是复杂的,涉及硬件和体系结构,包括系统权限级别控制、安全内存访问、密码指令、随机数生成器等。如图2所示,RoT或HSM通常包括以下主要组件:

OTP管理模块

其管理一次性可编程(OTP)存储器[126],该存储器是非易失性的,用于存储密钥和其他安全资产。OTP可以基于半导体反熔丝和MOS栅极氧化物击穿反熔丝来实现。OTP存储器只能编程一次,这是一个不可逆的过程,从而确保了安全性。原始设备制造商(OEM)在芯片出厂前对OTP进行编程,并通过它可以写入重要的信任敏感数据,如UUID、OEM密钥、固件版本以及与信任引导相关的方案、策略和配置参数。OTP以不可变的方式承载RoT信息,以支持整个芯片生命周期的信任链。

安全内存

其具有多个接口和加固的内存保护单元。RoT的RAM将安全资产存储在与系统其他部分隔离的内存区域中。它还可能包括少量ROM。对存储器区域的访问受到MPU[127]或PMP[128]机制的保护,以保证只有具有适当特权级别的实体才能访问受保护的存储器区域。我们将在第4节中讨论RISC-V安全存储器相关研究。

对称加密(如AES)引擎

其用于消息和图像文件的加密和解密,以保证数据机密性并支持安全引导[129]。在20世纪70年代非对称密码学发展之前,对称加密是唯一使用的加密类型。由于更高的性能和更简单的密钥管理,它仍然被更广泛地使用。高级加密标准(AES)是美国国家标准与技术研究所(NIST)于2001年制定的电子数据加密规范[130]。从那时起,AES已成为使用最广泛的对称加密算法。我们将在第5.1节中讨论AES的RISC-V ISA扩展。

不对称加密[131](例如,公钥RSA)引擎

其用于消息加密,使发送者能够将消息与私钥结合起来,在消息上创建短数字签名。该方案具有不必共享对称密钥的优点,同时获得对称密钥密码学的更高数据吞吐量优势。非对称密码系统使用密钥对:一个是其他人可能知道的公钥,另一个是只有所有者知道的私钥。该密钥对的生成取决于基于数学单向函数的加密算法。有效的安全性要求私钥保持私有。可以分发公钥。在这样的系统中,任何人都可以使用目标接收者的公钥来加密消息,但只能使用接收者的私钥来解密加密的消息。公钥加密还可以通过在消息上创建短数字签名来执行可靠的身份验证。公钥算法是现代网络中的基本安全原语密码系统,包括能够保证电子通信和数据存储的机密性、真实性和不可否认性的应用程序和协议。它们是许多互联网标准的基础,例如传输层安全协议。一些公钥算法提供密钥分发和机密性(例如,Diffie-Hellman密钥交换[132]),一些提供数字签名,一些提供两者(例如,PKCS[133])。与对称加密相比,非对称加密比良好的对称加密慢得多,后者在许多方面都太慢了。今天的加密系统(如TLS)同时使用对称加密和非对称加密。非对称加密是安全启动的重要组成部分。

HASH/HAMC引擎

其用于消息哈希,以保证数据的完整性并支持安全引导。哈希函数接受可变长度的数据块作为输入,并生成固定大小的哈希值,该值可用于消息验证、数字签名、单向密码和入侵检测等。基于哈希的消息验证码(HMAC)[134]是一种特定类型的消息验证代码,涉及加密哈希函数和密钥。与任何MAC一样,它可以用于同时验证数据完整性和消息真实性。HASH和HMAC在各种安全应用和互联网协议中发挥着重要作用。此外,散列函数是密钥推导和公钥算法(如PKCS[133]和ECDSA[135])的必要组成部分。

随机数/位生成(例如TRNG[136])引擎

生成用于多种加密算法和协议的随机数或位。许多基于密码学的网络安全算法和协议使用随机值。例如,密钥分发和相互认证方案、会话密钥生成、RSA公钥加密算法的密钥生成以及对称流加密的比特流生成。生成随机比特有两种根本不同的策略。一种策略是基于不可预测的物理过程生成每个比特。这种类型的随机比特生成器(RBG)通常被称为非确定性随机比特生成器。另一种策略是使用算法来确定性地计算比特。这被称为确定性随机比特生成器(DRBG)[137]。DRBG算法根据种子确定的初始值生成比特序列,该初始值由根据随机性源的输出确定的种子确定。用于实例化DRBG的种子必须包含足够的熵以确保随机性。如果种子是保密的,并且算法设计得当,DRBG输出的比特将是不可预测的。我们将分别在第5.1节和第6节中讨论与RBG相关的指令集架构和算法研究。

Trusted Boot Services

其降低了固件rootkit的风险。它从第一阶段的引导ROM开始,该ROM被合成为门。启用安全引导[129138]的设备在启动时将首先验证固件是否经过数字签名,固件将检查引导加载程序的数字签名,以验证其是否未被修改。启用可信引导的设备的引导加载程序在加载内核之前验证其数字签名。内核按顺序验证引导过程中的所有其他组件,包括引导驱动程序和引导文件。如果文件已被修改,引导加载程序将检测到问题并拒绝加载损坏的组件。RoT使网络上的受信任服务器能够验证系统引导过程的完整性。可信引导服务可以在RoT中实现,但服务例程主要与系统运行时有关。在本文中,我们将不详细讨论受信任的引导服务。我们将在下一次对RISC-V系统和应用程序安全性的调查中讨论它们,这将是本文的配套内容。

RISC-V体系结构安全性的构建块

RISC-V体系结构堆栈和特权模式

RISC-V可以支持不同的软件堆栈实现。一个简单的系统可以是在机器模式(M模式)下运行在应用程序执行环境(AEE)上的裸机应用程序。应用程序运行时与特定的应用程序二进制接口(ABI)交互,该接口包括支持的用户级ISA和一组用于与AEE交互的ABI调用。ABI向应用程序隐藏AEE的详细信息,为实现AEE提供了一个抽象层。

RISC-V还可以运行一个可以支持多个应用程序的操作系统。每个应用程序都通过ABI与提供AEE的操作系统进行通信。RISC-V操作系统通过监管器二进制接口(SBI)与监管器执行环境(SEE)接口。SBI包括用户级别以及主管级ISA以及一组SBI函数调用。在所有SEE实现中使用单个SBI允许在任何SEE上运行单个操作系统二进制映像。SEE可以是低端硬件平台上的简单引导加载程序和BIOS风格的IO系统,也可以是高端服务器中的虚拟机,或者是架构模拟环境中主机操作系统上的精简转换层[52]。

如图3所示,RISC-V可以运行一个虚拟机监视器配置,其中一个系统管理程序支持多个操作系统。这是复杂的基础设施即服务场景中的典型部署。每个操作系统通过SBI与提供SEE的系统管理程序进行通信。系统管理程序使用系统管理程序二进制接口(HBI)与系统管理程序执行环境(HEE)通信,以将系统管理程序与硬件平台隔离。

在任何时候,RISC-V硬件线程(hart)都以某种被编码为模式的特权级别运行。目前定义了三个RISCV权限级别:用户(U)模式(级别0)、主管(S)模式(等级1)和机器(M)模式(层次3)[52]。RISC-V特权体系结构中定义了2级H模式。在1.10版本中删除了H模式,以启用S模式中的递归虚拟化支持。为了向后兼容,最新的RISC-V规范保留了H模式。总之:

1、特权级别用于为软件堆栈的不同组件提供差异化保护,为RISC-V平台的安全性奠定了基础。

2、M模式是最高的特权级别。它是RISC-V硬件平台的唯一强制权限级别。以M模式运行的代码通常本质上是值得信赖的,因为它对机器实现具有低级访问权限。M模式可用于管理RISC-V上的安全执行环境。

3、许多RISC-V实现支持U模式,以保护系统的其余部分不受应用程序代码的影响。

4、可以添加S模式,以提供主管级操作系统和SEE之间的隔离。

hart通常以U模式运行应用程序代码,直到一些陷阱(如主管调用或计时器中断)迫使切换到陷阱处理程序,而陷阱处理程序通常以更特权的模式运行。然后hart将执行陷阱处理程序,陷阱处理程序最终将在U模式下的原始陷阱指令时或之后恢复执行。增加特权级别的陷阱称为垂直陷阱,而保持相同特权级别的阱称为水平陷阱。RISC-V特权体系结构提供了陷阱到不同特权级别的灵活路由。每个特权级别都有一组核心的特权ISA扩展,这些扩展具有可选的扩展和变体。M模式支持物理内存保护(PMP)的可选标准扩展[128],这是RISC-V的一个重要安全启用程序。

RISC-V特权级别是与ARM异常级别类似的概念。如图3所示,Armv8-A体系结构允许实现选择是否实现所有异常级别,并为每个实现的异常级别选择允许的执行状态[139]。EL0和EL1是必须达到的异常级别。EL2和EL3是可选的。选择不实施EL3或EL2具有重要意义。EL3是唯一可以更改安全状态的级别。如果实现选择不实现EL3,则PE将无法访问单个安全状态。EL2包含许多虚拟化功能。EL2的任何实现都不能省略这些功能。所有当前的Armv8-A实现都支持所有异常级别[139],因为大多数标准软件都需要这些异常级别。实现还可以选择对每个异常级别有效的执行状态。如果在异常级别允许AArch32,则必须在所有较低的异常级别允许它。例如,如果EL3允许AArch32,则必须在所有较低的Exception级别都允许它。然而,现有的实现也有局限性。例如,Cortex-A32仅支持所有异常级别的AArch32。一些现代实现,如Cortex-A55,实现了所有的异常级别,但只允许EL0使用AArch32,异常级别EL1、EL2和EL3必须使用AArch64。

物理内存保护(PMP)

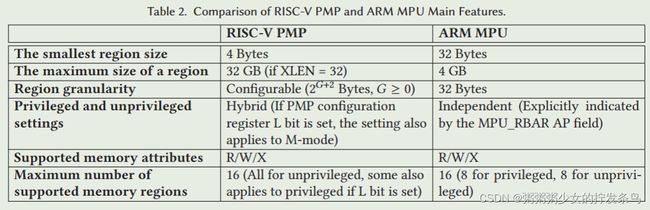

对于安全控制,可选的PMP[52128]单元提供每哈特机器模式控制寄存器,以允许为每个物理存储器区域指定物理存储器访问权限(读取、写入、执行)。PMP值的检查与物理内存属性检查并行进行。实际上,PMP可以向S和U模式授予权限,也可以从默认情况下具有完全权限的M模式撤销权限。PMP违规总是被精确地捕获在处理器处。从功能的角度来看,RISC-V PMP相当于ARM MPU[127],它是一种可编程单元,允许特权软件为单独的内存区域定义内存访问权限。RISC-V PMP和ARM MPU非常相似,但它们的一些关键配置(如区域大小和支持的区域数量)不同。我们比较了表2中RISC-V PMP和ARM MPU的关键特性集。我们将RISC-V PMP的主要特点总结如下:

1、当hart在S或U模式下运行时,PMP检查适用于所有访问。

2、当MPRV位被设置在mstatus寄存器中并且mstatus注册表中的MPP字段包含S或U时,PMP检查被应用于加载和存储。

3、PMP检查应用于虚拟地址转换的页表访问,对于虚拟地址转换,有效特权模式是S。

4、PMP检查可以另外应用于M模式访问,在这种情况下,PMP寄存器本身被锁定,因此,即使是M模式软件也无法在没有系统重置的情况下更改它们。

5、标准PMP编码支持小到四个字节的区域。

6、RISC-V最大支持设置16个PMP区域。

PMP主要用于防止在较低特权级别(如U和S模式)下运行的hart访问特权内存内容。例如,应该防止普通用户hart修改甚至读取共享库的数据。因此,共享库数据所在的存储区域可以设置为仅使用PMP执行。即使hart在M模式下运行,在某些情况下,防止它修改可能导致运行时错误的平台相关配置也是有益的。通过设置PMP配置寄存器的L位,PMP可以将存储器设置应用于M模式以强制执行保护策略,并锁定存储器区域以防止M模式hart更改强制执行的PMP设置。图4展示了PMP对运行时内存保护的影响。

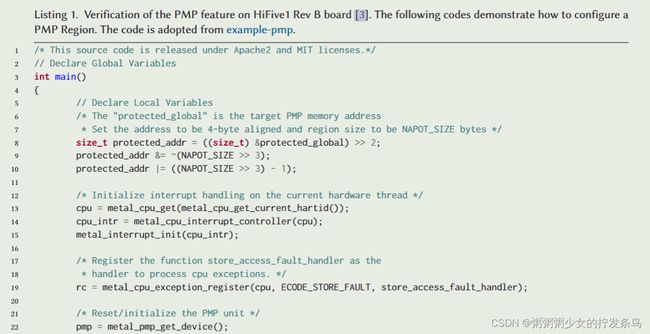

我们在HiFive1 Rev B板上验证了M模式下的RISC-V PMP设置。重新格式化的源代码如清单1所示。线路#38试图将数据写入PMP写禁用目标存储器地址,这触发存储/AMO访问故障(异常代码7)。

加密指令集

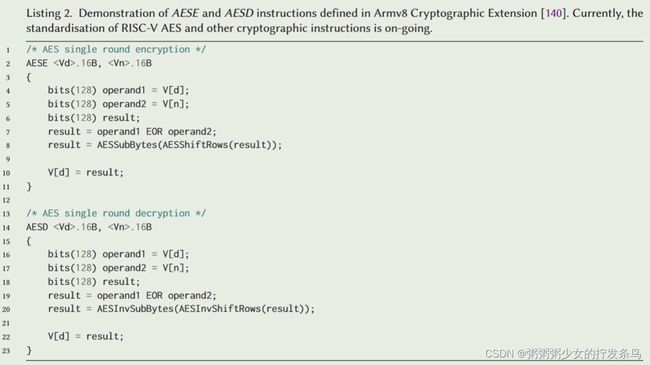

安全高效地执行加密操作是各种计算平台的基本要求。专用指令集扩展(ISE)通常用于实现此目的。密码指令集的实现与基于软件的实现相比具有两个优点。首先,基于CPU硬件的实现可以最大限度地提高密码操作的性能。其次,硬件实现可以隐藏实现细节,减少攻击面。Armv8加密扩展提供了加速AES、SHA、多项式乘法、SM3和SM4[140]的指令。清单2演示了Armv8加密扩展中定义的AESE(AES加密)和AESD(AES解密)指令。这些指令的一次执行可以进行一轮AES加密或解密操作,该操作实际上由多个执行步骤组成。

RISC-V标准密码ISE定义仍在进行中。关于这个主题有一些积极的研究项目。Stoffelen等人[98]提出了RV32I指令集的基于表的AES、位片AES、ChaCha和Keccak-f[1600]置换的第一个优化汇编实现。Marshall等人[82]进一步建议32位和64位RISC-V基本架构使用单独的ISE,与使用T表的纯软件实现相比,AES-128块加密的性能分别提高了4倍和10倍,硬件成本分别为1.1K和8.2K门。一些RISC-V SoC,如PolarFire SoC FPGA,已经采用异构架构来集成基于Arm的协处理器作为密码引擎。我们将在第5.1节中进一步讨论RISC-V密码ISE研究。

指令管道

指令流水线技术将指令划分为由不同处理器组件执行的一系列顺序步骤,并在单个处理器中并行处理不同的指令[141],从而充分利用所有处理器组件。无序执行是大多数高性能处理器中使用的一种模式,用于利用否则会浪费的指令周期。在这种范例中,处理器基于输入数据和执行单元的可用性而不是程序中的原始顺序来执行指令。因此,处理器可以避免在等待前一条指令完成时处于空闲状态,同时可以立即处理可以独立运行的下一条指令。因此,无序执行[142]是许多现代处理器不可或缺的性能特征。当无序执行到达条件分支指令时,其方向取决于尚未完成执行的指令。在这种情况下,处理器可以检查其当前寄存器状态,预测程序将遵循的路径,并沿着该路径推测性地执行指令。如果预测是正确的,那么检查点就没有用处,并且按照程序执行的顺序取消指令。否则,当处理器确定它遵循错误的路径时,它将通过从检查点重新加载其状态来丢弃路径上的所有未决指令,并沿着正确的路径恢复执行,以确保程序逻辑状态的正确性。分支预测器试图在确定性已知之前猜测分支将走哪条路。分支预测器的目的是改进指令管道中的流。在许多现代流水线微处理器体系结构中,分支预测器在实现高性能方面起着至关重要的作用。然而,无序执行和推测性分支预测会导致众所周知的Meltdown[20]和Spectre[21]漏洞。

RISC-V ISA避免过度定义特定的微体系结构风格(例如,微编码、有序、解耦、无序)或实现技术(例如,全定制、ASIC、FPGA)。RISC-V允许在这些风格中的任何一种中进行有效的实现[52]。Rocket Chip[143]是一个开源的片上系统设计生成器,可发出可合成的RTL。它使用Chisel硬件构造语言,为核心、缓存和与集成SoC的互连形成一个复杂的生成器库。Rocket Chip生成通用处理器核心,并提供有序核心生成器(Rocket)和无序核心生成器(BOOM)。Rocket Chip支持以指令集扩展、协处理器或完全独立的新内核的形式集成自定义加速器。Rocket Chip已经下线,并生产了一个能够引导Linux的原型。Gonzalez等人[100]复制了Spectre对BOOM核心的攻击。为了减轻攻击,他们实现了一个小的L0推测缓冲区,用于保存推测负载未命中的重新填充数据,并在负载被解析为未分配时刷新数据。这可以防止错误分配的负载影响缓存的状态,同时仍然允许正确推测的负载尽快将其数据广播到机器的其他部分,以保持性能。我们将在第7节中进一步讨论侧通道预防相关主题。

在本文的其余部分中,我们将按主题讨论RISC-V硬件和体系结构的安全性。对研究论文进行分类很有挑战性,因为有些研究涉及多个主题。例如,当我们讨论指令集扩展时,有关于侧通道预防的相关研究,但防止侧通道攻击本身是一个主要的研究课题,这对研究论文的分类提出了挑战。在这种情况下,我们将在最接近其工作的主题下讨论一项具体研究。

硬件安全

物联网设备等嵌入式设备面临着通过侧通道或故障注入进行物理攻击的挑战。从推测执行的漏洞中吸取教训,计算架构的设计应该考虑安全性,而不仅仅是性能。尽管半导体行业使用各种验证技术来确保片上系统(SoC)的安全性,但攻击正变得越来越复杂。近年来影响主要硬件制造商的一系列实际攻击证明,确保芯片安全极具挑战性。通过增加硬件安全扩展来减少软件TCB仍然是一种技术趋势。基于底层TCB的加密原语或TEE等安全解决方案在未来将继续面临许多挑战。此外,安全架构需要在应用程序的高性能和低功耗之间达成最佳折衷[63]。作为一种新的体系结构,RISC-V社区正在实施各种安全解决方案。RISC-V的开放性和指令集扩展能力为芯片安全解决方案的实现提供了前所未有的创新机会。在本节中,我们总结了在硬件和体系结构层最先进的RISC-V安全研究。我们将现有的硬件安全研究分为两个主题:硬件和物理安全以及硬件辅助安全单元。

硬件和物理安全

硬件漏洞[153]可能是由设计或制造过程中无意的设计错误和恶意植入的硬件特洛伊木马引起的。不正确的设计规范、有缺陷的设计实现或RTL合成中设计的不正确翻译都可能导致设计错误。最近的研究证实,硬件漏洞可以被各种攻击利用,包括物理访问攻击[147148],隐蔽通道[20,21]、故障注入[145]和逻辑锁攻击[152]。除了泄露关键系统或用户信息外,硬件漏洞的一个主要风险是其不可修复性。在tapeout之后,固件和软件更新不会改变芯片的硬件运行时行为,这可能导致产品召回。预防硬件漏洞的一个主要挑战是,当前的行业检测方法无法实现良好的硬件漏洞检测率。因此,探索新的硬件安全和漏洞检测技术是当务之急。图5总结了最新的RISC-V硬件和物理安全研究,并显示了硬件相关漏洞和攻击模型的总体视图。

RTL错误

Dessouky等人[152]组织了一场国际黑客马拉松,以表明当前的硬件安全验证技术从根本上是有限的,无法检测到真实平台中常见的RTL漏洞,这些漏洞可能导致硬件漏洞。具体来说,他们在两个开源RISC-V SoC设计中注入了31个RTL漏洞,以综合不同类型的常见硬件漏洞。这些错误包括不正确的权限提升、地址重叠、对某些系统寄存器的写入权限不正确、加密功能不安全、密钥存储不安全以及硬编码密码。来自世界各地的50多个团队已经使用正式验证、基于断言的模拟、基于软件的测试甚至手动检查方法来检测这些错误数月。业界领先的正式验证技术只检测到15个错误。能够导致秘密泄露的漏洞检测率很低,这表明进一步探索推进硬件安全验证的技术进步极其重要。Sadeghi等人[154]进一步总结了在这些硬件安全竞赛中吸取的教训,他们观察到检测硬件漏洞的主要技术包括模拟驱动的方法、信息流分析、软件驱动的模拟以及使用Lint工具检查RTL代码。他们还设想,模糊硬件接口可能是检测硬件错误的有效方法。

硬件特洛伊木马

硬件特洛伊木马(HT)是导致硬件漏洞的另一个主要安全风险[155]。从理论上讲,恶意工程师和芯片制造商可以修改硬件设计和实现,以包括硬件后门,从而使攻击者能够完全控制系统。硬件木马检测是一种重要的防御机制。针对这些危险木马的防御机制的发展相对滞后。Hepp等人[156]将四个硬件特洛伊木马设计并集成到后量子加密增强型RISC-V微控制器中。该微控制器于2020年9月下线。这些HT的影响是多方面的,从简单的拒绝服务到侧通道漏洞,以及向外部观察员传输敏感信息。对于每个HT,他们使用设计工具或模拟来估计这些木马的可检测性。他们的初步观察是,一些HT很容易被设计工具检测到。然而,一些修改软件控制流程的HT,干扰很小,不容易被检测到。然而,使用这些修改软件控制流的特洛伊木马需要进行秘密修改。这增加了在现实中使用这些木马实现攻击的难度。这项工作为硬件特洛伊木马检测工具提供了现实的测试设备。

Linscott等人[149]提出了一种新的架构,将处理器设计的安全关键部分映射到一次性可编程无LUT结构。通过分析目标模块的HDL,可以自动生成可编程结构。通过让可信方为每个芯片随机选择映射配置,所提出的方案可以防止攻击者知道目标信号的物理位置。此外,它们还提供了一个诱饵选项,用于映射安全关键信号,以检测击中诱饵的硬件木马。使用这种防御方法,任何能够分析整个可配置结构的特洛伊木马都必须使用复杂的逻辑功能,并占用很大的硅面积,这大大增加了被安全工具检测到的可能性。他们在RISC-V BOOM处理器上评估了该解决方案,并证明通过提供将每个关键信号映射到芯片上6个不同位置的能力,所提出的方案可以将攻击成功率降低99%,而开销仅增加27%的面积。

侧信道检测[157158]是发现潜在硬件木马的有效方法。它可以测量实际设计中由于插入或修改特洛伊木马而导致的系统功耗、电磁辐射和延迟传播的任何差异,以发现潜在威胁。然而,这些方法是在诸如AES协处理器之类的简单设计原型上进行评估的。此外,用于这些方法的分析方法受到一些统计指标的限制,例如EM迹线或T检验系数的直接比较。Takahashi等人[150]提出了两种基于机器学习的新检测方法。第一种方法是在原始EM轨迹上应用有监督的机器学习算法对硬件木马进行分类和检测。其检出率接近90%,假阴性率不到5%。第二种方法是基于异常值/新颖性算法。该方法与基于T检验的信号处理技术相结合,具有较好的性能。检测率接近100%,假阳性率不到1%。Takahashi等人对RISC-V通用处理器的方法进行了评估。RISC-V处理器中三个硬件木马的面积大小比分别为0.53%、0.27%和0.1%。虽然插入的木马很小,但新方法可以检测到它们。

现有的硬件木马研究主要集中在逻辑电路中的木马攻击。关于嵌入式内存中的特洛伊木马攻击的研究仍然很少。Hoque等人[159]讨论了一种用于嵌入式SRAM阵列的新型硬件特洛伊木马。他们展示了SRAM中各种类型的特洛伊木马电路,包括电阻短路、桥接和电路节点开路。这些木马可以逃避行业标准的后硅内存测试,并在部署后实现目标数据篡改。它们可以引起各种恶意影响,具有多种激活条件,在功耗、性能和稳定性方面具有较低的开销,并且产生可忽略不计的硅面积开销。Bolata等人[151]提出了一种针对内存中硬件木马的RISC-V微处理器保护架构。该体系结构旨在检测硬件特洛伊木马对系统指令和数据存储器的入侵。目标是检测硬件特洛伊木马,这些木马可以迫使微处理器在未经授权的内存位置运行恶意代码或读取/写入数据。所提出的保护架构依赖于两个基于Bloom Filter的检查器,它们监视从指令存储器中提取的指令以及指令和数据存储器中的访问地址。他们将保护架构应用于RISC-V FPGA微处理器,以运行一组用于案例研究的软件基准。

逻辑锁定攻击

逻辑锁定旨在解决半导体供应链中的IP盗版威胁。这项技术增加了一个密钥门,其输入由密钥驱动,以隐藏IP的内部细节。只有当应用编程的钥匙时,转换才会反转,以实现IP的原始功能。不幸的是,现有的逻辑锁功能不断受到攻击,很难达到预期目标。尽管当前的攻击主要针对组合电路,但这些攻击可以通过扫描链扩展到实际的时序电路。假设扫描输入和扫描输出端口可由攻击者控制和观察。攻击者可以选择性地将输入注入扫描输入端口,并分析来自扫描输出端口的响应,从而在功能上盗用受保护IP模块的功能。需要一个安全的扫描链来防止此类攻击。Potluri等人[146]观察到,扫描输入端口上的触发器锁定会混淆扫描输出端口的功能输出。因此,他们提出了SeqL,它将功能路径与锁定的扫描路径隔离,并锁定触发器输入以实现功能输出损坏。因此,SeqL可以隐藏功能正确的大多数扫描正确密钥,从而最大限度地提高攻击者观察到的解密密钥功能不正确的概率。他们在成熟的RISC-V CPU上验证了所提出的解决方案的有效性,并验证了SeqL可以抵御广泛的攻击,包括SAT、Double DIP、HackTest、SMT、FALL、Shift和Leak以及多周期攻击。

电磁故障注入

电磁故障注入(EMFI)技术是嵌入式设备面临的一个重要安全挑战。Elmore等人[145]通过实验证明,EMFI使320MHz RISC-V处理器能够跳过或错误地处理指令,从而证实了攻击者利用EMFI进行广泛攻击的可能性。此外,在Arm和RISC-V嵌入式处理器上的实验结果表明,在较低的电源电压和较高的时钟频率下,EMFI攻击更有可能成功。他们还观察到,异常代码有助于了解注入故障的细节,这为在许多情况下指令已损坏提供了进一步的证据。目前,针对EMFI攻击的对策仍然不多。

隐蔽通道

秘密渠道是敏感信息泄露的另一个风险。在高级处理器中发现了Meltdown和Spectre隐蔽通道漏洞[20,21],这导致公众对硬件安全高度警惕。这些秘密通道可以在秘密和攻击者之间没有任何明确信息流的情况下泄露秘密数据。人们普遍认为,这些隐蔽通道是基于推测和无序执行的高级处理器架构所固有的,低端处理器不存在此类安全风险。然而,Fadiheh等人[144]表明,隐蔽信道信息泄漏是普遍存在的,它们也可能出现在具有顺序管道的平均复杂度处理器中。他们提出了一种称为唯一程序执行检查(UPEC)的形式化方法,该方法可以系统地检测和定位隐蔽通道漏洞。UPEC采用了对微体系结构水平RTL的正式分析。UPEC将属于计算系统微体系结构逻辑部分的所有状态变量(寄存器、缓冲器、触发器)的集合定义为SoC的微体系结构状态变量。它定义了微体系结构状态变量的子集,这些变量定义了ISA级别的程序执行状态,不包括在程序内存中表示为体系结构状态的程序状态变量。它将受保护位置的内存内容定义为机密数据。如果被验证的系统存在状态soc状态,则UPEC属性失败,因此向下一状态soc状态的转换“取决于任何机密数据”。这里,soc state和soc state是状态变量的向量,仅包括体系结构状态变量。如果检测到任何UPEC属性故障,则设计可能包含隐蔽通道。针对开源RISC-V SoC生成器Rocketchip[160]的不同设计变体,探索了UPEC的有效性。

定时通道[161]也可能泄露敏感信息。由于复杂的快速路径和优化功能,定时信道在现代硬件中很难避免。避免定时信道的一种有前途的方法是设计和验证硬件设计可以在恒定时间内执行的条件。Gleissenthall等人[64]提出了IODINE,这是一种精确的时钟和恒定时间方法,可以消除硬件中的定时通道。IODINE[64]定义了使用其语言解释器VINTER将Verilog代码翻译为中间代码的语法。然后它执行用于定时信道分析的中间语言。对于预定义的输入向量,分析是逐周期进行的。在每个循环中,它检查每个变量的影响集。对于不同的输入向量,预计每个循环中这些向量中任何变量的影响集都是相同的,否则可能存在不同测试向量的执行时间不恒定的情况。鉴于Verilog中描述的硬件电路,包括一组源和汇以及一组规范假设,IODINE允许开发人员自动合成证明,以确保硬件在恒定的时间内执行。换句话说,在给定的使用假设下,从源到汇所花费的时间与操作数、处理器标志和并发计算的干扰无关。通过使用IODINE,加密硬件设计人员可以确保硬件执行时间不依赖于密钥值,因此他们的加密引擎不会泄露密钥。类似地,CPU设计者可以确保程序(如密码算法)以正确的结构在恒定时间内执行。该方法检测到两个真正的错误,一个在FPU中,另一个在RSA加密模块中。这项研究的一个主要贡献是,它提出了一种形式化的方法来以确定性的方式验证硬件设计中定时侧信道的存在。

物理访问攻击

物理访问芯片的攻击者可以直接探测引脚信号以观察敏感信息[162]。为了防止这种攻击,现有技术提出了一种安全处理器来自动加密和检查处理器外部的所有数据的完整性,包括DRAM和非易失性存储器中的数据。尽管安全处理器对内存内容进行加密,但DRAM在内存总线上以明文形式传输内存地址。攻击者可以窥探内存总线并观察访问的物理内存地址,然后收集敏感数据,如加密密钥或用户级程序的信息。为了防止这种信息泄露,有必要使存储器地址轨迹不可区分。Maas等人[147]提出了一种用于有效遗忘计算的新硬件架构,该架构可以确保数据机密性和内存跟踪遗忘性。换句话说,由于应用程序的每次存储器访问都会导致所访问数据的物理存储器地址随机变化,因此数据访问不会在物理存储器上产生固定的地址模式。因此,攻击者无法探测有关所访问的DRAM位置的任何信息。同样为了防止物理访问攻击,Werner等人[148]提出了一种保护RISC-V处理器免受故障注入攻击的方法。他们展示了通过指令流加密和解密来保护控制流,以及通过向比较操作添加冗余并将比较结果与加密的指令流纠缠来保护条件分支。

硬件辅助安全单元

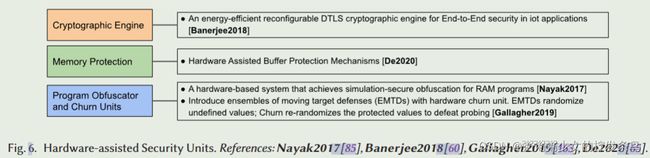

硬件辅助的安全单元试图确保软件无法提供的安全级别。硬件辅助安全机制的基本假设是,硬件比软件更不可能存在可利用的漏洞。硬件功能可以降低软件部分的复杂性,以提高平台性能。因此,该行业提倡全方位的硬件辅助安全方法,包括可信计算、随机数生成、加密加速、恶意软件检测[164]。同时,学术界也提出了许多基于这些工业硬件信任锚的安全解决方案。硬件辅助安全单元可以在许多场景中以不同的形式实现。例如,为了实现物联网应用程序的端到端安全,可以将硬件单元实现为加密引擎。在整体移动目标防御的情况下,它可以作为一个搅乱单元来实现。硬件辅助单元也可以用于内存保护和事务批准。包括TIMBER-V[71]和Keystone[41]在内的RISC-V TEE是基于内存保护机制和可信引导服务创建的。TIMBER-V基于内存保护单元和标记内存机制,我们将在第4.1节中对此进行讨论。Keystone依赖于一个可信的引导服务,该服务类似于Arm TEE,主要与系统运行时有关,本文将不再讨论。我们计划在下一篇关于系统和应用程序的RISC-V安全调查文章中将TEE作为一个主要主题进行讨论。图6总结了我们将在本小节剩余部分讨论的硬件辅助安全单元的研究。

程序混淆器和Churn单元

以纯软件的方式实现通用程序的虚拟黑匣子(VBB)模糊处理是具有挑战性的。Nayak等人[85]提出了HOP,它使用安全硬件来实现RAM程序的模拟安全模糊。HOP只信任硬件处理器。HOP的理论分析考虑了实际设计中使用的所有优化,包括硬件遗忘RAM(ORAM)、硬件暂存区、指令调度技术和上下文切换的使用。他们介绍了HOP的FPGA原型硬件实现。通过各种基准评估HOP的成本是不安全系统的8到76倍。与之前实现模糊处理(未实现)的所有努力相比,HOP的性能提高了三个数量级以上,使模糊处理技术离实现可在实践中部署的目标又近了一大步。

不断混淆攻击者所需的信息是一种有效的反击方法。频繁的混淆会产生较高的系统开销。Gallagher等人[163]提出了Morpheus,这是一种具有硬件搅乱单元的移动目标防御系统,其中每个移动目标防御都使用硬件支持以更低的成本提供更多的随机性。当与混淆一起使用时,Morpheus防御可以提供强大的保护,防止控制流攻击。安全测试和性能研究表明,Morpheus已经实现了对各种控制流攻击的高覆盖保护,包括对高级攻击的保护。此外,长达50毫秒的搅动时间至少比穿透睡眠所需的时间快5000倍。

内存保护

代码注入和代码重用攻击,如缓冲区溢出和面向返回编程(ROP),仍然是RISC-V程序的威胁。De等人[65]为RISC-V提出了两种硬件安全扩展。首先,他们使用了基于物理不可克隆函数(PUF)的随机金丝雀生成技术,这消除了在内存或CPU寄存器中存储敏感金丝雀字的需要,因此更安全、更高效。他们在RISC-V火箭芯片中实现了拟议的Canary引擎。仿真结果表明,对于单个缓冲区保护,平均执行开销为2.2%。当保护扩展到所有缓冲区时,将缓冲区计数增加10倍只会增加1.5倍的开销。其次,作者实现了Fixer,这是一个用于流完整性的专用安全协处理器扩展。FIXER为在后边缘(返回)和前边缘(调用)上运行的程序强制执行细粒度控制流完整性(CFI),而不需要对处理器核心进行任何架构更改。与基于软件的解决方案相比,FIXER以最小的执行时间(1.5%)和面积(2.9%)开销将能耗降低了60%。

加密引擎

数据报传输层安全(DTLS)是端到端物联网通信安全的重要协议。高计算开销使得纯软件DTLS实现对于资源受限的嵌入式设备来说成本太高。Banerjee等人[28,60]演示了DTLS协议的第一个硬件实现。该设计的关键组件是可重构元件场椭圆曲线加密(ECC)加速器,其能效是软件和最新硬件实现的238倍和9倍。DTLS 1.3协议的完整硬件实现比软件节能438倍,代码大小和数据内存占用分别低至8KB和3KB。对DTLS以外的应用程序的基准测试表明,密码加速器和片上低功耗RISC-V处理器的组合可以节省多达两个数量级的能量。他们的测试芯片由65nm CMOS制成。在16MHz和0.8V下,每次握手消耗44.08μJ,加密数据的每个字节消耗0.89 nJ。

软硬件协同设计可以显著提高密码算法的性能。王等人[165]在RISC-V嵌入式处理器上提出了基于哈希的后量子签名方案XMSS的软硬件协同设计。它们为SHA-256参数集和多个硬件加速器的XMSS参考实现提供软件优化,允许根据个人需求平衡区域使用和性能。与纯软件实现相比,通过将硬件加速器集成到RISC-V处理器中,密钥对生成性能可以提高54倍以上。签名生成时间小于10毫秒,验证时间小于6毫秒,比软件快42倍和17倍。他们在英特尔Cyclone V SoC FPGA上测试并测量了循环次数。他们的XMSS加速器和嵌入式RISC-V处理器的集成测试表明,基于哈希的后量子签名实际上可以用于各种嵌入式应用。

内存保护

回顾计算机工程的历史,许多安全漏洞源于两个方面。首先,自20世纪70年代以来,主流处理器体系结构和C/C++语言抽象只提供了基于粗粒度虚拟内存的保护。其次,主流工程方法论遵循设计、开发、测试和调试的过程。这种方法可以满足计算机行业的许多领域,但它们从根本上留下了大量可利用的漏洞,导致了许多严重的系统安全问题[72]。有效的内存保护可以缓解许多系统安全漏洞。如图7所示,至少提出了三种类型的内存保护解决方案:标记内存[56,57,59,61,71,72]、内存隔离[54,69]以及内存加密和身份验证[70]。在本章中,我们将讨论这些主题的相关研究工作。

标记内存

标记的存储器[166167]使存储器指针能够具有能力标签。在存储器访问时,将检查存储器地址的标签,以查看是否存在任何能力冲突。标记内存可以防止经典编程语言中容易发生的典型信息泄漏。例如,ISO C程序可能会因为无意的指针访问而泄露密钥数据。更糟糕的是,编译器不会对此报告任何警告。有了标记内存(如Cheri C语言扩展[168]中的实现),这种错误就不会发生,因为功能检查机制会阻止不安全的内存访问。内存保护功能在一些新兴的编程语言中也得到了支持,如RUST,它因其安全功能和效率而越来越受欢迎。标记存储器是RISC-V硬件和体系结构的一个活跃的研究领域。

Song等人[56]通过扩展Rocket RISC-V实现[160]并提供初步的标记内存支持,探索了标记内存的性能。该实现将预定义数量的标记位添加到存储器中的每个64位字。这些标记位与数据字一起通过高速缓存层次结构复制,这意味着L1数据和L2高速缓存行中的每个字都增加了额外的标记位。标签的一致性由现有的缓存一致性机制来维护。添加了两个新指令LTAG和STAG,用于装载和存储标签。标签存储在保留的存储区域中。对存储器字的每次访问也需要对标签的访问,从而导致存储器流量比为2。使用标签高速缓存可以降低内存流量比,并且流量的减少取决于标签高速缓存的大小。将缓存大小从16KB增加到128KB可以将平均内存流量比从1.59降低到1.06。面向数据的攻击[169]操纵非控制数据来改变程序的良性行为,而不会破坏其控制流的完整性。研究表明,即使存在控制流防御机制,这种攻击也会造成重大损害。基于标记内存特征,Liu[61]和Ma[57]等人提出了标记内存支持的数据流完整性机制,以实现细粒度的数据流完好性检查,从而减轻面向数据的攻击。

许多内存漏洞与指针有关[170]。当特定指针访问超出其允许范围的内存区域时,就会发生空间内存攻击。另一方面,临时内存攻击发生在访问分配后释放的内存区域时。标记内存是一种有效的内存指针保护方案。Menon等人[59]提出了称为基本绑定缓存(BnBCache)的片上硬件设计扩展,该扩展通过减少内存访问总数来优化胖指针性能。它假设存储器中的每个64位字与单个标记位相关联,该单个标记位指示单词是指针或常规数据。标记位由编译器设置,并与存储字一起存储,即使它被加载到寄存器中,寄存器也支持标记位。BnBCache由BnBIndex表和aBnLookUp表组成。BnBIndex表中的条目具有32个通用寄存器的1比1映射。每个BnBIndex条目都有一个指向BnLookUp条目的索引,该条目由4个字段组成:基值(64位)、绑定值(64位组)、ptr_id(64位组)和有效位。提出了带有八条新指令的ISA扩展,以支持标记内存机制。利用标记位、有效位和边界信息,可以阻止空间和时间内存攻击。所提出的解决方案在基于RISC-V ISA的64位基线处理器上实现,在FPGA上产生1914个LUT和2197个触发器的面积开销,而不会带来关键路径延迟[59]。

TIMBER-V[71]是一种新的标记存储器体系结构。结合内存保护机制,它可以灵活高效地隔离代码和数据,在小型嵌入式系统上实现可信执行环境(TEE)。如图8a所示,在正常世界和可信世界中,用户模式(U模式)和主管模式(S模式)下的执行都可以分开。正常世界中的N域支持U模式和S模式之间的传统划分,并允许现有代码在不修改的情况下运行。N域中的存储字,无论在U模式还是S模式下,都用N标签编码。在U模式和S模式下,T域中的存储字分别用TU和TS标签编码。可信用户模式(TU模式)可以用于被称为飞地的隔离执行环境。受信任的监督程序模式(TS模式)允许运行TagRoot信任管理器,用受信任的服务增强不受信任的操作系统。从N域到T域的切换是通过可信的可调用入口点函数实现的,该函数用TC标签编码。总共有4个不同的标签。因此,TIMBER-V对每个32位存储器字使用两位标记。标签只能在相同或较低安全域内更新,但不能用于提升权限,如图8b所示。TS模式(和M模式)可以完全访问所有标签。TU模式只能在N标签和TU标签之间更改标签,以支持用户内存的动态交错。TU模式被阻止操作TC标签,这些标签是为安全入口点保留的。TIMBER-V使用MPU来增强标签隔离功能,以隔离每个进程,同时保持低内存开销。TIMBER-V极大地减少了内存碎片,并提高了不可信内存跨安全边界的动态重用。除了交错堆栈之外,TIMBER-V还可以实现跨不同安全域的新型执行堆栈共享。TIMBER-V与现有代码兼容,支持实时约束。TIMBER-V的概念验证实现已经在RISC-V模拟器上进行了评估。与TIMBER-V类似,CHERI体系结构还提供硬件功能,支持细粒度内存保护和可扩展的安全划分。将CHERI的标记内存功能移植到RISC-V正在进行[72]。

内存隔离,加密和身份验证

现有的内存隔离机制存在可扩展性和性能问题,Kim等人[54]提出了指令级内存隔离(RIMI)来提高性能。RIMI还引入了域的概念,以分离不同内存映射区域中的代码和数据。域内存保护(DMP)机制仅允许域特定指令访问相应域中的指令和数据,以实现不同域访问的指令级内存隔离。每个域还包括物理内存保护(PMP)区域和访问其PMP区域的专用指令。PMP和DMP配置被联合检查以确定指令和数据的访问权限。具体来说,RIMI实现了带有domain_id标签的内存加载和存储指令,以及用于域切换的带有x标签的特殊控制传输指令。例如,lw1表示访问domain1的内存加载指令,sw0表示访问domain0的内存存储指令,jalr只能在同一域之间跳转,jalrx可以在不同域之间跳转。基于Spike模拟器的评估表明,使用RIMI可以有效地实现阴影堆栈和进程隔离。同样在指令级别,Savry等人[70]提出了一个框架,通过实现应用于指令的轻量级屏蔽方案来确保控制流的完整性,该方案基于经过验证的内存加密机制。在系统级别,对于内存隔离,Malenko等人[69]在RTOS中实现了一个设备驱动程序隔离模块,以防止有缺陷的设备驱动程序破坏操作系统和应用程序的状态。

ISA安全扩展

指令集体系结构(ISA)统一了在ISA的不同CPU实现上运行的机器代码的行为。ISA的生命周期跨越了几十年,但应用程序通常发展得很快。为了适应新的应用程序要求,ISA可能需要添加新功能来优化性能、能效或安全性。指令集扩展通常用于实现上述目标,同时保持向后兼容性。众所周知的指令集扩展包括x86 FPU、SSE、AVX、AES、SGX以及Arm SVE、Thumb、Neon、VFPv4和TrustZone安全扩展。如图9所示,RISC-V ISA的相关扩展已被提出,以实现硬件密码功能[77,79–83],减少系统攻击面[76],抵御某些侧信道攻击[66,67,73–75],增强控制流完整性[74],并实现安全的多方计算[84]。我们将在本节中讨论RISC-V ISA安全扩展。

加密算法

加密算法在平台安全机制中无处不在。这些算法是复杂的。存在用于各种加密功能的加密标准和指南,包括分组密码技术、数字签名、哈希函数和密钥管理等。加密函数的性能要求和标准实现使其成为将这些功能集成为ISA扩展并在硬件中实现的适当解决方案。我们已经演示了Armv8密码第2.3.3节中AESE和AESD指令的扩展。RISC-V社区也在为类似的目的扩展指令集。

AES的安全高效实现是大多数计算平台的基本要求。因此,通常实现专用指令集扩展(ISE)以支持高效的AES执行。RISC-V是一种新的ISA,缺乏这种标准化的ISE。Marshall等人[82]调查了AES的最新工业和学术ISE,并评估了五种不同的ISE。与基于软件T表的实现相比,32位和64位架构的ISE可以实现4×和10×AES-128块加密性能的提高,硬件成本分别为1.1K和8.2K门。他们还探索了如何使用RISC-V标准位操作扩展[171]来有效地实现AES-GCM。他们的工作是正在进行的RISC-V密码学扩展标准化过程的一部分。RISC-V加密扩展任务组正在研究标量和熵源指令的加密扩展方案,其中包括比特操作、标量AES、SHA、SM3和SM4加速以及TRNG熵源接口[83]。

与AES GCM算法类似,SNEIK[172]是一个轻量级的、基于排列的加密基元代码库,可以执行加密哈希、使用相关数据进行身份验证加密以及其他任务。该设计旨在满足所有对称密码需求,包括伪随机数生成和密钥推导等任务。Saarinen等人[77]在RISC-V(RV32I)上评估了SNEIK,并表明SNEIKEN128可以以54.8指令/字节的速度进行身份验证加密,这与AES-128在可比Arm平台上的性能大致匹配。SNEIKHA256在RV32I上实现了98.6指令/字节。RV32I基本指令集缺少旋转指令,这导致吞吐量低于Armv7。他们观察到SNEIK排列的结构非常适合ISA扩展优化。RV32I扩展对FPGA资源利用率的影响只有258个LUT/65片,但它将SNEIK排列速度提高了7倍。在Artix-7 FPGA硬件上进行的测试表明,具有ISA扩展的RISC-V“Crimson Puppy”SoC可以以12.4个周期/字节的速度执行SNEIKEN128操作,以17.3个周期/比特的速度执行SNEIKHA256操作,表明一个简单的RISC-V指令集扩展可以实现5倍的加速。

Tehrani等人[7879]提供了用于轻量级加密算法的特定处理器指令的详细架构和实现。这些指令以32位RISC-V ISA为目标,并允许加速几种常用的轻量级块密码。他们使用基于插件的VexRiscv处理器架构在Artix-7 FPGA板上实现指令扩展。他们演示了这些扩展指令的硬件资源使用情况。对于一个具有代表性的轻量级分组密码,他们将该系统的性能与ISA扩展和基本系统进行了比较。结果表明,在合理的硬件成本下,指令扩展可以将轻量级加密算法加速33到138倍。我们将在第6节中进一步讨论轻量级密码算法。

比特操作是处理比单词短的比特的行为。密码算法需要大量的位运算,因此位运算的支持对密码算法的性能有着重大影响。Koppelmann等人[80]提出了位操作指令的RISC-V扩展。具体来说,他们用十位操作指令扩展了RISC-V ISA:奇偶校验、字节交换、右/左旋转、popcount、位反转、计数前导/尾随零以及并行聚集/分散。这些BMI实现了与当前x86 BMI相同的功能,同时所需的代码字节减少了13.5%。为了证明其效率,他们使用13个基准测试对扩展进行了评估,新指令显示出良好的加速性。Wolf等人[171]在RISC-V BitManip任务组中积极研究比特操作指令扩展。根据RISC-V Bitmanip扩展文件0.94-draft[171]版本,他们为32位和64位ISAs提出了100多条比特操作指令,包括比特操作、比特排列、比特字段位置、比特压缩/解压缩等。

量子计算的发展以及Shor算法对我们当前IT安全的破坏性影响,催生了对防止量子计算攻击的加密系统的积极研究。这一研究领域被称为后量子密码学(PQC)。PQC研究的一个重要方面是PQC算法的有效和安全实现。当前的密码算法需要对数百到数千比特的数据进行有效的算术运算,而许多PQC方案对小于20比特的数据执行有限域运算。Alkim等人[81]以基于晶格的密钥封装机制Kyber和NewHope为例,研究了为ISA扩展提供有限现场操作支持对PQC方案的性能。他们在VexRiscv核心上创建了所提供指令的原型实现,并在两个不同的FPGA平台上评估了设计。结果表明,与基本软件实现相比,多项式运算的速度提高了85%。自定义指令可以取代通用乘法器以实现非常紧凑的实现。

故障攻击和功率分析威胁着密码方案的实现。屏蔽功率分析和基于冗余的方法是针对这类攻击最常用的对策。考虑到这些攻击,NIST最近要求提交文件,说明以低成本增加针对这些攻击的对策的可能性。Steinger等人[94]提出了Ascon-p的指令扩展,它使用与处理器寄存器文件的紧密集成,以相对较低的成本显著加速各种对称加密计算。作为概念验证,他们将指令扩展集成到32位RI5CY内核中。他们评估了各种硬件指标,并表明加速器可以用大约4.7kGE实现,换句话说,大约是专用协处理器设计面积的一半。考虑到Ascon-p的内置加速,他们创建了Ascon/Iap模型的汇编版本,该模型利用指令扩展,并为身份验证加密、哈希和伪随机数生成提供基准。基于基准测试,与纯软件实现相比,Ascon-p的指令扩展实现了50到80的加速。

侧信道攻击防御

正如我们在第3.1节中所讨论的,防止微体系结构侧通道攻击是当今硬件安全领域最紧迫的挑战之一。Meltdown[20]和Spectre[21]属于这种类型的攻击。为了防止侧通道攻击,基于硬件的技术侧重于重新设计缓存和完全修改处理器架构,以改进跨处理器信息流跟踪。基于软件的方法建议清除所有核心状态,包括专用缓存、转换备份缓冲区、分支预测单元等。基于软件的方式在很大程度上依赖于刷新机制。尽管在核心级别(1级内)刷新或清除多个易受攻击硬件组件的持久状态对于在整个系统中创建良好和完整的时间隔离至关重要,但研究表明,现有的ISA刷新指令在功能上不完整,在性能和电源效率方面效率低下。

已经有相关的工作试图通过无意地写入程序数据来防止侧信道信息泄漏。在这个模型中,程序编写需要避免敏感数据访问在共享资源上留下痕迹。尽管最近做出了努力,但在现代计算机上运行数据遗忘程序的安全性和性能仍然值得怀疑。首先,编写一个数据遗忘程序假设ISA中的某些指令不会泄露信息,但ISA和硬件没有提供这样的保证。其次,编写程序以避免依赖数据的行为将不可避免地产生严重的性能开销。有人提出利用ISA扩展来防止侧信道攻击[66,67,73–75]。在本节中,我们详细讨论了通过RISC-V指令扩展防止侧信道攻击的相关工作。

Yu等人[75]为RISC-V提出了一种数据遗忘ISA扩展(OISA)。在安全性方面,所提出的ISA设计可以阻断侧信道。就性能而言,OISA支持有效的内存遗忘计算,并具有在常见情况下(如无序推测执行和其他现代硬件优化)可以保持启用的安全功能。他们基于RISC-V无序、推测性的BOOM处理器,实现了一个完整的硬件原型。通过对一台抽象BOOM风格的机器的形式化分析,他们证明了OISA可以实现其安全设计目标。他们评估了硬件机制的区域开销,并提供了性能实验,以展示OISA如何改进各种现有的数据遗忘代码,包括恒定时间密码学和内存遗忘数据结构,同时提高其安全性和可移植性。标签站是OISA的核心组件。如图10所示,标签站在数据流经管道时检查和跟踪公共/机密标签,并在发生违规行为时发出#LV信号。结果标签是根据操作数标签计算的,它与结果一起传播,并伴随着结果的整个生命周期。

我们在第3.1节中讨论了定时通道。ISA扩展也是防止定时通道的一种潜在方式。李等人[73]创建了一个专门的冲洗指令,以提高堆芯级临时隔离的效率,从而降低潜在定时通道的可能性。他们首先提出了一种单指令多刷新(SIMF)方案,该方案将刷新操作集成在一条指令中,以清除核心级状态。SIMF的主要优点是:1)它大大减少了专用于刷新的动态指令计数(从而具有周期计数和指令获取能力);2) 它需要对现有硬件进行最小限度的扩展(向ISA添加指令);3) 当SIMF未使用时,在显式屏障指令的情况下,刷新操作序列在指令中隐式执行;4) 它为编程带来了好处,包括原子性和简单性。他们在开源标量有序RISC-V处理器中对SIMF进行了原型化。他们用另一条名为FLUSHX的指令扩展了RISC-V ISA,该指令刷新核心级状态,包括L1/L2 TLB、L1缓存和分支预测单元(BTB、RAS、BHT)。Wistoff等人[66]针对类似的定时信道问题提出了类似的解决方案。具体来说,他们提出了一种新的RISC-V围栏指令,该指令带有参数,使操作系统能够控制状态刷新。评估表明,该方案完全消除了时序通道,包括L1数据和指令缓存通道、TLB、分支目标缓冲区(BTB)和分支历史表(BHT)通道。

SMPC和CFI

安全多方计算(SMPC)的目标是为各方创建方法,以在其输入上联合计算函数,同时保持这些输入私有[120]。传统上,密码学是关于隐藏内容的,而这种新型的计算和协议是关于隐藏关于数据的部分信息,同时使用来自多个来源的数据进行计算并正确生成输出。通过定制RISC-V ISA,Matsuoka等人[84]提出了虚拟安全平台(VSP),这是一个全面的平台,可以为完整的两党安全计算卸载(SCO)解决方案提供一套完整的工具。VSP包括同态加密库的开源设计和实现、处理器体系结构、自定义ISA和编译器环境。VSP基于著名的Torus全同态加密(TFHE)方案,允许任何用户使用任何C程序以SCO模式执行其代码。

控制流完整性(CFI)[173]的目标是防止恶意软件攻击重定向程序的控制流。我们在第3.2节中讨论了硬件辅助安全单元以实现CFI。CFI也可以通过ISA扩展强制执行。Escouteloup等人[74]讨论了ISA的变化,以加强CFI并确保微观结构状态的隔离。他们在ISA设计中提出了一些安全建议,例如将帧指针等某些寄存器标记为机密寄存器以禁用机密寄存器上的分支,仅在指令的时序不依赖于数据时才授权指令,禁止前向间接跳转并禁止所有微体系结构管理指令,尤其是缓存管理,并且必须通过硬件安全上下文(HSC)指令提供微体系结构安全保证。

降低攻击面

系统的攻击面被定义为系统在方法、数据和通道三个抽象维度上的可攻击性[174]。直观地说,攻击面越大,系统就越有可能受到攻击,因此安全性就越低。能力硬件增强RISC指令(CHERI)[76]扩展了指令集架构(ISA)具有新的基于功能的基元,从而提高了软件在安全性方面的稳健性。CHERI模型遵循最小权限原则,通过最小化运行软件可以访问的权限来实现更高的安全性。CHERI坚持的另一个指导原则是有意使用原则,即当一个软件可以使用许多特权时,应该明确规定特权的使用,而不是隐含的选择。CHERI减少了系统的攻击面,即使攻击者成功利用该漏洞,他们也会获得最少的权限。CHERI以前已应用于MIPS和Arm ISAs。最近,CHERI及其完整的软件堆栈已移植到RISC-V 32位和64位变体[76]。CHERI-RISC-V规范与CHERI-MIPS共享许多体系结构特征,例如标记内存。但它们对内存中的地址有不同的解释。此外,CHERI相关的页面权限被添加到RISC-V体系结构页面表格式,而不是MIPS翻译后备缓冲区(TLB)条目。

密码原语

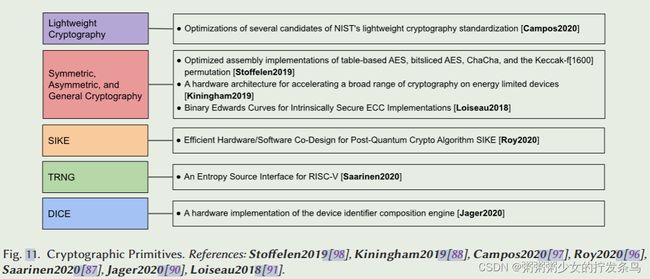

可信计算[175]、通信[176]、存储[177]、执行[50]和许多其他安全目标依赖于密码原语,包括对称和非对称密码、数据完整性算法、相互信任密钥管理和分发机制。随着应用程序生态系统的发展,密码原语出现了新的挑战和要求。图11总结了RISC-V域中的加密原语实现或性能优化项目。

轻量级密码

首先,小型物联网设备需要轻量级的加密算法。小型物联网设备通常受到CPU或内存资源的限制,它们的功能可能不足以支持标准加密算法的高效执行。如表3所示,最新的Polarfire RISC-V FPGA的平均单核计算性能仅为Intel Xeon 4215 x86处理器的3.1%。轻量级密码学已被提出以满足资源受限设备的要求[97]。轻量级在概念上可以指芯片面积大小、代码/内存大小、能源效率等。有一个ISO/IEC 29192标准用于轻量级分组密码。CLEFIA[178]、PRESENT[179]、LEA[180]是ISO分组密码算法中的三种。NIST还在筛选轻量级密码算法,这些算法将被纳入NIST轻量级密码标准。在受限环境中应用加密的一个主要挑战是安全性和性能之间的权衡。Fabio等人[97]分析了在RISC-V架构上优化NIST轻量级密码算法候选解决方案的不同策略。具体而言,他们展示了如何有效实施多种轻量级NIST候选产品,如Gimli、Sparkle、Saturnin、Ascon、Delirium和Xoodyak。他们研究了在汇编语言和C语言中优化对称密钥算法的总体影响,提出了诸如循环展开之类的优化,可以将软件实现的算法加速81%。

对称和非对称加密

Stoffelen等人[98]强调了RISC-V的特点,并为RV32I指令集提供了基于表的AES、位切片AES、ChaCha和Keccak-f[1600]的优化汇编实现。关于公钥密码学,他们研究了不带进位标志的任意精度整数算法的性能。他们对几个RISC-V扩展进行了定量性能研究,为未来的RISC-V核心设计和实现提供了设计见解。

固定功能硬件加速器(如AES引擎)无法支持新密码。Kiningham等人[88]介绍了Falcon,一种用于在能量受限设备上加速各种密码的硬件架构。Falcon提供了一个通用执行引擎,支持位片和置换指令,这是当前和未来主导密码的主干操作,包括AES、Cha-Cha、SHA-256、RSA、Curve25519 ECC和后量子密码学(如R-LWE)。在加密技术方面,Falcon提供了软件灵活性,同时与软件实现相比,将密码的能耗降低了5到60倍。这一改进使物联网应用程序在部署后升级密码变得可行,这样他们就可以随时了解最新的安全实践,而不会缩短设备部署寿命或牺牲应用程序工作负载。

为了应对物联网设备的安全挑战,Loiseau等人[91]为一组新的二进制Edwards曲线提出了一种快速、低功耗的加密技术,该曲线已被定义为达到284位的安全级别,适用于嵌入32位通用处理器的物联网设备。他们使用w坐标优化了点生成器的选择,以节省加法和加倍公式中的乘法运算。他们设法用4次乘法和4次平方计算出蒙哥马利阶梯的一步。除了性能优势外,这条曲线上的加密还具有固有的安全特性,可以抵御物理攻击。

SIKE后量子密码

量子计算机的进步使公钥密码系统的安全性面临风险[181]。公钥密码系统的安全基础是当整数很大时,整数分解问题非常复杂。然而,量子计算机可以比传统计算机以指数级的速度解决这个问题,这使现有的公钥密码系统面临风险。因此,如果量子计算机得以实现,公钥密码系统可能很容易被破坏。在这种背景下,NIST正在筛选能够抵御量子计算机潜在攻击的公钥加密和数字签名算法。后量子算法将增强FIPS 186-4、SP 800-56A和SP 800-56B。NIST在第三轮筛选中选出了7名入围者和8名候补者作为候选人。算法评估将很快完成。

SIKE公钥加密和密钥建立算法是NIST的备选算法之一[182]。它是一个很有前途的候选标准,但它的算法是资源密集型的。尽管SIKE的FPGA实现提供了低延迟和高性能,但它具有大面积和低灵活性的缺点。与FPGA实现相比,纯软件实现的性能要低得多。

软件和硬件协同设计对于优化性能、满足成本和功耗等设计约束以及显著缩短上市时间至关重要[183]。RISC-V的开放性提供了前所未有的硬件优化机会。Roy等人[96]提出了SIKE的软硬件协同设计方法,将基于冗余数的有限场加速器集成到基于Arm和RISC-V的两个微控制器平台中。结果表明,与Arm32和Arm64上的独立软件实现相比,使用场加速器增强的Arm Cortex-A9上的实现在时钟周期方面提供了显著的加速。此外,为了展示如何减少处理器和加速器之间的通信开销,他们将有限场加速器直接集成到RISC-V处理器的核心中。这是第一种在Arm和RISC-V平台上实现SIKE设计的软硬件协同设计方法。所提出的设计需要65500K时钟周期才能在Arm Cortex-A9处理器上执行SIKE。在RISC-V上,所提出的设计只需要36900K时钟周期。

TRNG

正如我们在第2.2节中所讨论的,随机数生成器是信任模块的重要根。Saarinen等人[87]提出了RISC-V真随机数生成器(TRNG)架构,该架构将熵源分量和加密的PRNG分离到单个接口中。这与以前的TRNG实现不同。他们描述了接口及其在密码学中的应用,并讨论了接口的背景和基本原理。该设计参考了主流ISA、最新的SP 800-90B和FIPS 140-3熵审查要求、AIS-31和IT安全评估通用标准,以及当前和新兴的加密要求,如后量子加密。体系结构的选择是对加密库中的安全微控制器、Linux内核和随机数生成器进行定量观察的结果。他们进一步将这种体系结构与当代的一些随机数生成器进行了比较,并描述了使用熵源和RISC-V AES指令的最小TRNG参考实现。

DICE

设备标识符组合引擎(DICE)是微控制器上可信计算的最低要求。目前,大多数实现使用的硬件并不是专门为此目的而设计的。这些实现依赖于黑盒MPU。由于使用的硬件不是最初为DICE设计的,因此在实现过程中存在某些陷阱。Jager等人[90]提出了一种基于微控制器的DICE架构,该架构配备了满足DICE要求的硬件。它包括对处理器流水线、专用内存块以及修改后的中断和调试模块的微小修改。他们创建了一个基于VexRiscV平台的FPGA原型,并评估了芯片尺寸的增加和DICE扩展对运行时间的影响,以证明DICE可以在对微控制器设计进行最小更改的情况下实现,并作为可信组件在物联网和汽车环境中使用。

防止侧信道攻击

侧信道攻击可以通过功率分析[184]和电磁分析(EMA)[185]进行。在第5.2节中,我们讨论了通过ISA扩展防止侧信道攻击的研究。除了ISA扩展之外,还有许多通用方法,例如在CPU执行流水线中实现对策,或者通过分析电路的RTL代码来检查硬件是否处于持续执行中。在本节中,我们将讨论一些检测和防止侧信道攻击的通用方法。具体而言,如图12所示,我们将讨论分支预测、TLB、核心间和定时侧信道,并讨论利用侧信道的功率分析和电磁攻击。我们还将讨论虚拟原型,它可以检测简单的侧通道。

分支预测漏洞

现代处理器的侧通道漏洞使硬件安全成为处理器设计的首要任务。Gonzalez等人[100]演示了如何使用基于RISC-V处理器的通用开源Berkeley无序机(BOOM)来研究在微体系结构级别减轻侧信道攻击。首先,他们复制了Spectre漏洞[21]的几个基本变体,这些变体利用了L1数据缓存中的推测执行。然后,他们针对这种类型的攻击实施初步的硬件缓解措施,证明其有效性,并衡量其对性能和区域大小的影响。与基线处理器相比,对硬件缓解的评估表明,在45nm工艺中,IPC增加了2%,面积增加了2.5%,时钟减少了0.36%。这项工作证实了开源RISC-V硬件生态系统对安全硬件研究的价值。

电源和电磁分析攻击

在无保护的微处理器上运行无保护的软件可能会导致各种侧通道泄漏,包括直接值泄漏、数据覆盖和电路级泄漏[103]。密码算法的软件实现容易受到侧信道分析(SCA)攻击,因为密码密钥可能通过处理器的可测量物理特性(如功耗和电磁辐射)泄漏。已经提出了各种具有解决方案的算法来缓解这个问题。然而,它们依赖于很少满足的设备假设,因此不容易实施。此外,这些解决方案不考虑与微体系结构相关的问题。Mulder等人[103]提出将侧信道分析的对策集成到RISC-V实现中。他们使用屏蔽技术在将机密写入内存之前对其进行封装,并在从内存读回机密之后执行反向操作来打开封装,以保护内存访问不受SCA的影响。该解决方案可防止一阶功率或电磁攻击,同时尽可能降低实施成本。评估结果证实了在受保护硬件平台上运行的各种加密原语的安全性。

动态频率缩放(DFS)是一种与时钟频率的动态变化有关的技术,通常是CPU或硬件模块在操作过程中的相关电压,以适应其功耗[186]。Dao等人[105]演示了如何将DFS技术集成到开源RISC-V处理器中,并将其用作对抗simple Power Analysis攻击的简单、经济高效的对策。其思想是,DFS模块可以在测量的功率跟踪中隐藏敏感信息,而处理器的硬件资源需求几乎不会改变。他们在Sakura-X FPGA板上实现了DFS,并证明了这种方法在减轻简单功率分析攻击方面的有用性。

大多数现代计算设备可以通过细粒度的操作来控制频率和电压。CLKSCREW[187]是一种新型的故障攻击,它利用能量管理机制的安全疏忽,使设备的频率超过其运行极限,从而导致故障和安全违规。静态和永久地限制频率和电压调制空间可以减轻这种情况攻击,但将导致性能和能源效率的显著下降。张等人[104]提出了一种运行时技术,该技术使用神经网络模型将不安全的运行性能点动态列入黑名单。该模型首先在设计时离线训练,然后在运行时通过检查一组选定的功能(如电源管理控制寄存器、定时误差信号和堆芯温度)进行调整。他们设计了一种名为黑名单(BL)核心的算法和硬件,可以高精度地检测和缓解这种基于电源管理的安全攻击。BL核心在功率、延迟和区域大小方面产生相对少量的开销。

定时攻击

算法的计算需要时间。如果算法没有在恒定的执行时间下仔细设计,可能会导致不同的输入具有不同的执行时间。如果计算涉及加密密钥等敏感信息,攻击者可能会通过遍历大量输入向量并准确测量每个测试向量的执行时间来反转密钥的内容,从而导致敏感信息泄露。通过时间信息窃取敏感密钥数据通常比使用已知的明文和密文对进行密码分析容易得多。

现代处理器中的转换后备缓冲区(TLB)可能会引起定时侧信道攻击。但是,由于TLB内部的未知寻址功能以及攻击者有限的监控能力(最多只能覆盖受害者的粗粒度数据访问),利用TLB通道具有挑战性。然而,最近研究人员可以对TLB内部的寻址功能进行逆向工程,并设计出一种机器学习策略,利用受害者记忆活动的高分辨率时间特征,使TLB侧通道攻击变得实用[188]。为了减轻这种风险,Deng等人[99]介绍了一种新的三步建模方法,该方法用于详尽列举所有可能的基于TLB的定时漏洞。步骤1执行存储器操作并将TLB块置于已知的初始状态。然后,步骤2执行第二存储器操作以改变TLB块的状态。最后,步骤3执行最后的存储器操作,并且最终操作的时间取决于步骤1、步骤2和步骤3的地址。超过三步的攻击可以分解为三步攻击。基于三步模型,他们展示了如何自动生成一个可以测试TLB漏洞的微安全基准。他们提出了两种新的安全TLB设计:静态分区(SP)TLB和随机填充(RF)TLB。对RISC-V Rocket Core中实现的安全TLB的评估表明,新的TLB不仅可以抵御先前宣布的攻击,还可以抵御使用新的三步模型发现的TLB中其他新的基于定时的攻击。基于FPGA的评估表明,RF TLB可以抵御所有攻击,性能开销小于10%。

多处理器片上系统(MPSoC)是一个流行的计算平台,由于其能效和灵活性,适合各种应用。具有异构架构的SoC允许集成各种中央处理单元,甚至同一系统上的图形处理器也越来越流行[189]。与许多其他平台一样,它们也容易受到侧通道攻击(SCA)的攻击。逻辑SCA可以通过简单地观察依赖于受害者在MPSoC上执行的软件的系统属性来检索敏感信息,这是非常有害的。不幸的是,目前的许多保护机制要么依赖于平台,要么只对少数攻击有效。Reinbrecht[102]介绍了Guard NoC,这是一种安全的片上网络(NoC)架构,可以保护MPSoC免受各种逻辑SCA的影响。安全的NoC使用三种独立于应用程序的策略来隐藏和隔离敏感信息,方法是屏蔽操作的执行时间,并采用双重通信策略,如同时使用分组和电路交换。分组交换用于安全分组,电路交换用于公共分组。评估表明,该安全NoC可以抵抗实际的逻辑SCA,几乎不会泄露任何信息,同时具有最小的区域大小和功耗。

定时侧信道攻击是密码算法中的一个重要问题。如果实现的执行时间取决于秘密信息,则对手可以通过测量执行时间来推断秘密。最近出现了不同的方法来探索加密实现中的信息泄漏,并保护它们免受这些攻击。例如,在第3.1节中,我们讨论了IODINE[64],它翻译Verilog代码进行形式分析,以检测定时信道。然而,关于ISA仿真的内容很少以及它对定时攻击的影响。Napoli等人[101]研究了OI-DBT,一种使用不同区域形成技术(RFT)的动态二进制翻译器,对密码算法的恒定时间和非恒定时间的实现的影响。实验表明,仿真可以对秘密泄漏产生显著影响,在某些情况下甚至可以缓解泄漏。此外,结果表明,模拟器对RFT启发式的选择也对这些泄漏产生了影响。

在第3.2节中,我们讨论了程序模糊作为一种广泛使用的知识产权(IP)保护技术,以抵御反向工程攻击。Biswas等人[190]观察到,变换序列的选择对定时信道信息泄漏有显著影响。某些转换序列可能会导致比原始程序更高的泄漏。Biswas等人提出了一种基于遗传算法的定时信道敏感程序模糊优化框架,以在性能和防止定时侧信道泄漏方面找到模糊转换函数的最佳组合。他们评估了RISC-V火箭核心的新框架。他们使用dudet工具来验证所提出的TSC-SPOOF框架为ModExp和MulMod16程序提供了优化点,同时减少了定时信道泄漏。他们观察到,对于优化的ModExp和MulMod16程序,分别需要大约1M和2M的测量才能通过10的t统计量。但对于初始群体中的两个程序,只需要20K的测量值就可以跨越相同的t统计量。

堆芯内部侧通道

保护飞地免受特权软件攻击的系统必须考虑基于软件的侧通道攻击。针对可以从特权软件发起的攻击的保护是一种新兴的攻击模式。Van等人[106]提出,通过强制所有活动飞地在其各自独立的核心上物理隔离,从而减轻核心内部的侧信道攻击,来防范核心内部侧信道攻击。他们还根据安全区域的所有权重新设计了内存层次结构,以保护安全区域免受核心内部通道攻击。物理隔离和重新设计的内存层次结构的结合可以保护飞地免受所有已知的基于软件的侧通道攻击。内存标签用于保护飞地内存的机密性和完整性。引导垫片是RoT,管理垫片可以从中开始管理保护内存的标签。管理垫片是TCB的软件部分。硬件强制包围区仅访问其有权访问的页面,而管理填充程序是唯一允许更改标记目录中值的代码。管理填充程序不是一个操作系统,它只实现安全维护飞地生命周期和转移页面所有权所需的最低逻辑。他们实现了该系统,并用通信性能、内存开销和硬件面积指标对其进行了评估。评估表明,在现代片上系统中添加安全内核将使CPU复杂度增加约14.5%,硬件面积增加不到2%。存储额外的标记数据会使最后一级缓存的大小增加2%到13%。

基于虚拟样机的侧通道检测

在设计阶段评估软件安全漏洞可以在最早阶段发现问题,并避免后期漏洞修复的成本,因此这是非常关键的。Sauvage等人[107]描述了一种通过标量乘法实现的虚拟原型,旨在保护平台免受简单的侧信道攻击。他们使用Mentor Graphics Modelsim工具来获得尽可能接近现实的信息泄漏再现,需要比特和时钟周期精度来模拟PULPino[191]上软件实现的执行,PULPino[191]是一台开源的32位RISC-V微型计算机。对于每个时钟周期,他们计算进入微控制器的位数、功耗图像,并观察程序计数器以识别执行的汇编指令,然后识别相应的C函数。它们使用依赖于mbed TLS库的加密原语的naive double和add实现作为参考。虚拟分析指出,double函数和add函数在管理变量和内部操作方面存在差异,可以用来提取私钥。这种方法还不成熟,在实际应用中面临许多挑战,如提高模拟性能、更逼真的攻击模型和更自动化的部署。

结论和未来工作

基于硬件的安全技术,如内存保护和指令集安全扩展,已在实践中得到广泛应用。自从Meltdown和Spectre漏洞爆发以来,计算机硬件和体系结构的安全性受到了业界和学术界的广泛关注,吸引了越来越多的研究。RISC-V作为一种新的开放指令集,受到了广泛的关注,并正在走向主流。尽管与RISC-V相关的研究项目越来越多,但RISC-V作为一种新架构的安全性研究相对滞后。在这篇文章中,我们调查了RISC-V硬件和架构安全研究的现状,希望为读者提供RISC-V安全生态系统的全貌。具体来说,我们首先简要介绍了RISC-V的背景和体系结构安全基础,然后分主题介绍了RISC-V的安全研究。我们重点讨论硬件和体系结构的安全性。我们的研究涵盖硬件和物理访问安全、硬件辅助安全单元、ISA安全扩展、内存保护、加密原语和侧通道攻击保护。在调查过程中,我们注意到RISC-V安全的硬件和架构基础已经到位,并且已经建立了广泛的安全机制。

我们还注意到RISC-V的密码指令集并不完整,标准化工作仍在进行中。指令集是RISC-V在体系结构层最大的改进空间。通过指令集实现高效的密码算法将是一项重要的工作。此外,RISC-V架构的安全基础,如PMP,可能会通过侧信道受到攻击[192]。防止体系结构安全基础受到侧通道的攻击将是一个重要的研究课题。如上所述,RISC-V是一种新的体系结构,一些研究相对滞后。将其他体系结构的经典安全应用程序移植到RISC-V将是不久的将来的主要任务。例如,RISC-V社区正在移植Arm的OP-TEE实现。将RISC-V与Arm等其他体系结构在相关领域进行比较将是有意义的。此外,我们还可以从我们的总结中看到,尽管目前RISC-V的研究已经涵盖了广泛的安全主题,但许多研究仍处于早期阶段,相关实现尚未成熟。例如,目前对内存保护的研究主要集中在标记内存上,只有少数研究是关于内存隔离和加密验证的。关于逻辑锁定、电磁注入攻击、侧通道预防和检测以及控制流完整性的研究还不成熟。RISC-V安全性课题仍有广阔的研究空间。在本文中,我们主要讨论RISC-V的硬件和体系结构的安全性。下一步,我们将继续对RISC-V固件和系统以及软件和应用程序的安全性进行全面研究,以实现RISC-V安全频谱的完全覆盖。

据我们所知,这是第一篇关于RISC-V安全性的全面综述文章。我们希望这篇文章能让读者全面了解现有的RICS-V安全机制,甚至从更广泛的角度了解嵌入式系统和通用计算机架构安全的最新研究。