萌新的FPGA学习绪论-1

萌新的FPGA学习绪论-1

其实很多的课和内容都是相通的

我在跑完单周期的RiscV时候 虽然最后还差点意思但是基本的逻辑实现没有特别大的问题

过两天写一个Spec文档说明一下

由于开始一个新的设计 所以对于RiscV的设计暂时放到一边希望我能在接下来的时间内尽快完成

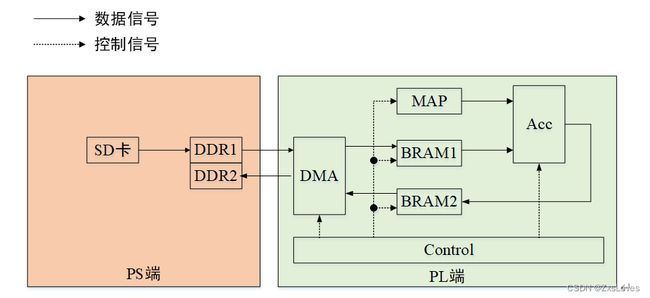

暂时不说这个了 先开始讲述 最近要实现的SOC设计 将SD卡内的文件读取到FPGA板子上 再通过内部的逻辑完成功能 其实有很多关键的技术节点

比如在SD卡上如何用C语言控制串口 作为一个简单的MCU发送数据

而在FPGA上如何通过verilog实现电路的连接和功能模块的编写

对于初学者的我是一个很大的考验。

上面的絮絮叨叨结束 ,接下来开始讲述。 我先通读一遍参考手册,因为我没用过FPGA的板子 也是从头学起。

1、顶层文件对象+功能+top比如:video_oneline_top

2、逻辑控制文件介于顶层和驱动层文件之间对象+ctr比如:ddr_ctr.v

3、驱动程序命名对象+功能+dri比如:lcd_dri.v、uart_rxd_dri.v

4、参数文件命名对象+para比如:lcd_para.v

5、模块接口命名:文件名+u比如 lcd_dir lcd_dir_u(…)

6、模块接口命名:特征名+文件名+u比如 mcb_read c3_mcb_read_u

8、端口注释input Video_vs_i,//输入场同步入

9、信号命名命名总体规则:对象+功能(+极性)+特性

10、时钟信号 对象+功能+特性比如:phy_txclk_i、sys_50mhz_i

11、复位信号对象+功能+极性+特性比如:phy_rst_n_i、sys_rst_n_i

12、延迟信号对象+功能+特性 1+特征 2比如:fram_sync_i_r0、fram_sync_i_r1

13、特定功能计数器 对象+cnt比如:line_cnt、div_cnt0、div_cnt1功能+cnt比如:wr_cnt、rd_cnt

14、一般计数器cnt+序号用于不容易混淆的计数比如:cnt0、cnt1、cnt2

15、 时序同步信号对象+功能+特性比如:line_sync_i、fram_sync_i

16、 使能信号功能+en比如:wr_en、rd_en对象+功能+en比如:fifo_wr_en、mcb_wr_en

编写逻辑

module detect_3( input clk_i, input rst_n_i, output out_o ); reg out_r;

//状态声明和状态编码

reg [1:0] Current_state;

reg [1:0] Next_state;

parameter [1:0] S0=2'b00;

parameter [1:0] S1=2'b01;

parameter [1:0] S2=2'b10;

parameter [1:0] S3=2'b11;

//时序逻辑:描述状态转换

always@(posedge clk_i)

begin if(!rst_n_i)

Current_state<=0;

else Current_state<=Next_state;

end //组合逻辑:描述下一状态

always@(*)

begin

case(Current_state) S0:

Next_state = S1;

S1:

Next_state = S2;

S2:

Next_state = S3;

S3:

Next_state = Next_state;

default :

Next_state = S0;

endcase end //输出逻辑:让输出 out,经过寄存器 out_r 锁存后输出,消除毛刺

always@(*)

begin

case(Current_state)

S0,S2: out_r<=1'b0;

S1,S3: out_r<=1'b1;

default : out_r<=out_r;

endcase

end

assign out_o=out_r;

三段式状态机在第一个 always 模块采用同步时序逻辑方式描述状态转移,第二个 always 模块采用组合逻辑方

式描述状态转移规律,第三个 always 描述电路的输出。通常让输出信号经过寄存器缓存之后再输出,消除电路毛

刺。这种状态机也是比较推崇的,主要是由于维护方便,组合逻辑与时序逻辑完全独立。

我其实不太会写tb文件 我觉得tb好难啊

tb用的很多都是不可综合的语句

/*----------------------------------------------------------------仿真控制语句及系统任务描述----------------------------------------------------------------*/$stop //停止运行仿真,modelsim 中可继续仿真

$stop(n) //带参数系统任务,根据参数 0,1 或 2 不同,输出仿真信息

$finish //结束运行仿真,不可继续仿真

$finish(n) //带参数系统任务,根据参数 0,1 或 2 不同,输出仿真信息//0:不输出任何信息

//1:输出当前仿真时刻和位置

//2:输出当前仿真时刻、位置和仿真过程中用到的 memory 以及 CPU 时间的统计

$random //产生随机数

$random % n //产生范围-n 到 n 之间的随机数

{$random} % n //产生范围 0 到 n 之间的随机数/*----------------------------------------------------------------仿真终端显示描述----------------------------------------------------------------*/

$monitor //仿真打印输出,大印出仿真过程中的变量,使其终端显示/

*$monitor($time,,,"clk=%d reset=%d out=%d",clk,reset,out);*/

$display //终端打印字符串,显示仿真结果等/*

$display(” Simulation start ! ");

$display(” At time %t,input is %b%b%b,output is %b",$time,a,b,en,z);

$time //返回 64 位整型时间

$stime //返回 32 位整型时间

$realtime //实行实型模拟时间

基本的知识讲述完毕 接下来讲述的是

单个简单的设计

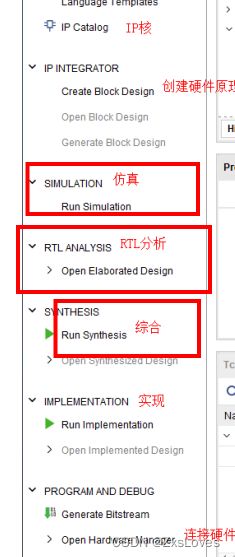

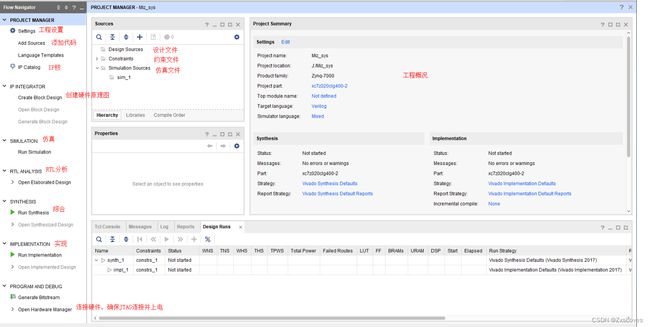

我们现在先确定一下vivado的基本功能

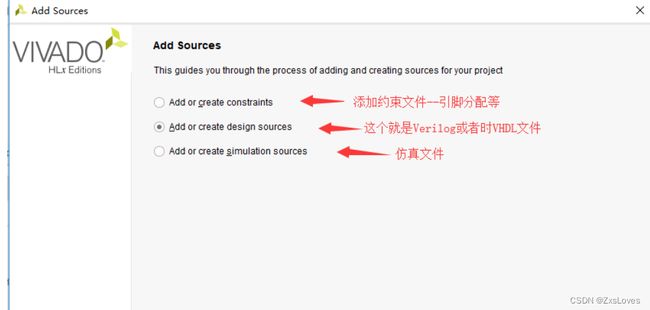

添加管教约束文件

管教约束文件就是.xdc文件

管脚约束文件,即.xdc 文件,一般情况,生成后会放在 Miz_sys.srcs\constrs_1 文件夹中,这里的“Miz_sys”对应的是创建工程的名称。添加管脚约束有三种方法,分别是手动新建 XDC PIN 脚约束文件、直接加入已经写好的约束文件、综合后添加管脚约束,用户根据实际情况选择其中一种方法,可以提高工作效率。

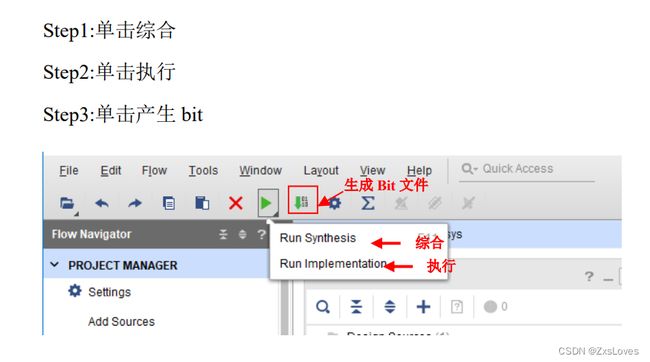

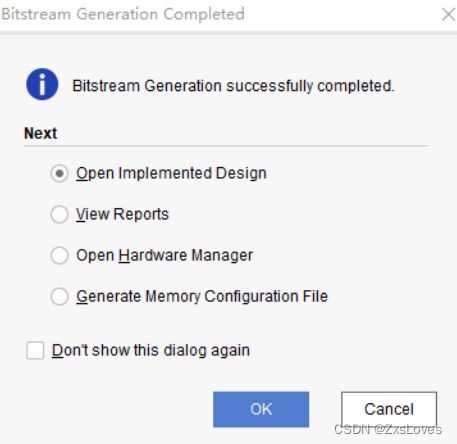

如何编译并产生bit文件

我们对于程序的固化的一个准备

如果我们想要固化一个ZYNQ程序,以及为这个程序做一个镜像文件该如何处理? 对于这个问题 我想到了之前的SOC任务 在PL PS端的实现

我们准备固化ZYNQ的程序

确定PL部分的bit的文件 PS部分的elf文件

我们在此处介绍一下zynq从SD卡的启动过程

zynq和大多数arm启动过程一样,分为三个阶段 阶段0 阶段1 阶段2

阶段 0:即传统的 BootROM 过程。ZYNQ 芯片 ROM 里面固化了一段不可修改的程序,只要 ZYNQ 一上电,这

段程序就会执行。它将对 ZYNQ 的 NAND、NOR、SD 等基本外设控制器进行初始化。把 SD 卡这类易失的存储器

件初始化后,就会把其中的程序拷贝到 ZYNQ 的 OCM(On-chip memory)。这个被拷贝到片上 RAM 执行的程序

就是我们今天要制作的文件——BOOT.bin。

阶段 1:BOOT.bin 加载到 OCM 上开始执行。 BOOT.bin 由 FSBL.elf+该工程.bit+该工程.elf 构成。阶段 1 要做的

就是:首先配置 PS 部分,PS 完成初始化后,会去配置 PL 部分,最后去加载阶段 2 的代码。

阶段 2:这一阶段是可选的,主要是为了完成 Linux 系统启动过程。本次实验暂时不需要。

关于ZYNQ启动模式的选择

这里有个疑问,众所周知 ZYNQ 具有多种启动方式:NOR, NAND, Quad-SPI, SD Card 以及 JTAG 。ZYNQ 如何判断到底从哪里启动呢?实际上,当上电后,ZYNQ 会根据模式管脚的设定,选用 boot 的方式。

我拿在手里的板子是米联客 他有两种启动方式 一种是在SD中启动

另一种是QSPI FLASH启动 开发板通过拨码开关对管教进行约束 改变启动模式