FPGA project : rom_vga_jump

只有vga_pix 模块代码与rom_vga不同,所以只上传了这个模块的代码与仿真代码。

// #define BLACK 0x0000 // 黑色

// #define NAVY 0x000F // 深蓝色

// #define DGREEN 0x03E0 // 深绿色

// #define DCYAN 0x03EF // 深青色

// #define MAROON 0x7800 // 深红色

// #define PURPLE 0x780F // 紫色

// #define OLIVE 0x7BE0 // 橄榄绿

// #define LGRAY 0xC618 // 灰白色

// #define DGRAY 0x7BEF // 深灰色

// #define BLUE 0x001F // 蓝色

// #define GREEN 0x07E0 // 绿色

// #define CYAN 0x07FF // 青色

// #define RED 0xF800 // 红色

// #define MAGENTA 0xF81F // 品红

// #define YELLOW 0xFFE0 // 黄色

// #define WHITE 0xFFFF // 白色

// rgb 565

module vga_pix (

input wire vga_clk ,

input wire vga_rst_n ,

input wire [9:0] pix_x ,

input wire [9:0] pix_y ,

output wire [15:0] pix_data

);

// parameter

parameter PIC_SIZE= 14'd1_0000 ,

H_PIC = 10'd100 ,

V_PIC = 10'd100 ,

H_VALID = 10'd640 ,

V_VALID = 10'd480 ;

parameter RED = 16'hF800 ,

ORANGE = 16'hFC00 ,

YELLOW = 16'hFFe0 ,

GREEN = 16'h07e0 ,

QING = 16'h07FF ,

BLUE = 16'h001F ,

PURPLE = 16'hF81F ,

BLACK = 16'h0000 ,

WHITE = 16'hFFFF ,

GRAY = 16'hD69A ;

// wire signal define

wire rden_w ;

wire [13:0] address_w;

wire [15:0] data_pic ; // 图片的像素

// reg signal define

reg [15:0] data_pix; // 10 个彩条

reg rden ; // 读使能信号超前图像数据一个时钟周期。

reg [13:0] address ; // 在读使能信号拉高,每个时钟周期自加一,0 ~ PIC_SIZE - 1

reg pic_vald; // 图片使能

reg [9:0] x_move ; // x轴方向的,偏移量

reg x_flag ; // 为0 表示向右移动;为1 表示向左移动。

reg [9:0] y_move ;

reg y_flag ; // 为0 表示向下移动;为1 表示向上移动。

// reg [15:0] data_pix; // 10 个彩条

always @(posedge vga_clk or negedge vga_rst_n) begin

if(~vga_rst_n) begin

data_pix <= 10'h3ff ;

end else begin // 有简便写法 ( H_VALID / 10 ) * n

if((pix_x >= 10'd0) && (pix_x <= H_VALID / 10 - 1'b1))

data_pix <= RED ;

else

if((pix_x >= H_VALID / 10) && (pix_x <= (H_VALID / 10) * 2 - 1'b1))

data_pix <= ORANGE ;

else

if((pix_x >= (H_VALID / 10) * 2) && (pix_x <= (H_VALID / 10) * 3 - 1'b1))

data_pix <= YELLOW ;

else

if((pix_x >= (H_VALID / 10) * 3) && (pix_x <= (H_VALID / 10) * 4 - 1'b1))

data_pix <= GREEN ;

else

if((pix_x >= (H_VALID / 10) * 4) && (pix_x <= (H_VALID / 10) * 5 - 1'b1))

data_pix <= QING ;

else

if((pix_x >= (H_VALID / 10) * 5) && (pix_x <= (H_VALID / 10) * 6 - 1'b1))

data_pix <= BLUE ;

else

if((pix_x >= (H_VALID / 10) * 6) && (pix_x <= (H_VALID / 10) * 7 - 1'b1))

data_pix <= PURPLE ;

else

if((pix_x >= (H_VALID / 10) * 7) && (pix_x <= (H_VALID / 10) * 8 - 1'b1))

data_pix <= BLACK ;

else

if((pix_x >= (H_VALID / 10) * 8) && (pix_x <= (H_VALID / 10) * 9 - 1'b1))

data_pix <= WHITE ;

else

if((pix_x >= (H_VALID / 10) * 9) && (pix_x <= H_VALID - 1'b1) )

data_pix <= GRAY ;

else

data_pix <= BLACK ;

end

end

// reg rden ;

// wire rden_w ;

always @(posedge vga_clk or negedge vga_rst_n) begin

if(~vga_rst_n) begin

rden <= 1'b0 ;

end else begin

if(((pix_y >= y_move) && (pix_y <= (y_move + V_PIC - 1))) && ((pix_x >= x_move) && (pix_x <= (x_move + H_PIC - 1)))) begin

rden <= 1'b1 ;

end else begin

rden <= 1'b0 ;

end

end

end

assign rden_w = rden ;

// reg [13:0] address ;

always @(posedge vga_clk or negedge vga_rst_n) begin

if(~vga_rst_n) begin

address <= 0 ;

end else begin

if(rden == 1'b1) begin

if(address == PIC_SIZE - 1) begin

address <= 0 ;

end else begin

address <= address + 1'b1 ;

end

end else begin

address <= address ;

end

end

end

assign address_w = address ;

// reg pic_vald;

always @(posedge vga_clk or negedge vga_rst_n) begin

if(~vga_rst_n) begin

pic_vald <= 1'b0 ;

end else begin

pic_vald <= rden ;

end

end

// reg [9:0] x_move ;

always @(posedge vga_clk or negedge vga_rst_n) begin

if(~vga_rst_n) begin

x_move <= 10'd0 ;

end else begin

if(pix_x == H_VALID - 1 && x_flag == 1'b0 && pix_y == V_VALID - 1) begin

x_move <= x_move + 1'b1 ;

end else begin

if(pix_x == H_VALID - 1 && x_flag == 1'b1 && pix_y == V_VALID - 1) begin

x_move <= x_move - 1'b1 ;

end else begin

x_move <= x_move ;

end

end

end

end

// reg x_flag ;

always @(posedge vga_clk or negedge vga_rst_n) begin

if(~vga_rst_n) begin

x_flag <= 1'b0 ;

end else begin

if((pix_x == H_VALID - 1 && pix_y == V_VALID - 10 && x_move == (H_VALID - H_PIC - 2) && x_flag == 1'b0)

|| (pix_x == H_VALID - 1 && pix_y == V_VALID - 10 && x_move == 0 && x_flag == 1'b1)) begin

x_flag <= ~x_flag ;

end else begin

x_flag <= x_flag ;

end

end

end

// reg [9:0] y_move ;

always @(posedge vga_clk or negedge vga_rst_n) begin

if(~vga_rst_n) begin

y_move <= 10'd0 ;

end else begin

if(pix_x == H_VALID - 1 && y_flag == 1'b0 && pix_y == V_VALID - 1) begin

y_move <= y_move + 1'b1 ;

end else begin

if(pix_x == H_VALID - 1 && y_flag == 1'b1 && pix_y == V_VALID - 1) begin

y_move <= y_move - 1'b1 ;

end else begin

y_move <= y_move ;

end

end

end

end

// reg y_flag ;

always @(posedge vga_clk or negedge vga_rst_n) begin

if(~vga_rst_n) begin

y_flag <= 1'b0 ;

end else begin

if((pix_x == H_VALID - 1 && pix_y == V_VALID - 10 && y_move == (V_VALID - V_PIC - 1) && y_flag == 1'b0)

|| (pix_x == H_VALID - 1 && pix_y == V_VALID - 10 && y_move == 0 && y_flag == 1'b1)) begin

y_flag <= ~y_flag ;

end else begin

y_flag <= y_flag ;

end

end

end

// wire [15:0] data_pic;

/*****************output signal*******************************************/

// reg [15:0] pix_data

assign pix_data = (pic_vald == 1'b1) ? data_pic : data_pix ;

/****************新增代码*******************/

rom_pic rom_pic_insert(

.address ( address_w ),

.clock ( vga_clk ),

.rden ( rden_w ),

.q ( data_pic )

);

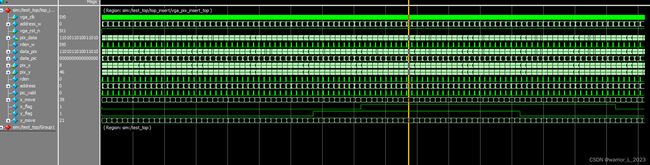

endmodule `timescale 1ns/1ns

module test_top ();

reg sys_clk ;

reg sys_rst_n ;

wire [15:00] rgb ;

wire hsync ;

wire vsync ;

top top_insert(

.sys_clk ( sys_clk ) ,

.sys_rst_n ( sys_rst_n ) ,

.rgb ( rgb ) ,

.hsync ( hsync ) ,

.vsync ( vsync )

);

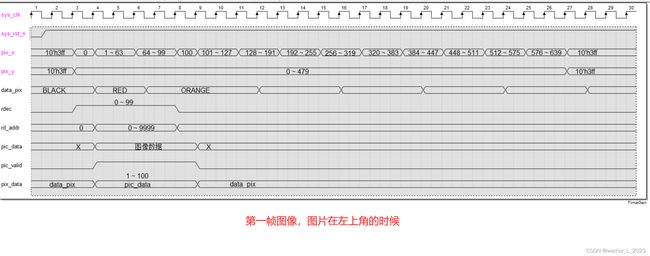

defparam top_insert.vga_pix_insert_top.H_VALID = 60 ,

top_insert.vga_pix_insert_top.V_VALID = 50 ,

top_insert.vga_pix_insert_top.H_PIC = 10 ,

top_insert.vga_pix_insert_top.V_PIC = 10 ,

top_insert.vga_pix_insert_top.PIC_SIZE= 100 ;

defparam top_insert.vga_ctrl_insert_top.H_SYNC = 10'd2 ,

top_insert.vga_ctrl_insert_top.H_BACK = 10'd2 ,

top_insert.vga_ctrl_insert_top.H_LEFT = 10'd2 ,

top_insert.vga_ctrl_insert_top.H_VALID = 10'd60 ,

top_insert.vga_ctrl_insert_top.H_RIGHT = 10'd2 ,

top_insert.vga_ctrl_insert_top.H_FORNT = 10'd2 ,

top_insert.vga_ctrl_insert_top.H_TOTAL = 10'd70 ;

defparam top_insert.vga_ctrl_insert_top.V_SYNC = 10'd2 ,

top_insert.vga_ctrl_insert_top.V_BACK = 10'd2 ,

top_insert.vga_ctrl_insert_top.V_TOP = 10'd2 ,

top_insert.vga_ctrl_insert_top.V_VALID = 10'd50 ,

top_insert.vga_ctrl_insert_top.V_BOTTOM= 10'd2 ,

top_insert.vga_ctrl_insert_top.V_FRONT = 10'd2 ,

top_insert.vga_ctrl_insert_top.V_TOTAL = 10'd60 ;

parameter CYCLE = 20 ;

initial begin

sys_clk = 1'b1 ;

sys_rst_n <= 1'b0 ;

#(CYCLE) ;

sys_rst_n = 1'b1 ;

end

always #(CYCLE / 2) sys_clk = ~sys_clk ;

endmodule