SSI同步时序逻辑电路设计步骤以及例题解析

一般来说,同步时序电路设计步骤如下:

1、进行逻辑抽象,设定输入、输出变量,根据不同状态的转换关系建立原始状态图,列出原始状态转移真值表。

2、利用状态等效方法对原始状态转移真值表进行化简,得出化简后的状态转移真值表。

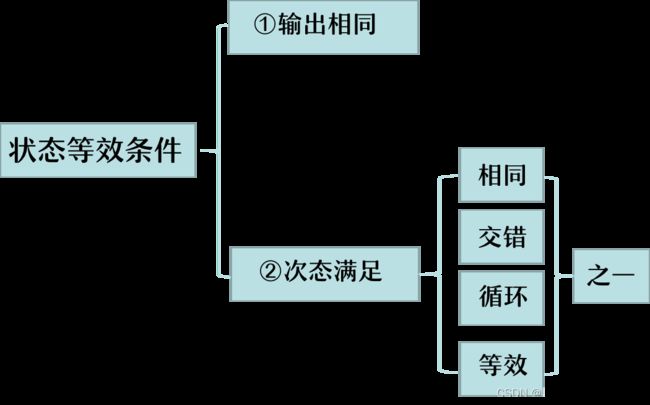

***状态等效的条件:两个(或多个)状态相应的输出相同;次态满足相同、交错、循环、等效之一的条件,那么这些状态是等效的。

图1.状态等效条件图

3、对状态转移真值表进行状态分配。

***分配相邻代码的原则:

①次态相同的现态(优先)。指现态

②同一现态的次态。指次态

③相同输出的现态。指现态

④次态次数最多的分配逻辑‘0’。

[原则1最重要,如果原则1全部满足,必须优先分配相邻代码。其次,根据要求的频度,决定是否分配相邻代码,原则4是分配逻辑零的状态。(优先级:①>②>③)]

4、求解激励函数与输出函数表达式。

将化简后的编码状态表按照次态每一位进行拆分,得到每个触发器的状态表,可依此求出每个触发器的状态方程;同理也可以根据输出变量Z求出输出方程。然后将触发器的状态方程和特征方程进行比较可求出触发器的激励函数,比如:JK、D等激励函数表达式。

5、根据触发器的激励函数与输出函数做出电路图。(无需掌握)

———————————————————————————————————————————————————————————

例题:设计一个'1010'序列检测器,当输入1010时,序列检测器 的输出为1,其他情况下 输出为0。

解析:按照上述步骤依次进行。

①作出原始状态图和状态转移表,并进行化简。

(***设置状态变量:

S0为初始状态;

S1为输入了1的状态;

S2为连续2bit输入10的状态;

S3为连续3bit输入101的状态;

S4为连续4bit输入1010的状态;)

作出的原始状态图如下:

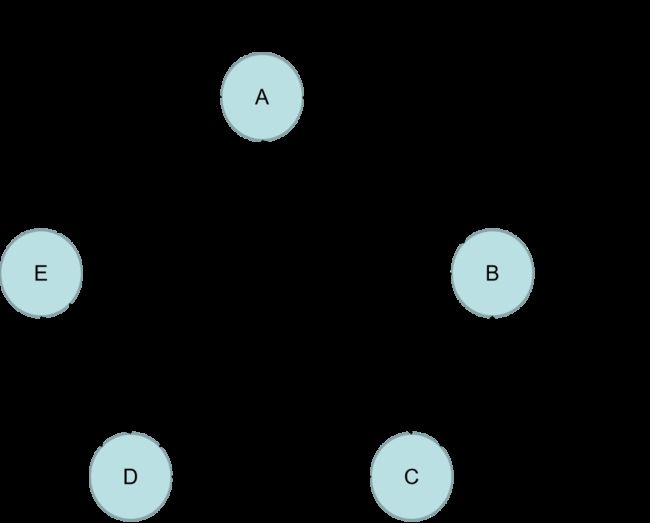

图2.化简前的原始状态图 图3.化简后的原始状态图

不怎么会掌握原始状态图画法的UU可以看一下这篇博客:https://blog.csdn.net/weixin_42048463/article/details/101974855

可以用隐含表法化简同步时序逻辑电路,详情见:https://www.doc88.com/p-11747101104731.html

化简前后的状态转移真值表如下:

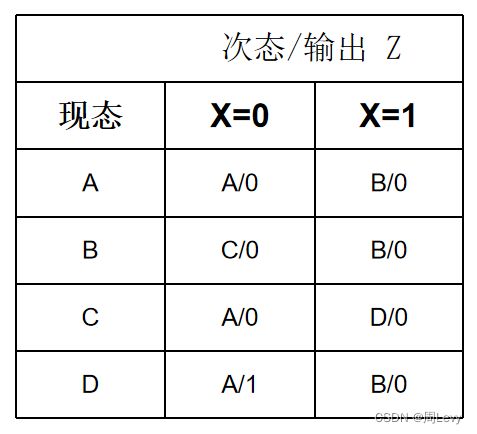

图4.化简前状态转移真值表 图5.化简后状态转移真值表

②对状态转移真值表进行状态分配。

根据状态分配原则并结合化简后的状态转移真值表进行状态分配:

I、次态相同的现态: AD

II、同一现态的次态:AD,AB,BC

III、相同输出的现态:AB,BC,AC

IV、次态次数最多分配‘0’:A或B (A好一点)

***给分配相邻代码的优先级为:(AD)->(AB,BC)->(AB,AC,BC)

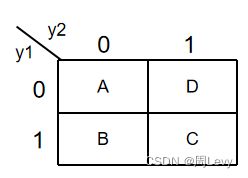

作出状态分配方案:

图6.状态分配方案

根据状态分配方案,将A、B、C、D编码为00、01、11、10,作出编码状态表。

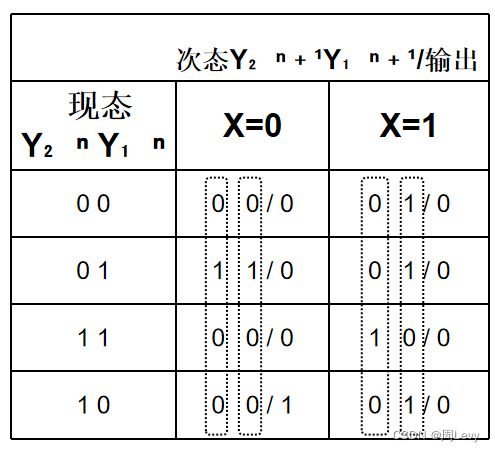

图7.编码状态表

③求解激励函数与输出函数表达式。

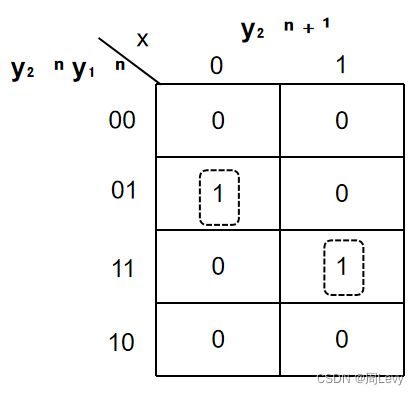

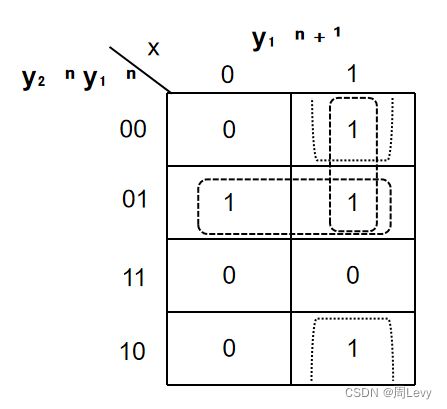

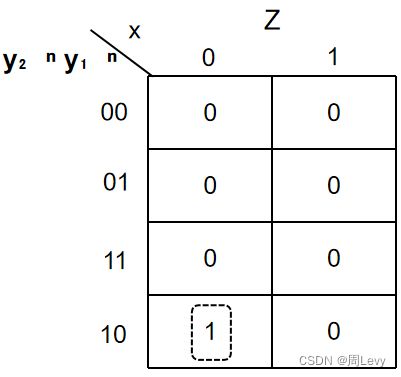

从编码状态表分解出状函数y₂ⁿ﹢¹(y₁ⁿ,y₂ⁿ,X)、y₁ⁿ﹢¹(y₁ⁿ,y₂ⁿ,X)与输出函数Z(y₁ⁿ,y₂ⁿ,X)的卡诺图,画卡诺圈并进行化简。

图8.从状态表到激励函数与输出函数的卡诺图

*由卡诺图求得状态方程与输出方程:

y₂ⁿ﹢¹ = (#y₂ⁿ)y₁ⁿ(#x)+y₂ⁿy₁ⁿx

y₁ⁿ﹢¹ = (#y₂ⁿ)y₁ⁿ+(#y₂ⁿ)x+(#y₁ⁿ)x

Z = y₂ⁿ(#y₁ⁿ)(#x)

*如果选用JK触发器,将所求特征方程与JK触发器特征方程进行对比,

可求得:

J₂ = y₁ⁿ(#x) K₂ = #(y₁ⁿx)

J₁ = (#y₂ⁿ)x+x K₁ = #[(#y₂ⁿ)+(#y₂ⁿ)x]

④根据触发器的激励函数与输出函数做出电路图。(无需掌握)

到此,SSI同步时序逻辑电路设计完成!

参考资料:[1]李碧芬. 用隐含表法化简同步时序逻辑电路设计中的原始状态表的探讨[J]. 湖北广播电视大学学报, 2009, 29(2):2.

[2] CSDN博主好梦成真Kevin的博客《110序列检测器设计》.