PCIe中断之MSI和MSI-X的区别(详细)总结附图文快速掌握

目录

- 一、整体介绍

- 二、MSI和MSI-X对比

-

- 2.1 中断向量连续

- 2.2 映射区域区别

- 2.3 MSI-X配置空间

-

- 2.3.1 MSI-X Capbility介绍

- 2.3.2 Capbility ID介绍

- 2.3.3 Message Control介绍

- 2.3.4 MSI-X Table介绍

- 2.3.5 MSI-X Pending Table(PBA)介绍

- 三、MSI 处理过程

-

- 3.1 Message处理

- 3.2 详细过程

- 四、MSI⁃X 中断处理请求过程

- 五、INTx中断介绍

-

- 5.1 PCI INTx中断流程

- 六、其他相关链接

-

- 1、软中断过程总结

- 2、中断机制详细总结

- 3、Linux下中断机制之tasklet执行过程总结

一、整体介绍

本文主要介绍MSI和MSI的基本概念和差异,通过图文的方式方便读者快速掌握,最后章节也简单介绍了INTx的基本概念。

MSI(Message Signaled Interrupts)是一种通过在内存中写入信息来产生中断的方式,其中内存地址由设备驱动程序和硬件设备协商确定。MSI与传统的中断线不同,它不需要单独的中断线,而是通过PCI总线进行通信。

MSI-X(Extended Message Signaled Interrupts)是在MSI的基础上扩展的一种中断方式,它允许设备使用多个独立的中断信号,从而提高了中断处理的效率。这对于那些需要高速响应的应用程序尤其有用,例如虚拟化或者高性能计算。

MSI/MSI-X机制的引入解决了传统Line-based Interrupt机制的种种限制,包括:

1、无需经过I/O APIC转发中断,直接通过PCI/PCIe Memory Write Transaction向CPU发送中断,效率更高

2、每个PCI Function可以支持分配多个中断向量,满足同一个设备有多个不同中断请求的需要当分配多个中断向量给同1个PCI Function时,提供按中断向量进行屏蔽的功能,更为灵活。

总的来说,PCIe总线引出MSI-X机制的主要目的是为了解决使用该机制不需要中断控制器分配给该设备的中断向量号连续所带来的问题,同时扩展PCIe设备使用中断向量的个数。然而,MSI-X需要更多的硬件资源,所以不是所有设备都能使用它。

二、MSI和MSI-X对比

主要区别如下表:

| MSI | MSI-X | |

|---|---|---|

| 中断向量数 | 32 | 2048 |

| 中断号约束 | 必须连续 | 可以随意分配 |

| 中断信息存放 | capbility寄存器 | MSI-X Table(bar空间) |

2.1 中断向量连续

如果一个PCIe设备需要使用8个中断请求时,如果使用MSI机制时,Message Data的[2:0]字段可以为0b000~0b111,因此可以发送8种中断请求,但是这8种中断请求的Message Data字段必须连续。在许多中断控制器中,Message Data字段连续也意味着中断控制器需要为这个PCIe设备分配8个连续的中断向量号。

有时在一个中断控制器中,虽然具有8个以上的中断向量号,但是很难保证这些中断向量号是连续的。因此中断控制器将无法为这些PCIe设备分配足够的中断请求,此时该设备的“Multiple Message Enable”字段将小于“Multiple Message Capable”。

2.2 映射区域区别

产生MSI中断的内存映射区在PCIE设备的配置空间,而产生MSIX中断的内存映射区在PCIE设备的BAR空间;

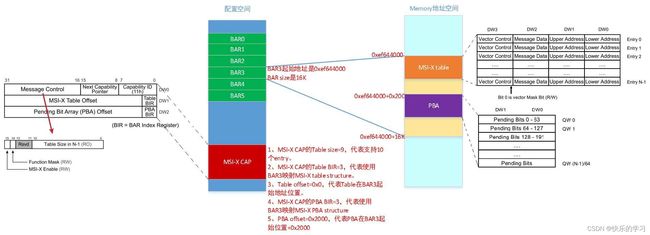

2.3 MSI-X配置空间

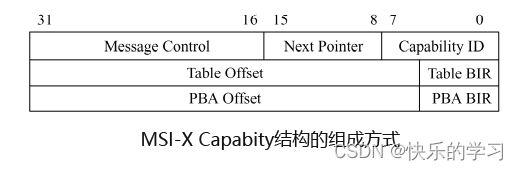

2.3.1 MSI-X Capbility介绍

Message Control:用来打开/关闭MSI/MSI-X功能,表示PCIe设备是否能够使用该Entry提交中断请求, 类似MSI的mask位。

Message Address & Data: 用来指定MSI/MSI-X中断对应的Message Address和Message。

2.3.2 Capbility ID介绍

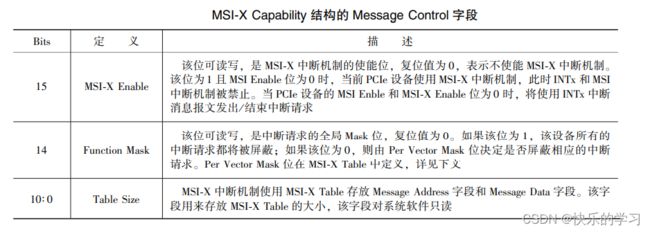

2.3.3 Message Control介绍

2.3.4 MSI-X Table介绍

Trigger Mode

中断触发方式控制寄存器:

2’b00: PCIe设备使用边沿触发方式申请中断

2’b10: PCIe设备使用低电平触发方式申请中断

2’b11: PCIe设备使用高电平触发方式申请中断

Vector

表示这个中断使用的中断向量,FSB Interrupt Message总线事务在提交中断请求的同时,也将中断向量提交给处理器,因此使用FSB Interrupt Meaasge总线事务时,处理器不需要使用中断响应周期通过读取中断控制器获取中断向量号。该方式的中断请求效率较高。

在x86处理器中,MSI机制使用的Message Data字段与MSI-X机制使用的Message Data字段相同。但是当一个PCIe设备支持多个MSI中断请求时,其Message Data字段必须是连续的,即其使用的vector字段是连续的,使用MSI-X机制有效的解决了该问题。

Delivery Mode

该字段标识着如何处理来自PCIe设备的中断请求

在x86处理器系统中,PCIe设备使用的Message Address字段仍保存PCI总线域的存储器地址,其格式为:

其中第31~20位存放FSB Interrupt存储器空间的基地址,其值为0xFEE。当PCIe设备对“0xFEEx_xxxx”这段“PCI域”的地址空间进行写操作时,MCH/ICH会首先进行“PCI总线域”到“存储器域”的地址转换,之后将这个写操作翻译为FSB总线的Interrupt Message总线事务,从而向CPU内核提交中断请求。

Destination ID

该字段保存目标CPU的ID号。

RH(Redirection Hint Indication)

该字段指示是否进行中断转发,当RH为0时,表示FSB Interrupt Message中断报文直接发向与Destination ID字段相同的CPU,为1时,将使能中断转发功能。

DM(Destination Mode)

该字段表示在传递优先权最低的中断请求时,Destination ID字段被翻译为Logical或者Physical APIC ID。

3、Vector Control

这个字段位于DWORD3,只使用了第0bit,作为vector的mask bit,若被置位,那么这个function将不能使用这个表项来发送MSI-X中断。然而,需要注意的是:如果其他表项也使用了相同的中断向量号,他们仍然能被用来发送中断消息。

2.3.5 MSI-X Pending Table(PBA)介绍

MSI-X中断机制还使用了独立的Pending Table表,该表用来存放与每一个中断向量对应的Pending位。这个Pending位的定义与MSI Capability寄存器的Pending位类似。MSI-X Table和Pending Table存放在PCIe设备的BAR空间中。MSI-X机制必须支持这个Pending Table,而MSI机制的Pending Bits字段是可选的。

三、MSI 处理过程

3.1 Message处理

根据PCIe规范的定义,MSI/MSI-X中断请求发生时,PCIe设备会实际产生1个Memory Write Transaction。它对应的数据封包为Memory Write类型的Trasaction Layer Packet(TLP),其格式如下图所示(对MSI-X也同样适用)。其中目标Memory Address称为“Message Address”,要写入该内存地址的数据称为“Message Data”。这两个字段都来自MSI/MSI-X Capability Structure中的设定,系统软件在Enable并初始化MSI/MSI-X的过程中必须要预先设置好它们。

3.2 详细过程

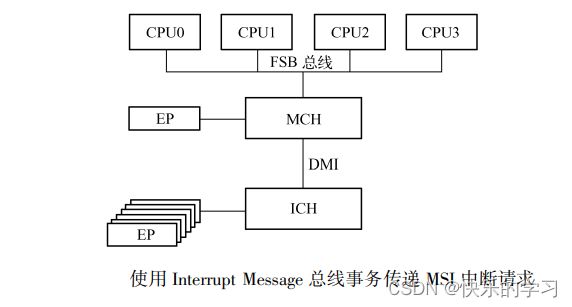

1、PCIe 设备在发送 MSI / MSI⁃X 中断请求之前, 系统软件需要合理设置 PCIe 设备 MSI / MSI⁃ X Capability 寄存器, 使 Message Address 寄存器的值为 0xFEExx00y, 同时合理地设置 Message Data 寄存器 Vector 字段。其中 xx 表示 APIC ID, 而 y 为 RH + DM。

2、PCIe 设备提交 MSI / MSI⁃X 中断请求时, 需要向 0xFEExx00y 地址写 Message Data 寄存器 中包含的数据, 并以存储器写 TLP 的形式发送到 RC。

3、如果 ICH 收到这个存储器写 TLP 时, 将通过 DMI 接口将这个 TLP 提交到 MCH。 MCH 收到这个 TLP 后, 发现这个 TLP 的目的地址在 FSB Interrupts 存储器空间中, 则将 PCIe 总线的存储器写请求转换为 Interrupt Message 总 线事务, 并在 FSB 总线上广播。

4、FSB 总线上的 CPU, 根据 APIC ID 信息, 选择是否接收这个 Interrupt Message 总线事务, 并进入中断状态, 之后该 CPU将直接从这个总线事务中获得中断向量号, 执行相应的中断服务例程, 而不需要从APIC中断控制器获得中断向量。

四、MSI⁃X 中断处理请求过程

PCIe 设备发出 MSI⁃X 中断请求的方法与发出MSI中断请求的方法类似, 都是向Message Address所在的地址写Message Data字段包含的数据。 只是MSI⁃X中断机制为了支持更多的 中断请求, 在 MSI⁃X Capablity结构中存放了一个指向一组Message Address和Message Data字段的指针, 从而一个PCIe设备可以支持的MSI⁃X中断请求数目大于 32 个, 而且并不要求 中断向量号连续。 MSI⁃X 机制使用的这组Message Address和Message Data字段存放在 PCIe 设备的BAR空间中, 而不是在 PCIe 设备的配置空间中, 从而可以由用户决定使用 MSI⁃X中断请求的数目。

x86处理器使用FSB的Interrupt Message总线事务处理 PCIe 设备的MSI / MSI⁃X中断请求。

五、INTx中断介绍

PCI总线使用INTA#、INTB#、INTC#和INTD#信号向处理器发出中断请求。这些中断请求信号为低电平有效,并与处理器的中断控制器连接。在PCI体系结构中,这些中断信号属于边带信号(Sideband Signals),PCI总线规范并没有明确规定在一个处理器系统中如何使用这些信号,因为这些信号对于PCI总线是可选信号。所谓边带信号是指这些信号在PCI总线中是可选信号,而且只能在一个处理器系统的内部使用,并不能离开这个处理器环境。

5.1 PCI INTx中断流程

一个简单的PCI总线INTx中断实现流程,如下图所示(单核CPU)。

1、首先,PCI设备通过INTx边带信号产生中断请求,经过中断控制器(Interrupt Controller,PIC)后,转换为INTR信号,并直接发送至CPU;

2、CPU收到INTR信号置位后,意识到了中断请求的发生,但是此时并不知道是什么中断请求。于是通过一个特殊的指令来查询中断请求信息,该过程一般被称为中断应答(Interrupt Acknowledge);

3、该特殊指令被发送至PIC后,PIC会返回一个8bits的中断向量(Interrupt Vector)值给CPU。该中断向量值与其发送的INTR请求是对应的;

4、CPU收到来自PIC的中断向量值后,会去其Memory中的中断向量表(Interrupt Table)中查找对应的中断服务程序(Interrupt Service Routines,ISR)在Memory的位置;

5、然后CPU读取ISR程序,进而处理该中断。